382c21f0e73989244674d3bcb2bd63cc.ppt

- Количество слайдов: 81

저전력 통신 So. C 설계 조 준 동 VADA Lab. Sung. Kyun. Kwan University 2006. 8 성균관대학교 정보통신공학부 © 조준동 2006년 여름 1

발표순서 • 저전력 So. C 설계 기초 – Power metric – 기본적인 저전력 설계 기술 • 재구성구조를 이용한 저전력 설계 – Reconfigurable Radio Systems (Software Defined Radio) • 병렬처리를 통한 저전력 설계 – Network-centric Design – Reliable Design • Deep submicron Clock and Power 관리 기법 © 조준동, 2006년 여름 2

저전력 설계 기초 성균관대학교 정보통신공학부 © 조준동 2006년 여름 3

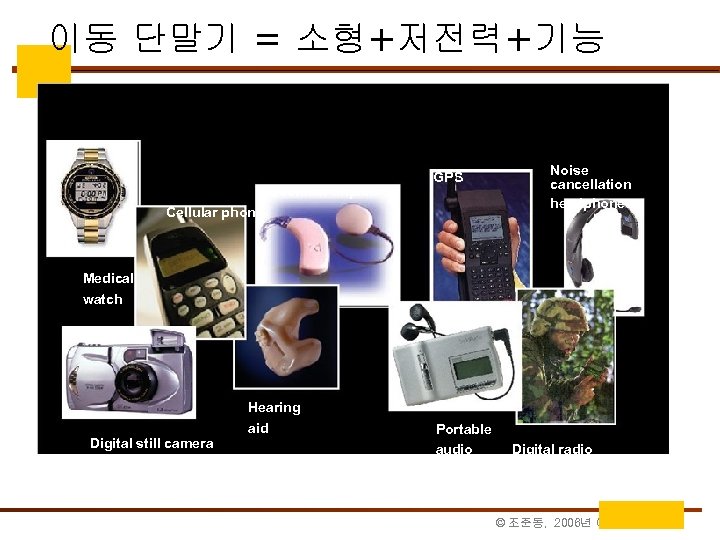

이동 단말기 = 소형+저전력+기능 Cochlear implant GPS Cellular phone Noise cancellation headphones Medical watch Digital still camera Hearing aid Portable audio Digital radio © 조준동, 2006년 여름 4

미래의 모바일 컴퓨팅 • 실시간 처리 이동 슈퍼 컴퓨팅 – Speech recognition, Cryptography. – Augmented reality. • 16개의 Pentium-4 필요 – 2004 Intel P 4 @3 GHz; 55 M TR’s 122 mm 2 0. 09 u – 2014 20 GHz 0. 03 u • 저전력을 만족하면서 고성능 – requires (massive) parallelism – Multi-processor systems – Subsystem integration Mudge et al: © 조준동, 2006년 여름 5

저전력 디바이스의 필요성 • 실용적 (Reducing power requirements of high throughput portable applications) • 경제적 (Reducing packaging costs and achieving memory savings) • 기술적 (Excessive heat prevents the realization of high density chips and limits their functionalities) © 조준동, 2006년 여름 6

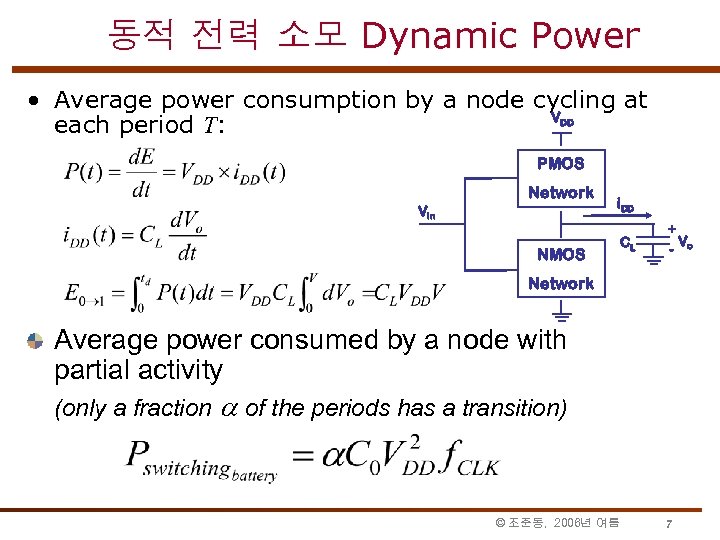

동적 전력 소모 Dynamic Power • Average power consumption by a node cycling at V each period T: DD PMOS Network Vin i. DD NMOS CL + V - o Network Average power consumed by a node with partial activity (only a fraction of the periods has a transition) © 조준동, 2006년 여름 7

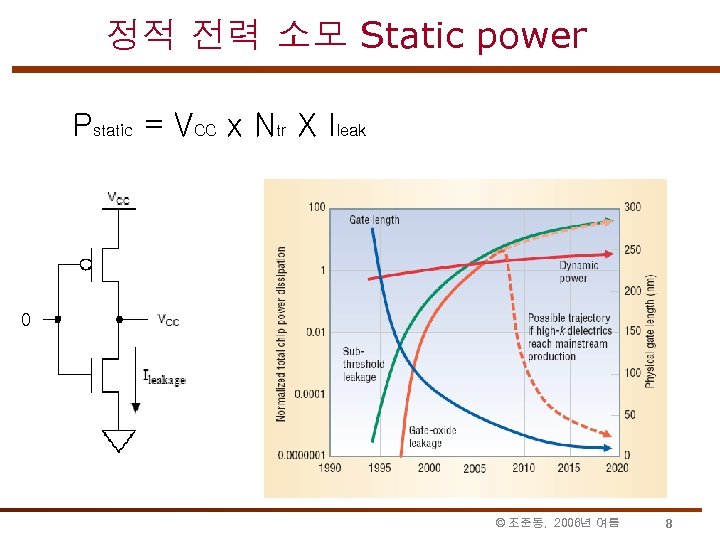

정적 전력 소모 Static power Pstatic = VCC x Ntr X Ileak 0 © 조준동, 2006년 여름 8

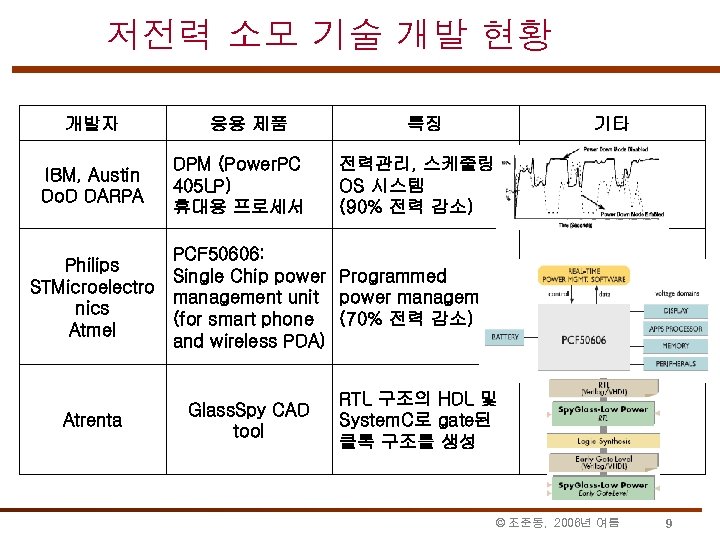

저전력 소모 기술 개발 현황 개발자 IBM, Austin Do. D DARPA 응용 제품 DPM (Power. PC 405 LP) 휴대용 프로세서 특징 기타 전력관리, 스케줄링, OS 시스템 (90% 전력 감소) PCF 50606: Philips Single Chip power Programmed STMicroelectro management unit power management nics (for smart phone (70% 전력 감소) Atmel and wireless PDA) Atrenta Glass. Spy CAD tool RTL 구조의 HDL 및 System. C로 gate된 클록 구조를 생성 © 조준동, 2006년 여름 9

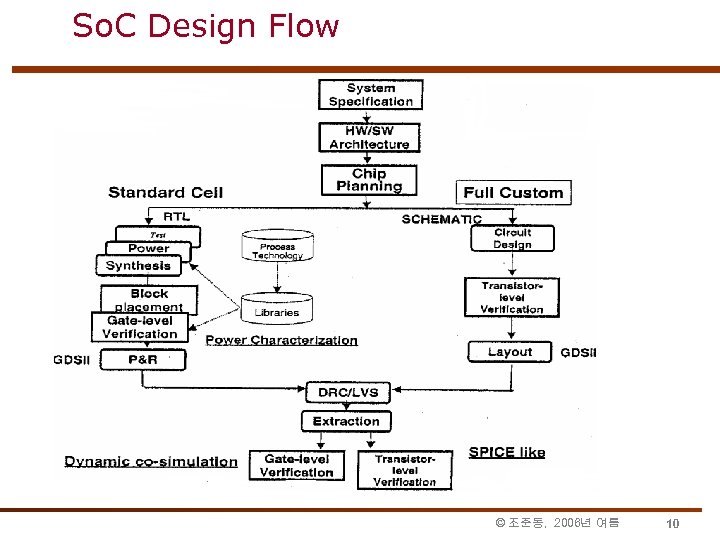

So. C Design Flow © 조준동, 2006년 여름 10

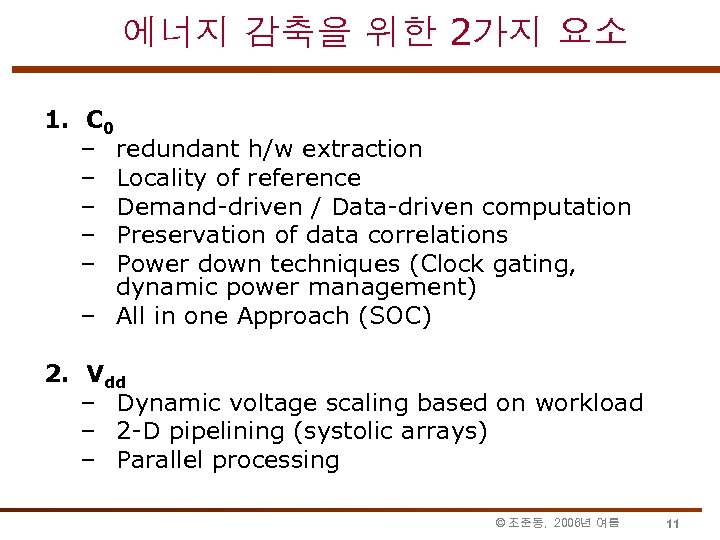

에너지 감축을 위한 2가지 요소 1. C 0 – redundant h/w extraction – Locality of reference – Demand-driven / Data-driven computation – Preservation of data correlations – Power down techniques (Clock gating, dynamic power management) – All in one Approach (SOC) 2. Vdd – Dynamic voltage scaling based on workload – 2 -D pipelining (systolic arrays) – Parallel processing © 조준동, 2006년 여름 11

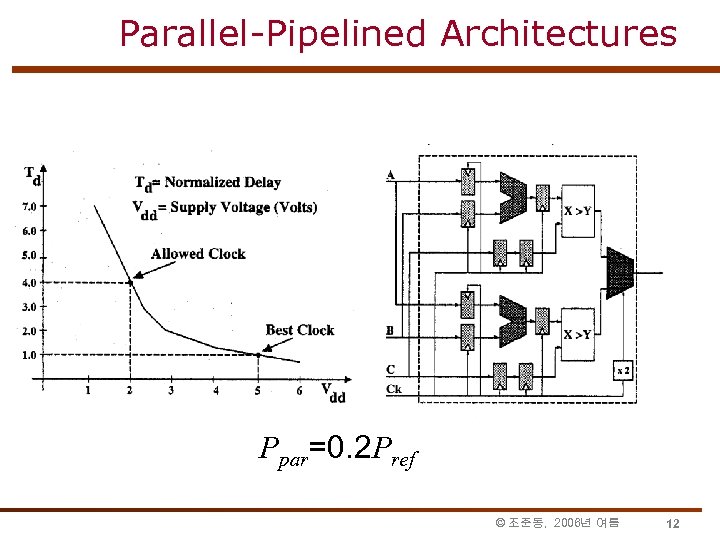

Parallel-Pipelined Architectures Ppar=0. 2 Pref © 조준동, 2006년 여름 12

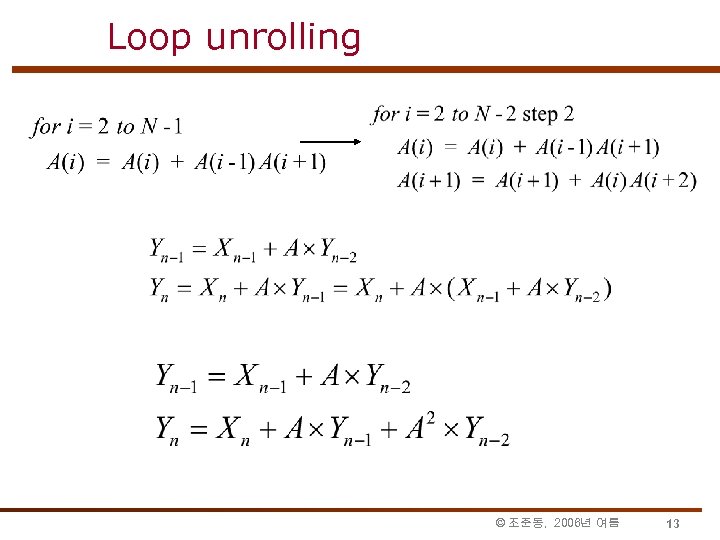

Loop unrolling © 조준동, 2006년 여름 13

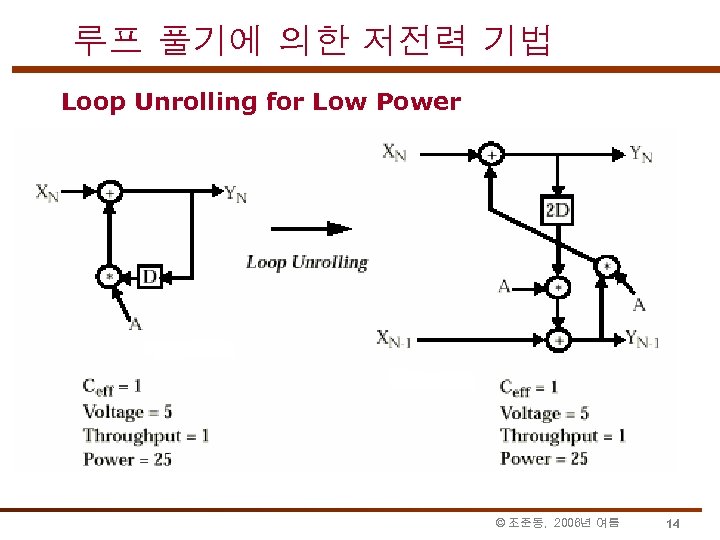

루프 풀기에 의한 저전력 기법 Loop Unrolling for Low Power © 조준동, 2006년 여름 14

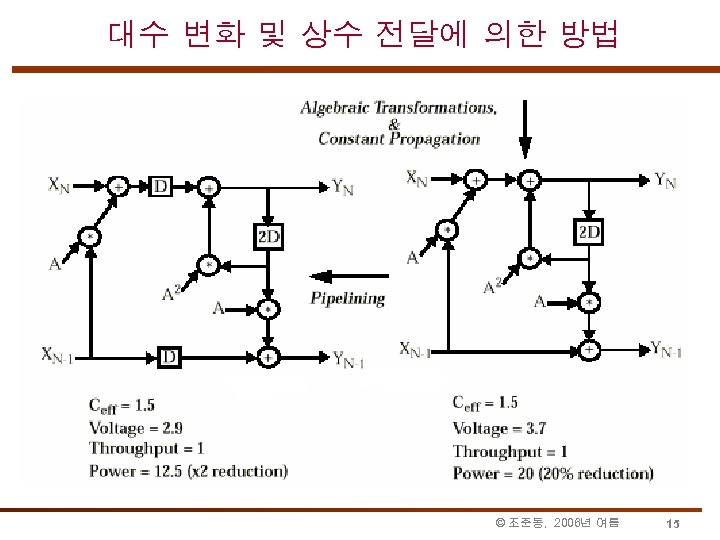

대수 변화 및 상수 전달에 의한 방법 © 조준동, 2006년 여름 15

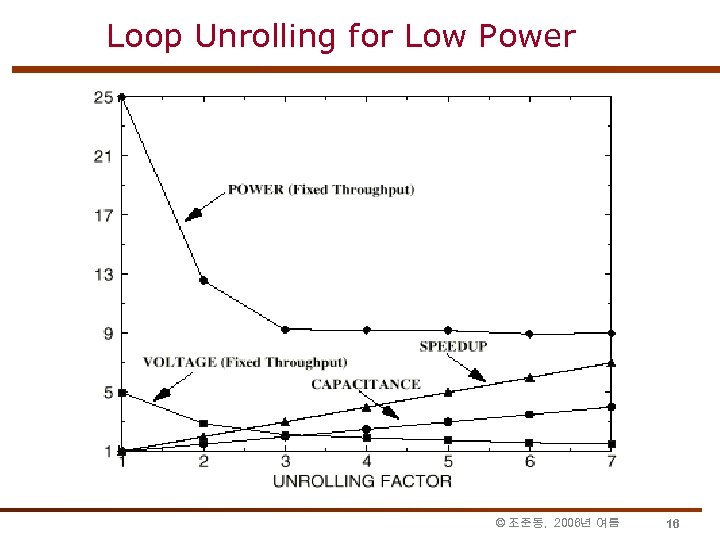

Loop Unrolling for Low Power © 조준동, 2006년 여름 16

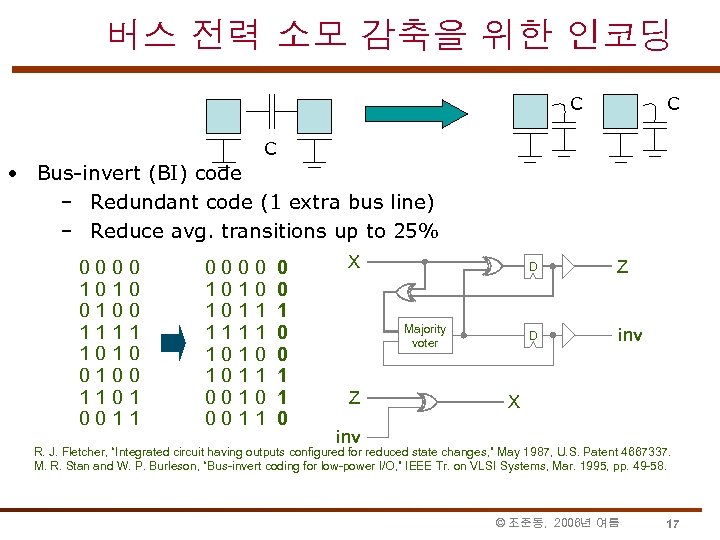

버스 전력 소모 감축을 위한 인코딩 C C C • Bus-invert (BI) code – Redundant code (1 extra bus line) – Reduce avg. transitions up to 25% 0000 1010 0100 1111 1010 0100 1101 0011 0000 1011 1111 1010 1011 0010 0011 0 0 1 1 0 X D D Majority voter Z Z inv X inv R. J. Fletcher, “Integrated circuit having outputs configured for reduced state changes, ” May 1987, U. S. Patent 4667337. M. R. Stan and W. P. Burleson, “Bus-invert coding for low-power I/O, ” IEEE Tr. on VLSI Systems, Mar. 1995, pp. 49 -58. © 조준동, 2006년 여름 17

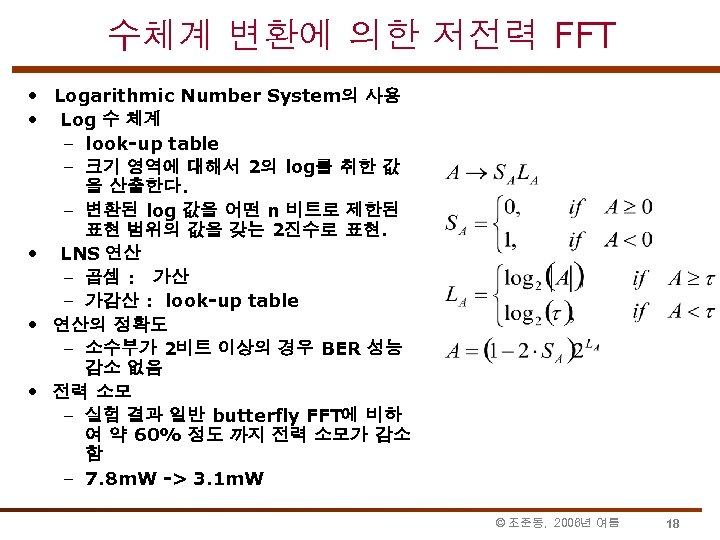

수체계 변환에 의한 저전력 FFT • Logarithmic Number System의 사용 • Log 수 체계 – look-up table – 크기 영역에 대해서 2의 log를 취한 값 을 산출한다. – 변환된 log 값을 어떤 n 비트로 제한된 표현 범위의 값을 갖는 2진수로 표현. • LNS 연산 – 곱셈 : 가산 – 가감산 : look-up table • 연산의 정확도 – 소수부가 2비트 이상의 경우 BER 성능 감소 없음 • 전력 소모 – 실험 결과 일반 butterfly FFT에 비하 여 약 60% 정도 까지 전력 소모가 감소 함 – 7. 8 m. W -> 3. 1 m. W © 조준동, 2006년 여름 18

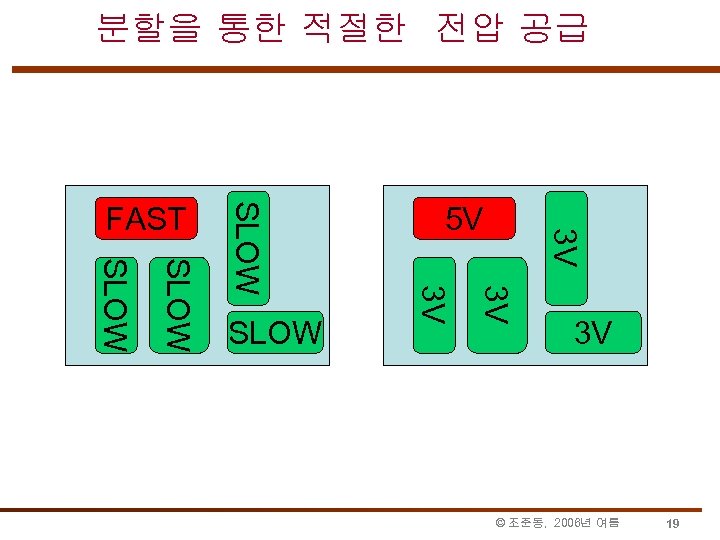

분할을 통한 적절한 전압 공급 3 V 3 V SLOW 5 V 3 V SLOW FAST 3 V © 조준동, 2006년 여름 19

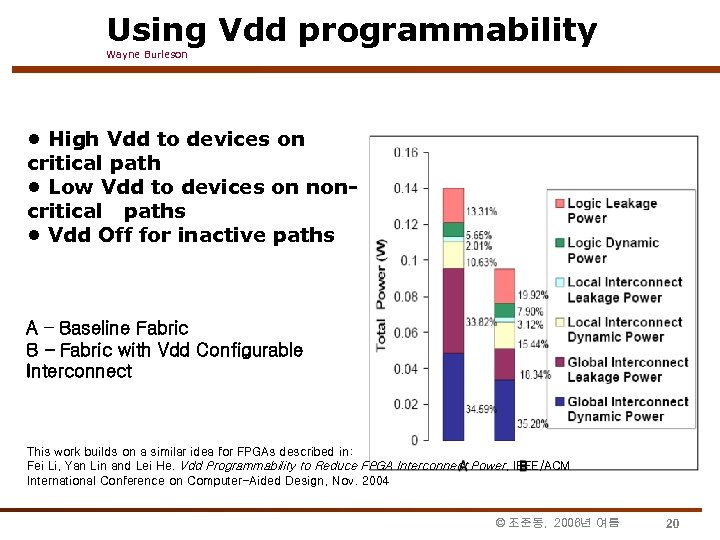

Using Vdd programmability Wayne Burleson • High Vdd to devices on critical path • Low Vdd to devices on noncritical paths • Vdd Off for inactive paths A – Baseline Fabric B – Fabric with Vdd Configurable Interconnect This work builds on a similar idea for FPGAs described in: Fei Li, Yan Lin and Lei He. Vdd Programmability to Reduce FPGA Interconnect Power, IEEE/ACM International Conference on Computer-Aided Design, Nov. 2004 © 조준동, 2006년 여름 20

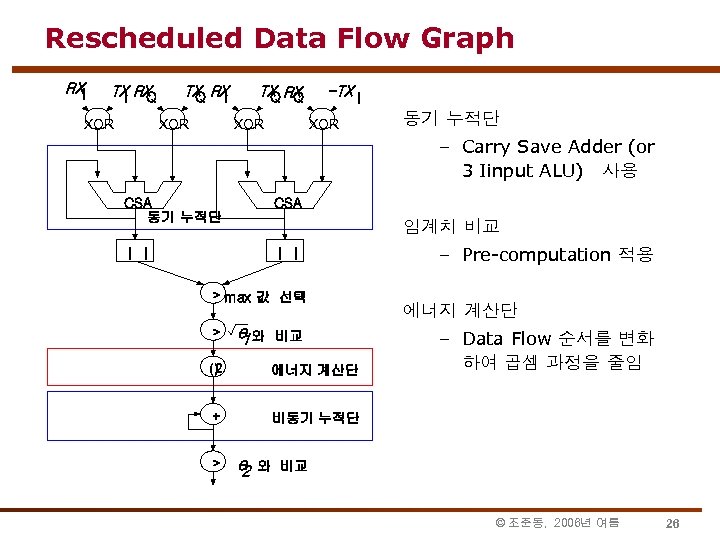

저전력 CDMA 탐색자 ü CDMA 단말기용 MSM (Mobile Station Modem) 칩 의 Searcher Engine에 대한 RTL수준 저전력 설계 구 현. 동작 주파수 : 12. 5 MHz ü Data flow graph를 사용하여 rescheduling, precomputation 및 strength reduction, Synchronous Accumulator를 이용한 저전력 설계, area와 power를 각각 최대 67. 68%, 41. 35% 감소 시킴. San Kim and Jun-Dong Cho, “Low Power CDMA Searcher”, CAD and VLSI Workshop, May. 1999. © 조준동, 2006년 여름 21

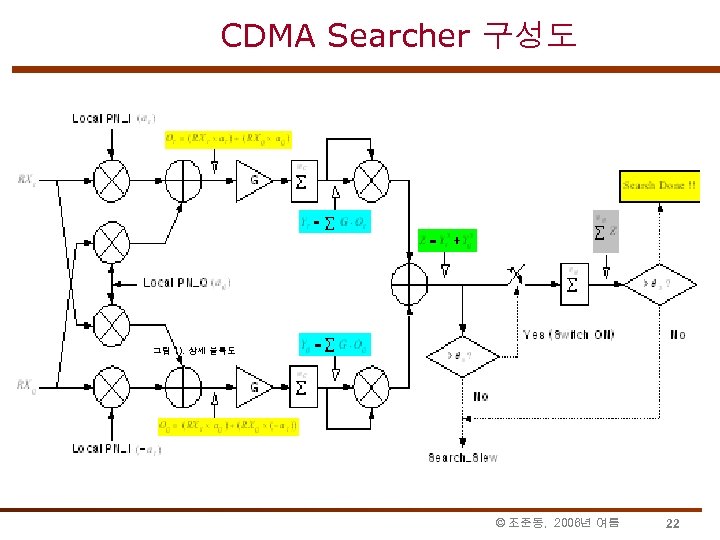

CDMA Searcher 구성도 그림 1). 상세 블록도 © 조준동, 2006년 여름 22

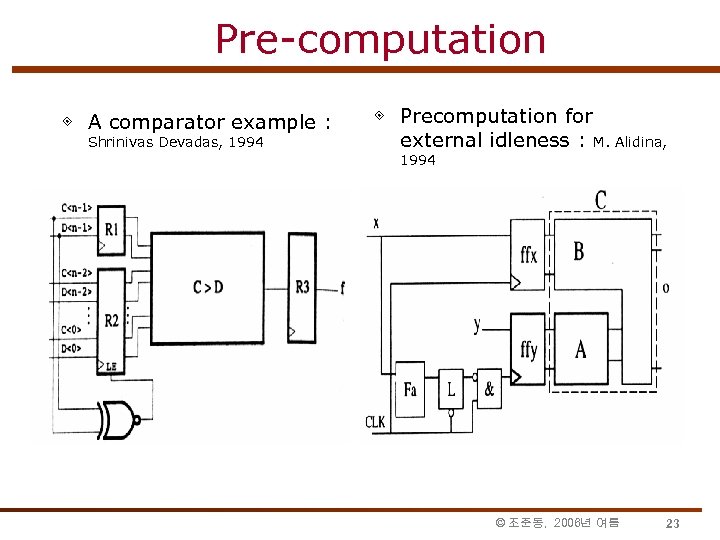

Pre-computation ◈ A comparator example : Shrinivas Devadas, 1994 ◈ Precomputation for external idleness : M. Alidina, 1994 © 조준동, 2006년 여름 23

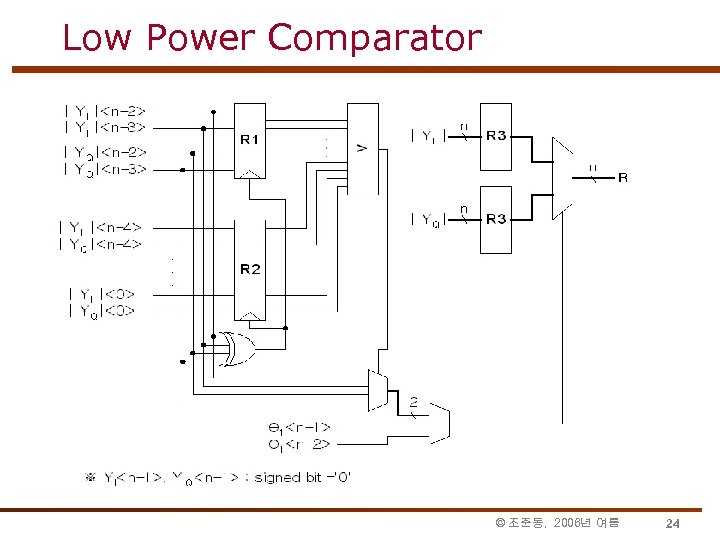

Low Power Comparator © 조준동, 2006년 여름 24

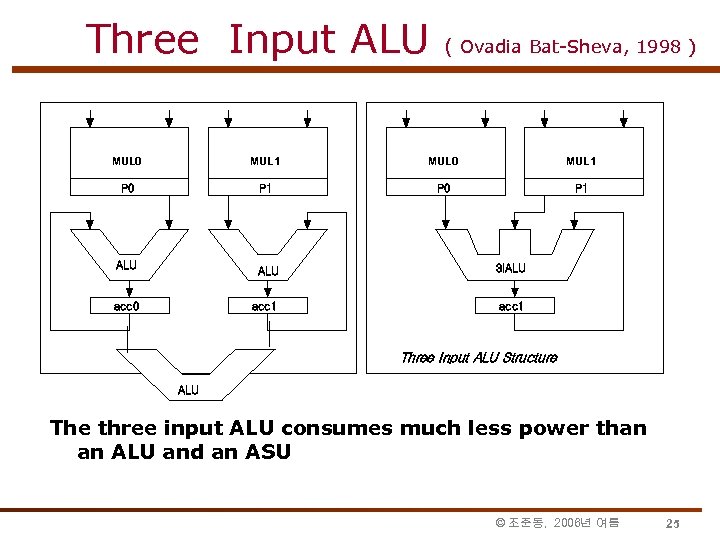

Three Input ALU ( Ovadia Bat-Sheva, 1998 ) MUL 0 MUL 1 P 0 P 1 ALU acc 1 acc 0 3 IALU acc 1 Three Input ALU Structure ALU The three input ALU consumes much less power than an ALU and an ASU © 조준동, 2006년 여름 25

Rescheduled Data Flow Graph RXI TX RX I Q XOR TX RX Q I XOR TX RX Q Q XOR -TX I XOR 동기 누적단 – Carry Save Adder (or 3 Iinput ALU) 사용 CSA 동기 누적단 CSA | | 임계치 비교 > max 값 선택 > θ 와 비교 1 2 () 에너지 계산단 + – Pre-computation 적용 에너지 계산단 – Data Flow 순서를 변화 하여 곱셈 과정을 줄임 비동기 누적단 > θ 와 비교 2 © 조준동, 2006년 여름 26

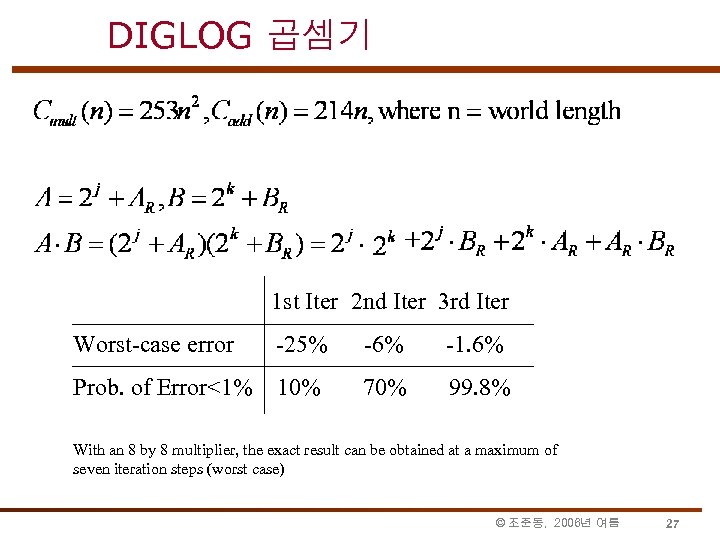

DIGLOG 곱셈기 1 st Iter 2 nd Iter 3 rd Iter Worst-case error -25% -6% -1. 6% Prob. of Error<1% 10% 70% 99. 8% With an 8 by 8 multiplier, the exact result can be obtained at a maximum of seven iteration steps (worst case) © 조준동, 2006년 여름 27

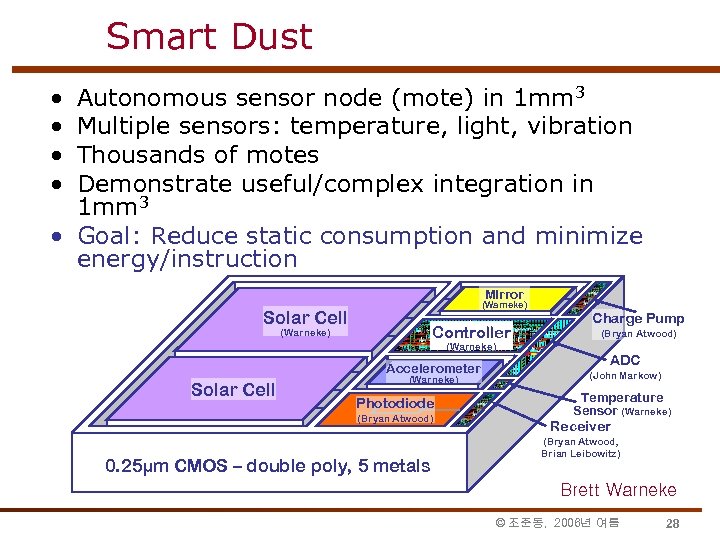

Smart Dust • • Autonomous sensor node (mote) in 1 mm 3 Multiple sensors: temperature, light, vibration Thousands of motes Demonstrate useful/complex integration in 1 mm 3 • Goal: Reduce static consumption and minimize energy/instruction Mirror (Warneke) Solar Cell Controller (Warneke) Charge Pump (Bryan Atwood) (Warneke) Accelerometer Solar Cell (Warneke) Photodiode (Bryan Atwood) 0. 25µm CMOS – double poly, 5 metals ADC (John Markow) Temperature Sensor (Warneke) Receiver (Bryan Atwood, Brian Leibowitz) Brett Warneke © 조준동, 2006년 여름 28

스마트 더스트를 위한 저전력 설계 • System integration and miniaturization • Low-energy microcontroller – Goals • < 0. 1 p. J/instruction/bit • < 10 n. W leakage • 1 -100 k. Hz operation – Sequencing and clock gating – Reconfigurable datapath components – Data-driven operation – Element-level power cycling © 조준동, 2006년 여름 29

Power Cycling 1. Rest mode – Processor is powered down, while I/O devices remain on 2. Sleep mode – Both processor and peripherals are powered off. I/O ports, disk ports, display, and sound circuits – RAM and power-management IC remain on. 3. Shutdown mode – The entire computer including the powermanagement IC is powered down. – Only a tiny amount of power is drawn for RAM. © 조준동, 2006년 여름 30

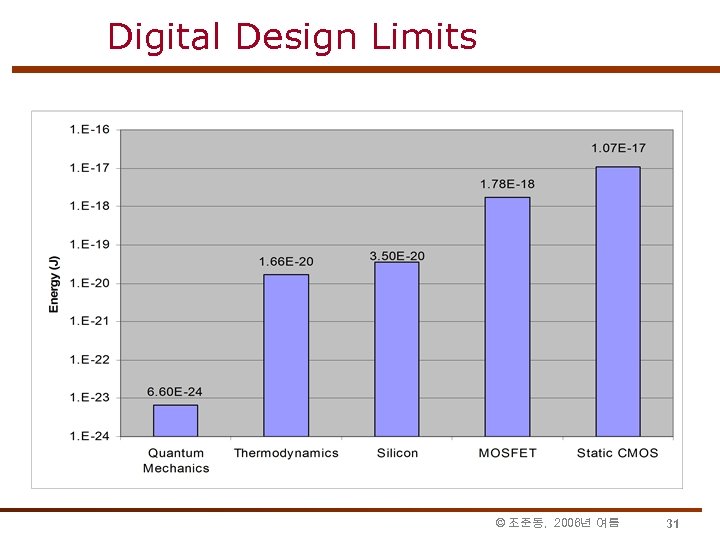

Digital Design Limits © 조준동, 2006년 여름 31

재구성구조를 이용한 저전력 설계 성균관대학교 정보통신공학부 © 조준동 2006년 여름 32

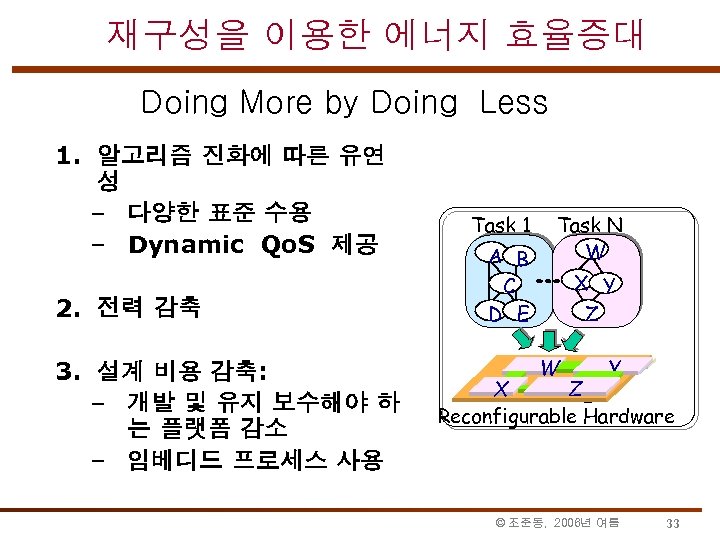

재구성을 이용한 에너지 효율증대 Doing More by Doing Less 1. 알고리즘 진화에 따른 유연 성 – 다양한 표준 수용 – Dynamic Qo. S 제공 2. 전력 감축 3. 설계 비용 감축: – 개발 및 유지 보수해야 하 는 플랫폼 감소 – 임베디드 프로세스 사용 Task 1 A B C D E Task N W X Y Z A W Y B I J X D C ZE Reconfigurable Hardware H © 조준동, 2006년 여름 33

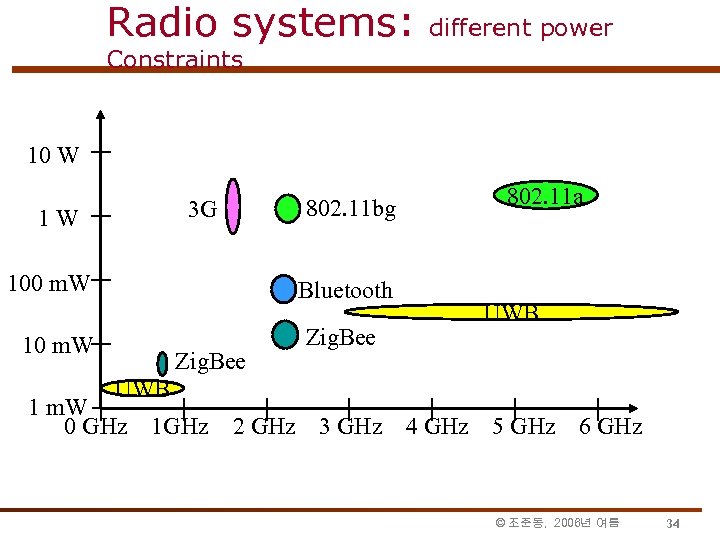

Radio systems: different power Constraints 10 W 3 G 1 W 100 m. W 802. 11 bg Bluetooth 10 m. W Zig. Bee 802. 11 a UWB 1 m. W 0 GHz 1 GHz 2 GHz 3 GHz 4 GHz 5 GHz 6 GHz © 조준동, 2006년 여름 34

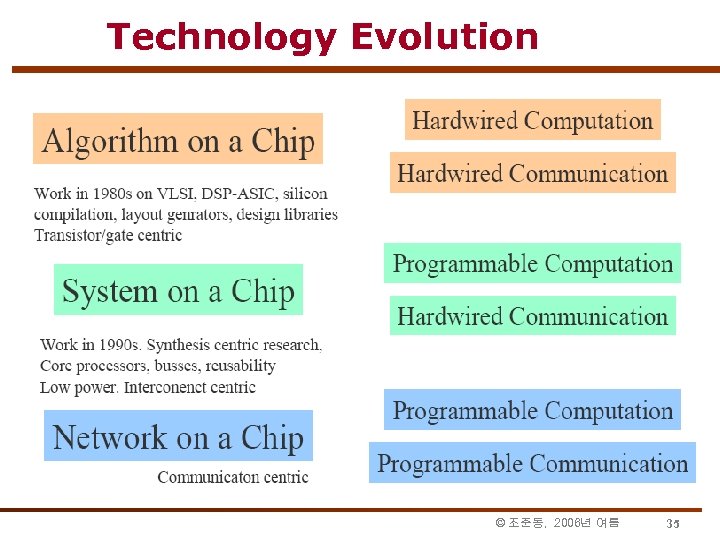

Technology Evolution © 조준동, 2006년 여름 35

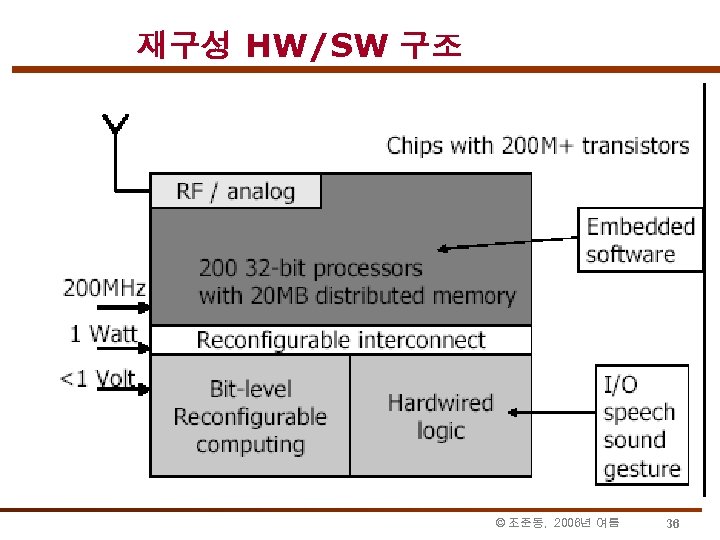

재구성 HW/SW 구조 © 조준동, 2006년 여름 36

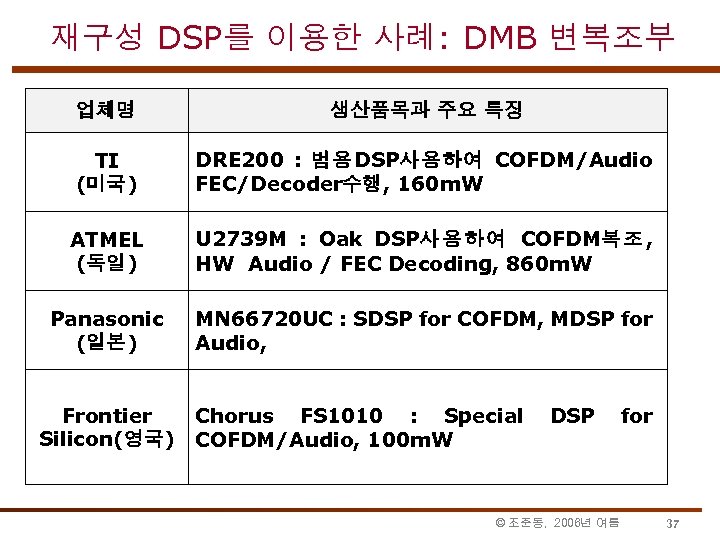

재구성 DSP를 이용한 사례: DMB 변복조부 업체명 생산품목과 주요 특징 TI (미국) DRE 200 : 범용DSP사용하여 COFDM/Audio FEC/Decoder수행, 160 m. W ATMEL (독일) U 2739 M : Oak DSP사 용 하 여 COFDM복 조 , HW Audio / FEC Decoding, 860 m. W Panasonic (일본) MN 66720 UC : SDSP for COFDM, MDSP for Audio, Frontier Silicon(영국) Chorus FS 1010 : Special DSP for COFDM/Audio, 100 m. W © 조준동, 2006년 여름 37

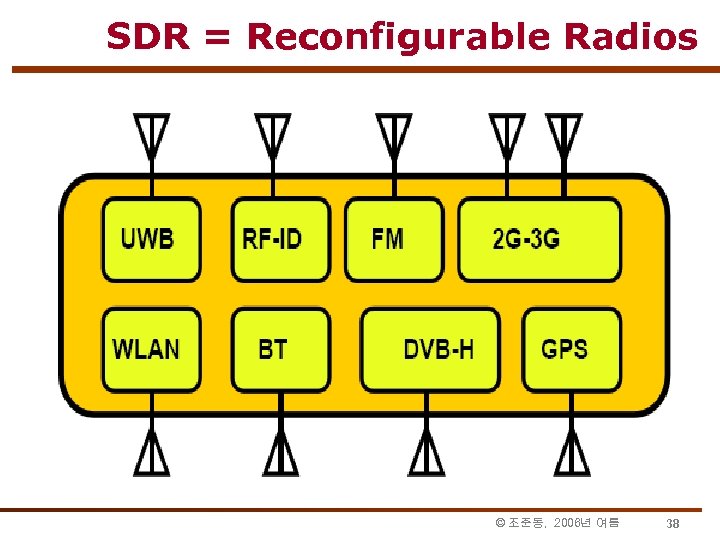

SDR = Reconfigurable Radios © 조준동, 2006년 여름 38

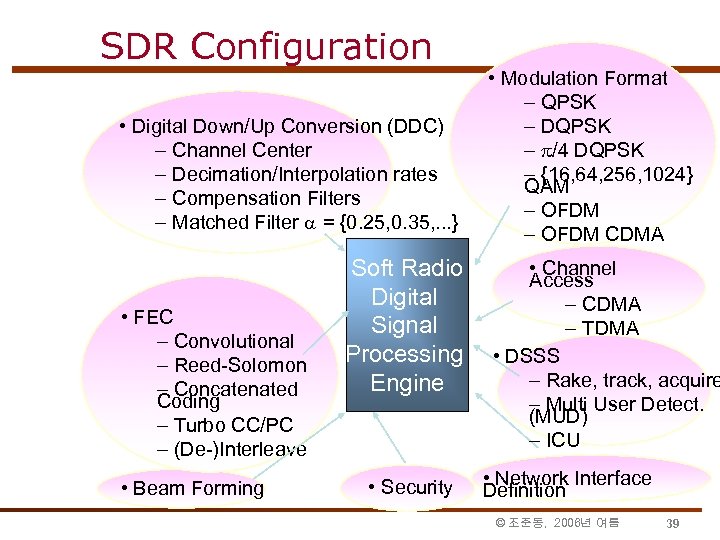

SDR Configuration • Digital Down/Up Conversion (DDC) – Channel Center – Decimation/Interpolation rates – Compensation Filters – Matched Filter a = {0. 25, 0. 35, . . . } • FEC – Convolutional – Reed-Solomon – Concatenated Coding – Turbo CC/PC – (De-)Interleave • Beam Forming Soft Radio Digital Signal Processing Engine • Security • Modulation Format – QPSK – DQPSK – p/4 DQPSK – {16, 64, 256, 1024} QAM – OFDM CDMA • Channel Access – CDMA – TDMA • DSSS – Rake, track, acquire – Multi User Detect. (MUD) – ICU • Network Interface Definition © 조준동, 2006년 여름 39

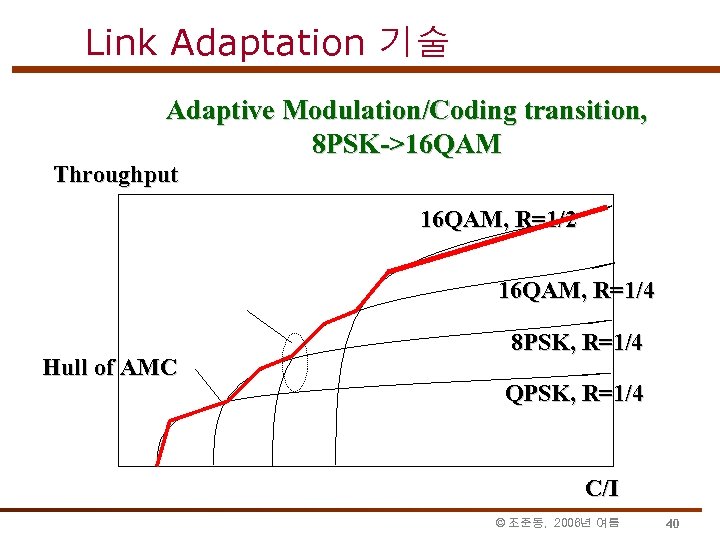

Link Adaptation 기술 Adaptive Modulation/Coding transition, 8 PSK->16 QAM Throughput 16 QAM, R=1/2 16 QAM, R=1/4 Hull of AMC 8 PSK, R=1/4 QPSK, R=1/4 C/I © 조준동, 2006년 여름 40

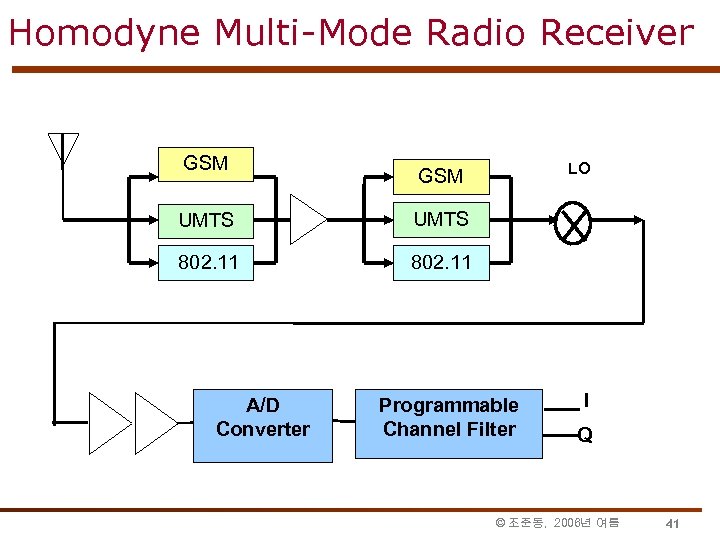

Homodyne Multi-Mode Radio Receiver GSM LO GSM UMTS 802. 11 A/D Converter Programmable Channel Filter I Q © 조준동, 2006년 여름 41

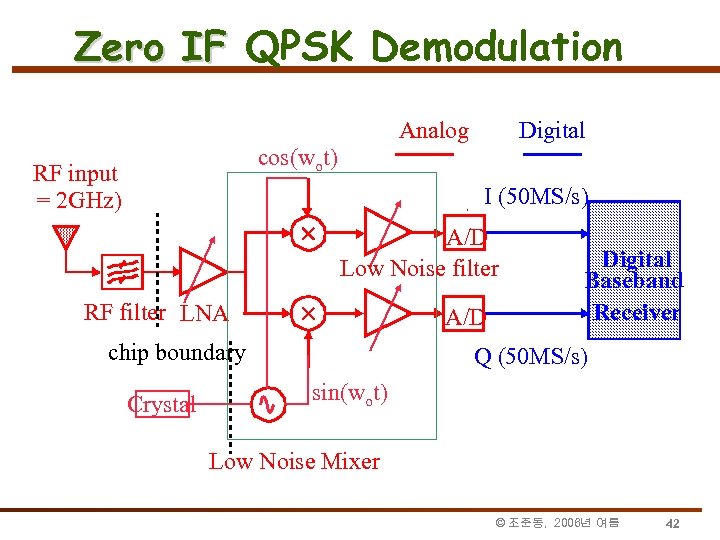

Zero IF QPSK Demodulation Analog Digital cos(wot) RF input = 2 GHz) I (50 MS/s) A/D Low Noise filter RF filter LNA A/D chip boundary Crystal Digital Baseband Receiver Q (50 MS/s) sin(wot) Low Noise Mixer © 조준동, 2006년 여름 42

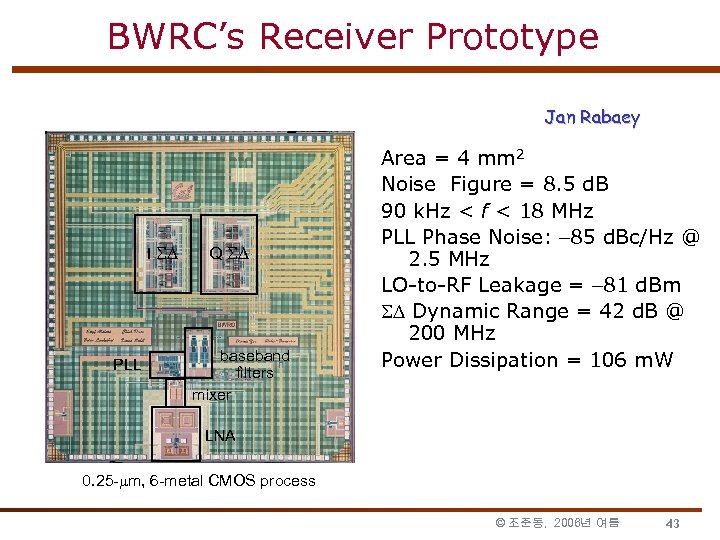

BWRC’s Receiver Prototype Jan Rabaey I SD PLL Q SD baseband filters mixer Area = 4 mm 2 Noise Figure = 8. 5 d. B 90 k. Hz < f < 18 MHz PLL Phase Noise: -85 d. Bc/Hz @ 2. 5 MHz LO-to-RF Leakage = -81 d. Bm SD Dynamic Range = 42 d. B @ 200 MHz Power Dissipation = 106 m. W LNA 0. 25 -mm, 6 -metal CMOS process © 조준동, 2006년 여름 43

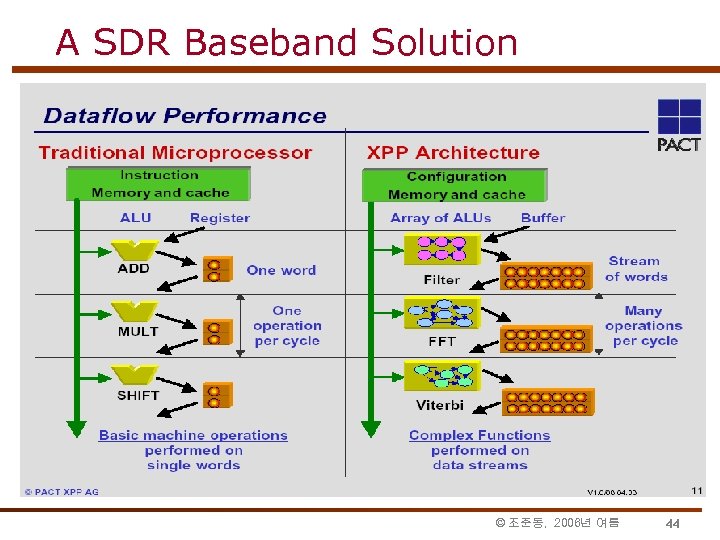

A SDR Baseband Solution © 조준동, 2006년 여름 44

재구성 Video Encoding • Motion Estimation: Most Computationally demanding part of Video Encoding • Example: CCIR 601 format • 720 by 576 pixel • 16 by 16 macro block (n = 16) • 32 by 32 search area (p = 8) • 25 Hz Frame rate (f frame = 25) • 9 Giga Operations/Sec is needed for Full Search Block Matching Algorithm. © 조준동, 2006년 여름 45

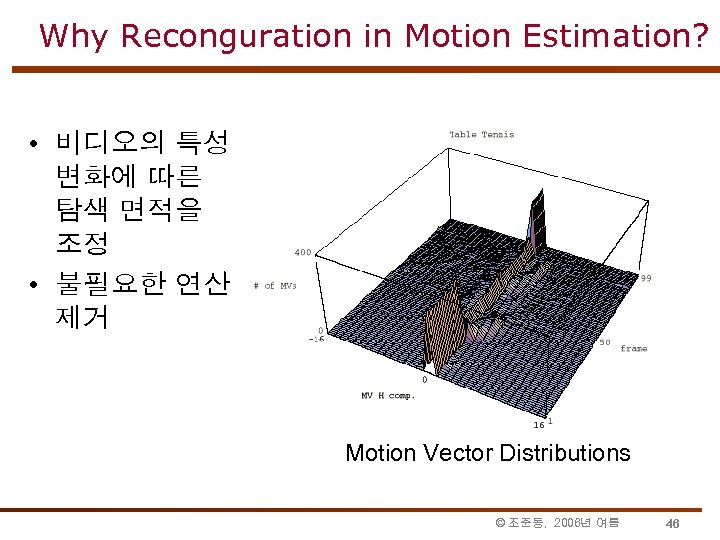

Why Reconguration in Motion Estimation? • 비디오의 특성 변화에 따른 탐색 면적을 조정 • 불필요한 연산 제거 Motion Vector Distributions © 조준동, 2006년 여름 46

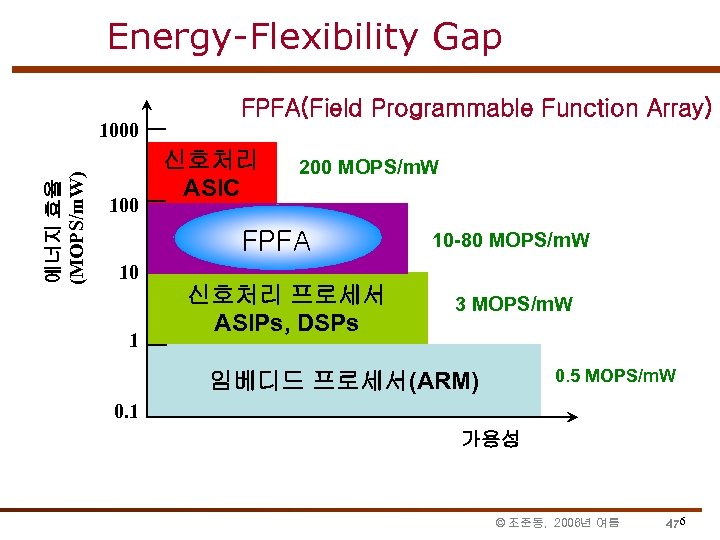

Energy-Flexibility Gap 에너지 효율 (MOPS/m. W) 1000 100 FPFA(Field Programmable Function Array) 신호처리 ASIC 200 MOPS/m. W FPFA 10 1 신호처리 프로세서 ASIPs, DSPs 10 -80 MOPS/m. W 3 MOPS/m. W 0. 5 MOPS/m. W 임베디드 프로세서(ARM) 0. 1 가용성 © 조준동, 2006년 여름 476

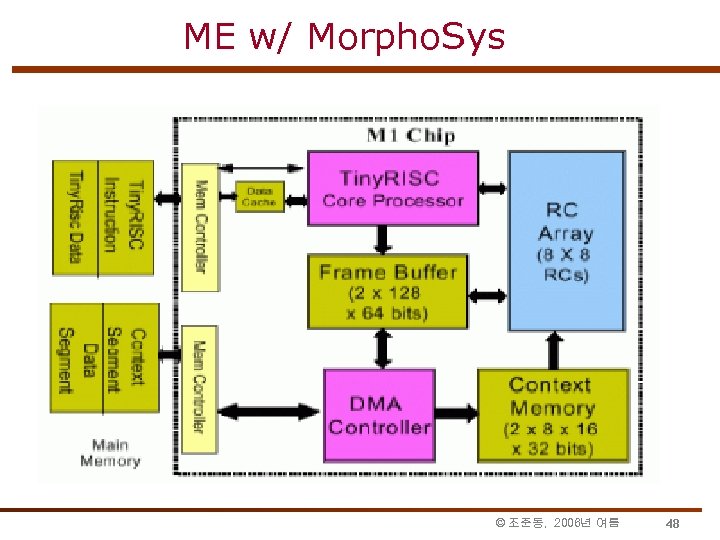

ME w/ Morpho. Sys © 조준동, 2006년 여름 48

Reconfigurable cell © 조준동, 2006년 여름 49

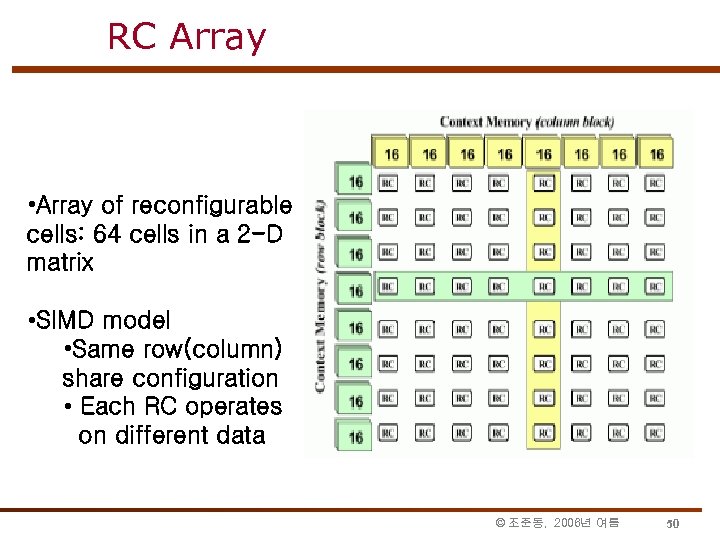

RC Array • Array of reconfigurable cells: 64 cells in a 2 -D matrix • SIMD model • Same row(column) share configuration • Each RC operates on different data © 조준동, 2006년 여름 50

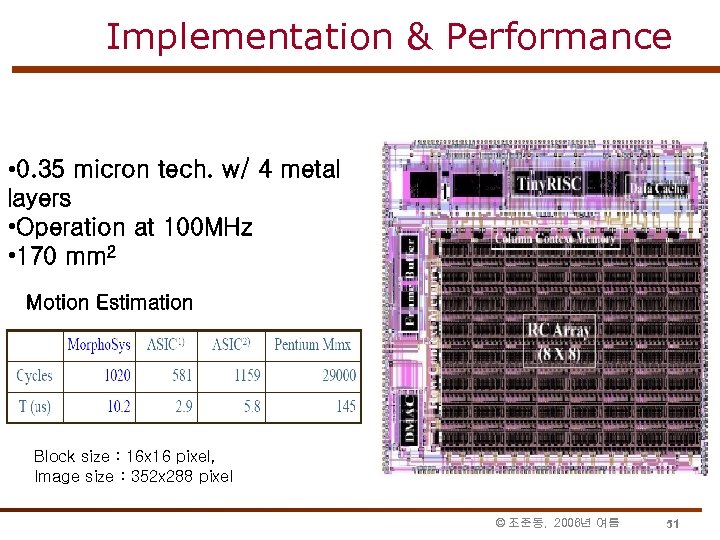

Implementation & Performance • 0. 35 micron tech. w/ 4 metal layers • Operation at 100 MHz • 170 mm 2 Motion Estimation Block size : 16 x 16 pixel, Image size : 352 x 288 pixel © 조준동, 2006년 여름 51

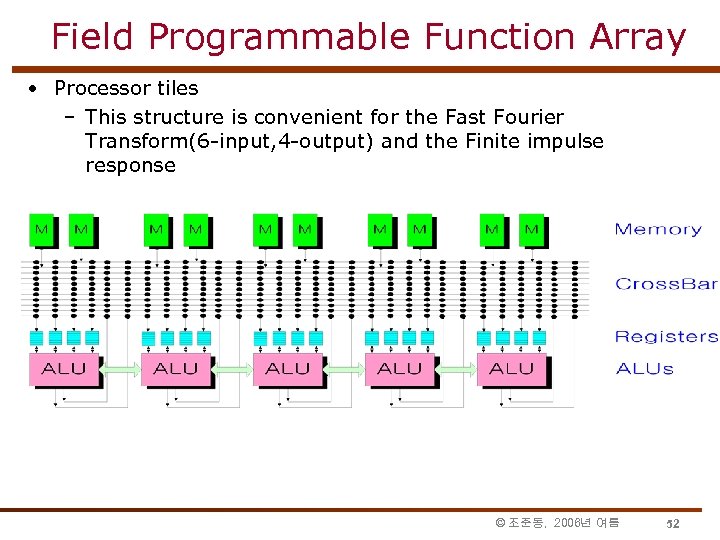

Field Programmable Function Array • Processor tiles – This structure is convenient for the Fast Fourier Transform(6 -input, 4 -output) and the Finite impulse response © 조준동, 2006년 여름 52

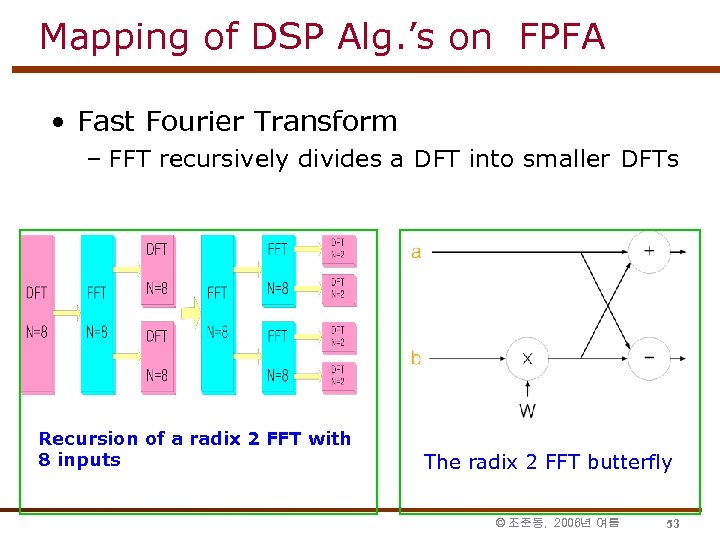

Mapping of DSP Alg. ’s on FPFA • Fast Fourier Transform – FFT recursively divides a DFT into smaller DFTs Recursion of a radix 2 FFT with 8 inputs The radix 2 FFT butterfly © 조준동, 2006년 여름 53

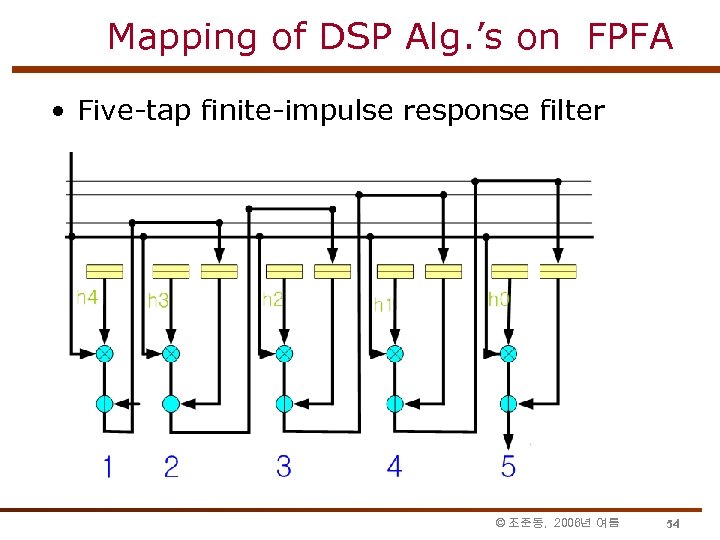

Mapping of DSP Alg. ’s on FPFA • Five-tap finite-impulse response filter © 조준동, 2006년 여름 54

병렬처리를 이용한 저전력 설계 성균관대학교 정보통신공학부 © 조준동 2006년 여름 55

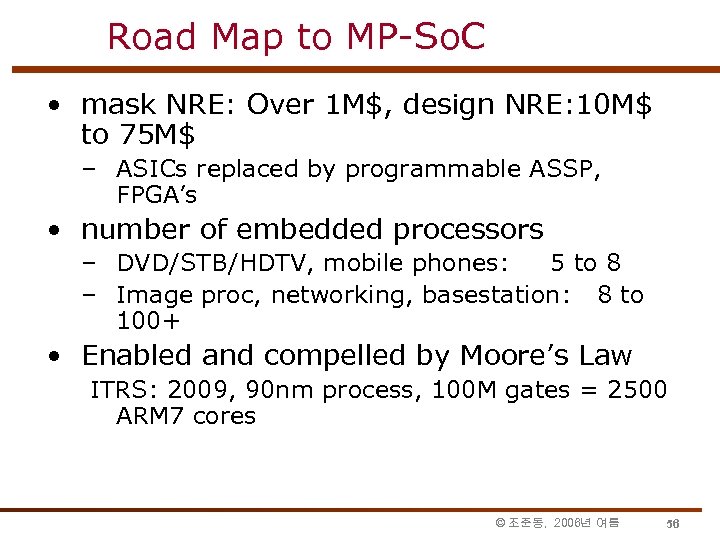

Road Map to MP-So. C • mask NRE: Over 1 M$, design NRE: 10 M$ to 75 M$ – ASICs replaced by programmable ASSP, FPGA’s • number of embedded processors – DVD/STB/HDTV, mobile phones: 5 to 8 – Image proc, networking, basestation: 8 to 100+ • Enabled and compelled by Moore’s Law ITRS: 2009, 90 nm process, 100 M gates = 2500 ARM 7 cores © 조준동, 2006년 여름 56

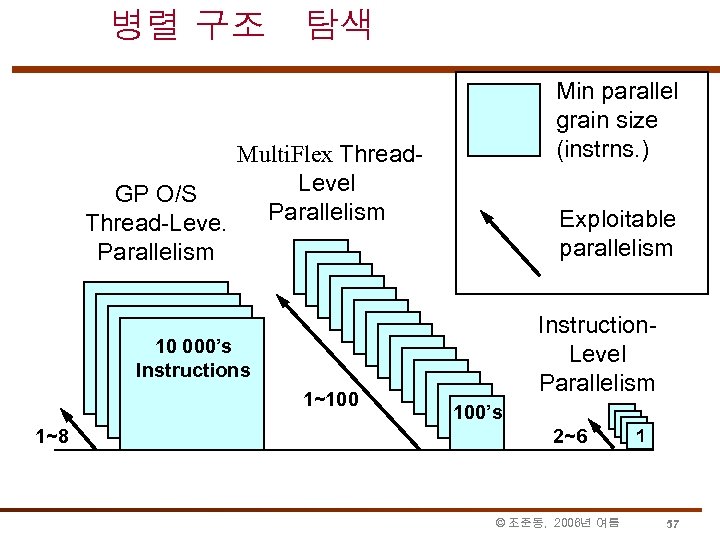

병렬 구조 탐색 Min parallel grain size (instrns. ) Multi. Flex Thread. Level GP O/S Parallelism Thread-Level Parallelism Exploitable parallelism Instruction. Level Parallelism 10 000’s Instructions 1~100 1~8 100’s 2~6 © 조준동, 2006년 여름 1 57

기존기술의 문제점 ▷같은 (호모지니어스) 프로세서를 여러 개 사용하는 것은 자원 유용도가 낮아서 리니어로 전력량이 늘 어날 수 있다. ▷ 프로세서가 와이어와 메모리 지연시간에 의해서 제 약된다. ▷ 온 칩 인터콘넥션의 설계: 타스크 매핑, IPC선택(파 이프, FIFO, 메시지 대기열, 차단 표시기, 공유 메 모리 등) © 조준동, 2006년 여름 58

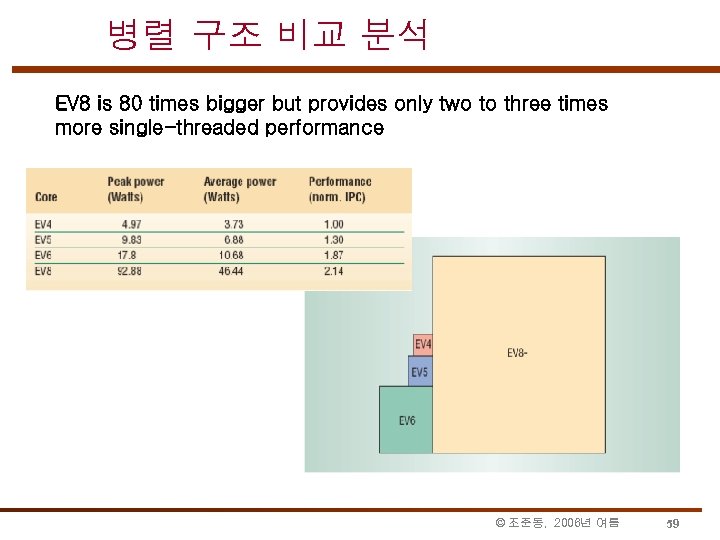

병렬 구조 비교 분석 EV 8 is 80 times bigger but provides only two to three times more single-threaded performance © 조준동, 2006년 여름 59

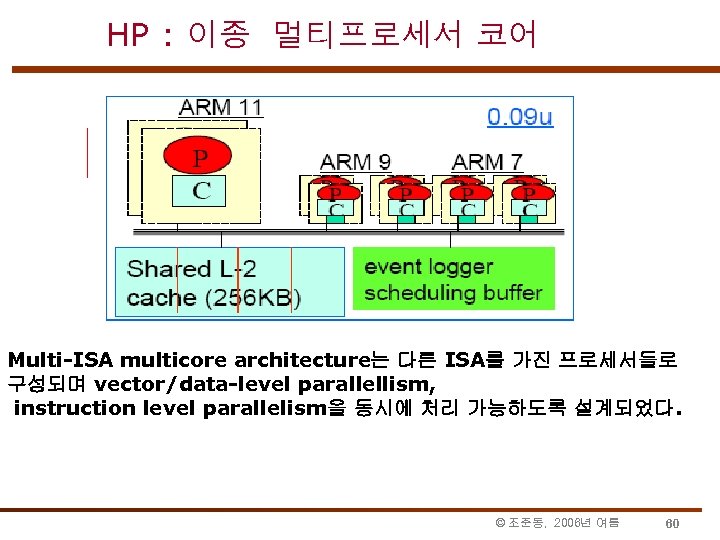

HP : 이종 멀티프로세서 코어 Multi-ISA multicore architecture는 다른 ISA를 가진 프로세서들로 구성되며 vector/data-level parallellism, instruction level parallelism을 동시에 처리 가능하도록 설계되었다. © 조준동, 2006년 여름 60

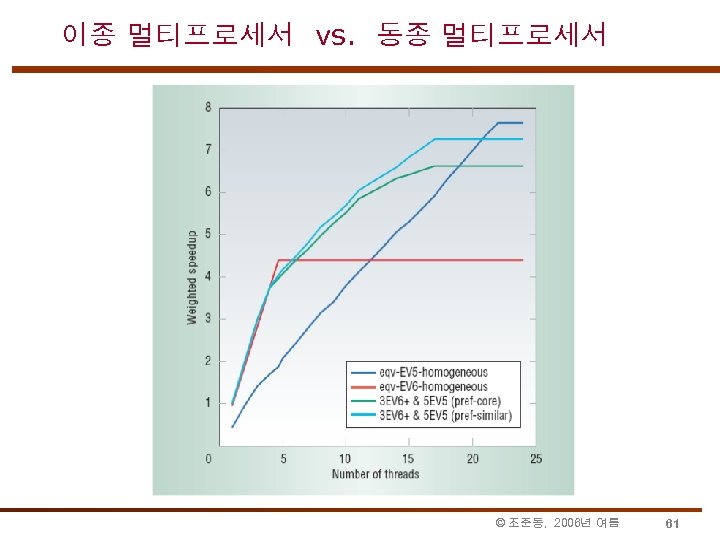

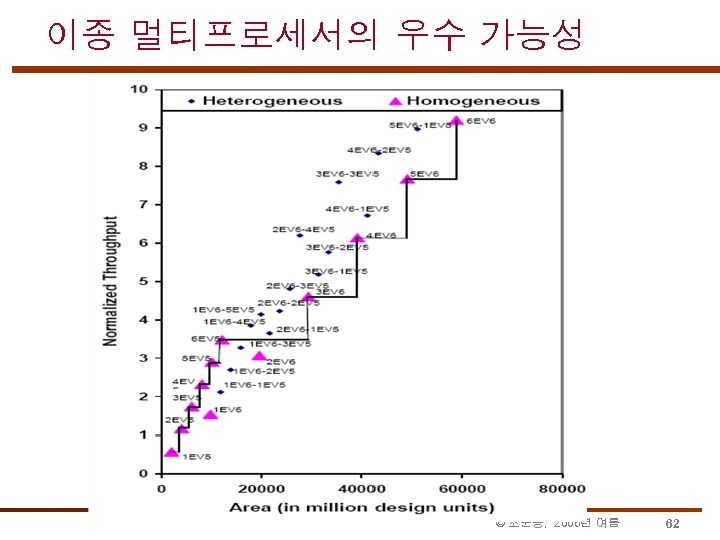

이종 멀티프로세서 vs. 동종 멀티프로세서 © 조준동, 2006년 여름 61

이종 멀티프로세서의 우수 가능성 © 조준동, 2006년 여름 62

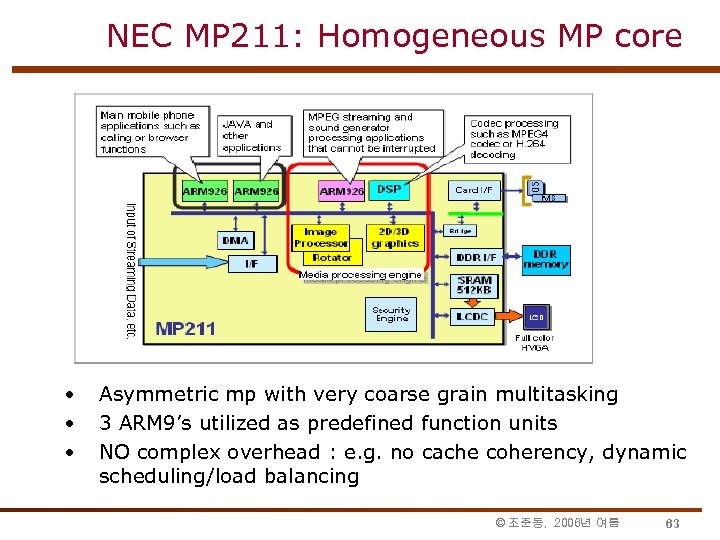

NEC MP 211: Homogeneous MP core • • • Asymmetric mp with very coarse grain multitasking 3 ARM 9’s utilized as predefined function units NO complex overhead : e. g. no cache coherency, dynamic scheduling/load balancing © 조준동, 2006년 여름 63

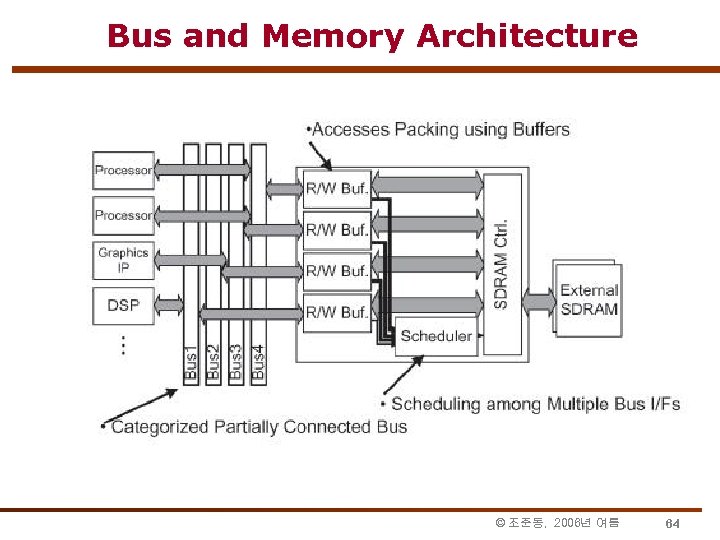

Bus and Memory Architecture © 조준동, 2006년 여름 64

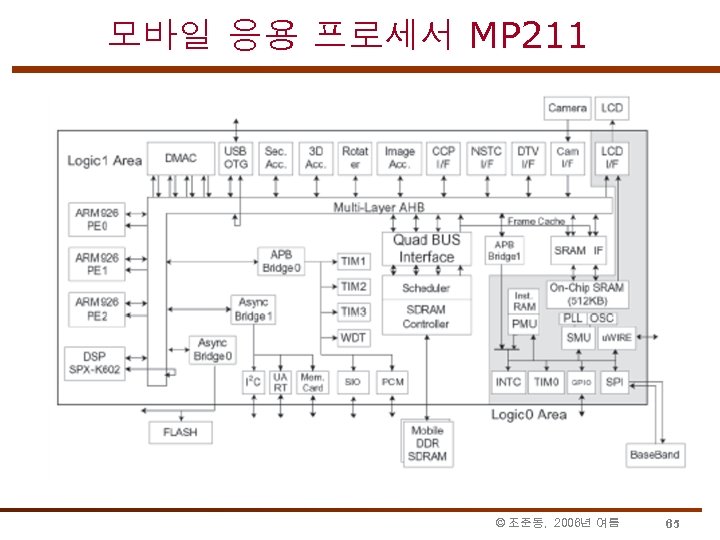

모바일 응용 프로세서 MP 211 © 조준동, 2006년 여름 65

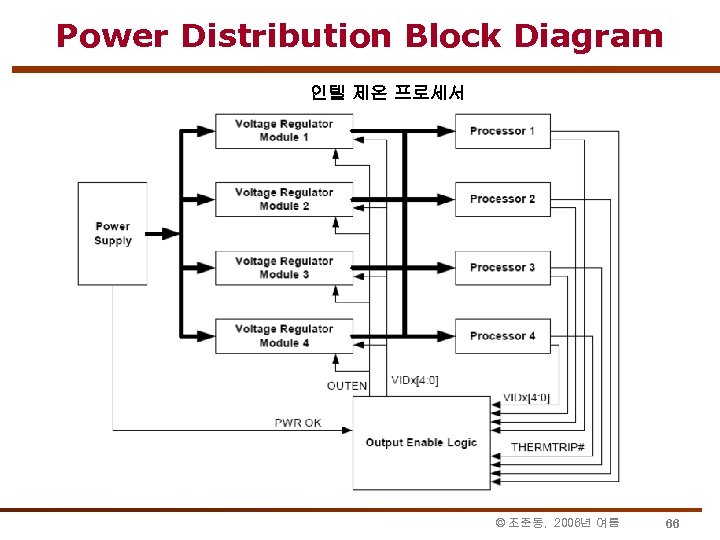

Power Distribution Block Diagram 인텔 제온 프로세서 © 조준동, 2006년 여름 66

Deep-submicron 저전력 설계 성균관대학교 정보통신공학부 © 조준동 2006년 여름 67

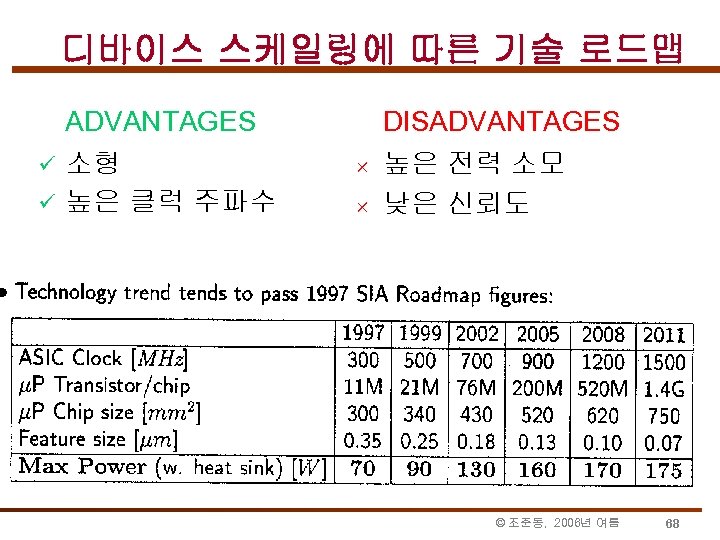

디바이스 스케일링에 따른 기술 로드맵 ADVANTAGES ü 소형 ü 높은 클럭 주파수 DISADVANTAGES ´ 높은 전력 소모 ´ 낮은 신뢰도 © 조준동, 2006년 여름 68

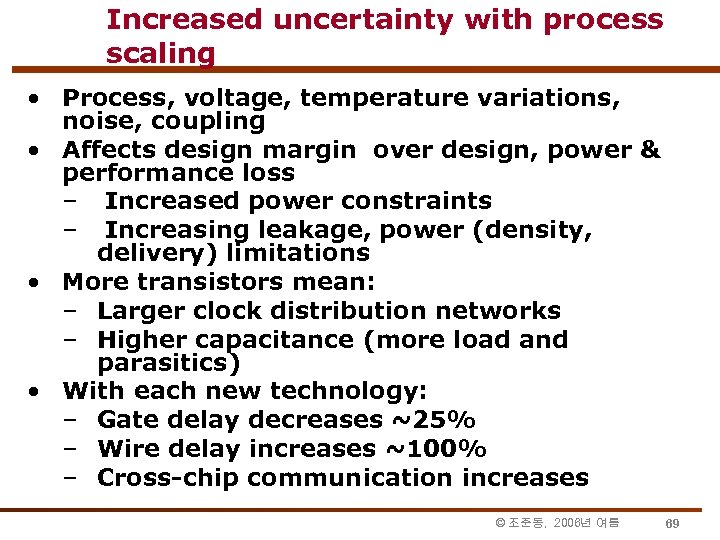

Increased uncertainty with process scaling • Process, voltage, temperature variations, noise, coupling • Affects design margin over design, power & performance loss – Increased power constraints – Increasing leakage, power (density, delivery) limitations • More transistors mean: – Larger clock distribution networks – Higher capacitance (more load and parasitics) • With each new technology: – Gate delay decreases ~25% – Wire delay increases ~100% – Cross-chip communication increases © 조준동, 2006년 여름 69

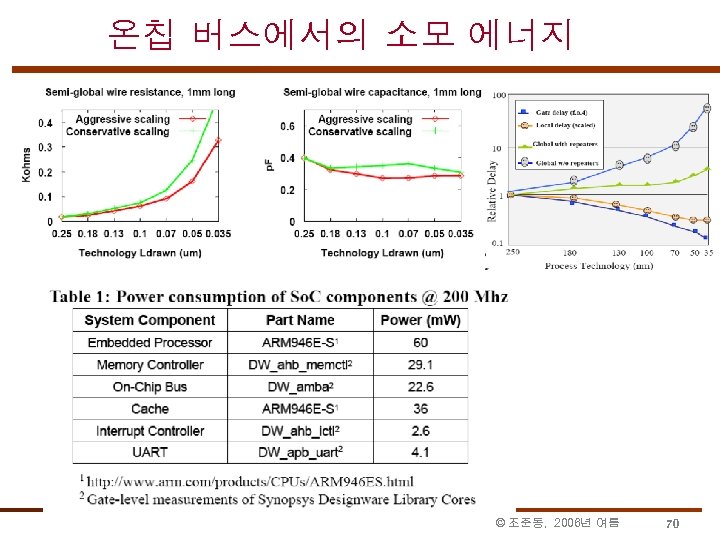

온칩 버스에서의 소모 에너지 © 조준동, 2006년 여름 70

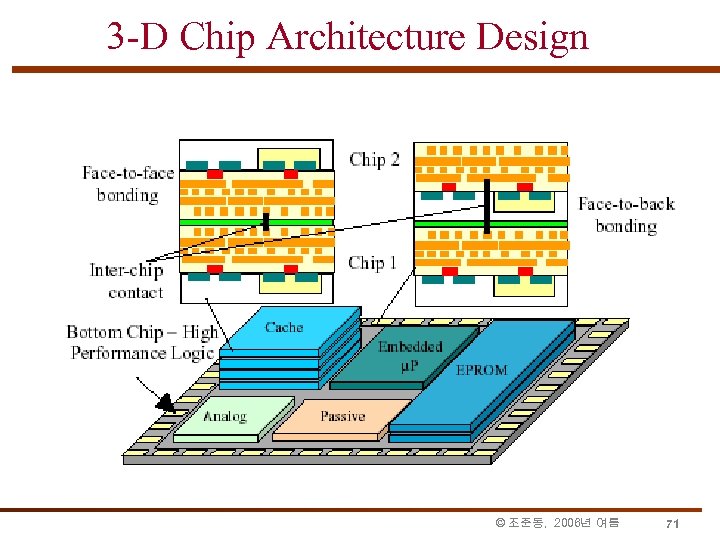

3 -D Chip Architecture Design © 조준동, 2006년 여름 71

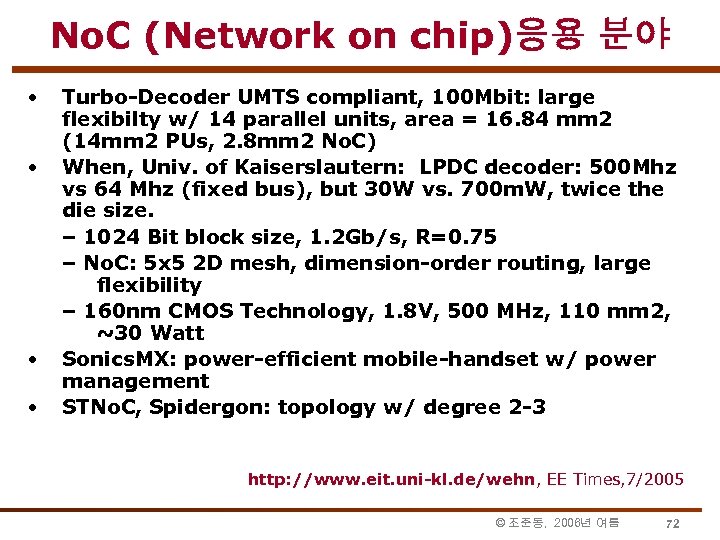

No. C (Network on chip)응용 분야 • • Turbo-Decoder UMTS compliant, 100 Mbit: large flexibilty w/ 14 parallel units, area = 16. 84 mm 2 (14 mm 2 PUs, 2. 8 mm 2 No. C) When, Univ. of Kaiserslautern: LPDC decoder: 500 Mhz vs 64 Mhz (fixed bus), but 30 W vs. 700 m. W, twice the die size. – 1024 Bit block size, 1. 2 Gb/s, R=0. 75 – No. C: 5 x 5 2 D mesh, dimension-order routing, large flexibility – 160 nm CMOS Technology, 1. 8 V, 500 MHz, 110 mm 2, ~30 Watt Sonics. MX: power-efficient mobile-handset w/ power management STNo. C, Spidergon: topology w/ degree 2 -3 http: //www. eit. uni-kl. de/wehn, EE Times, 7/2005 © 조준동, 2006년 여름 72

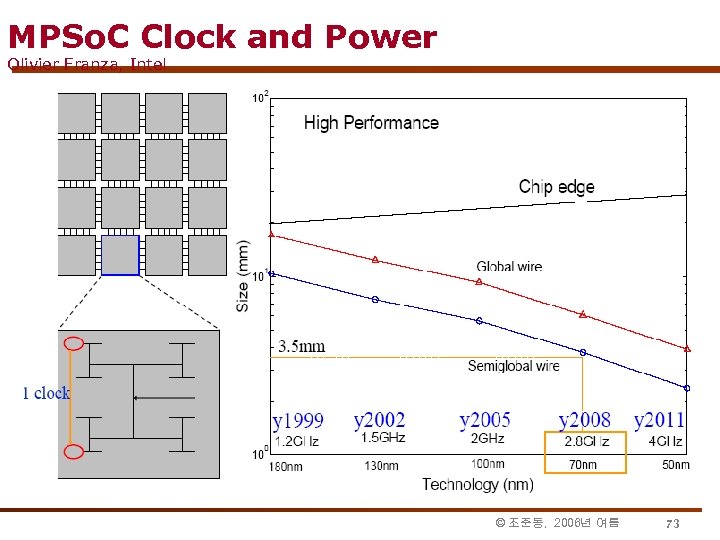

MPSo. C Clock and Power Olivier Franza, Intel © 조준동, 2006년 여름 73

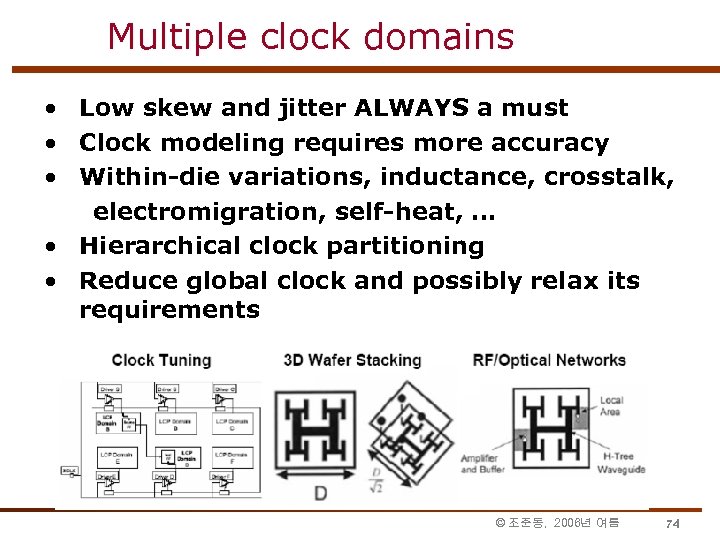

Multiple clock domains • Low skew and jitter ALWAYS a must • Clock modeling requires more accuracy • Within-die variations, inductance, crosstalk, electromigration, self-heat, … • Hierarchical clock partitioning • Reduce global clock and possibly relax its requirements © 조준동, 2006년 여름 74

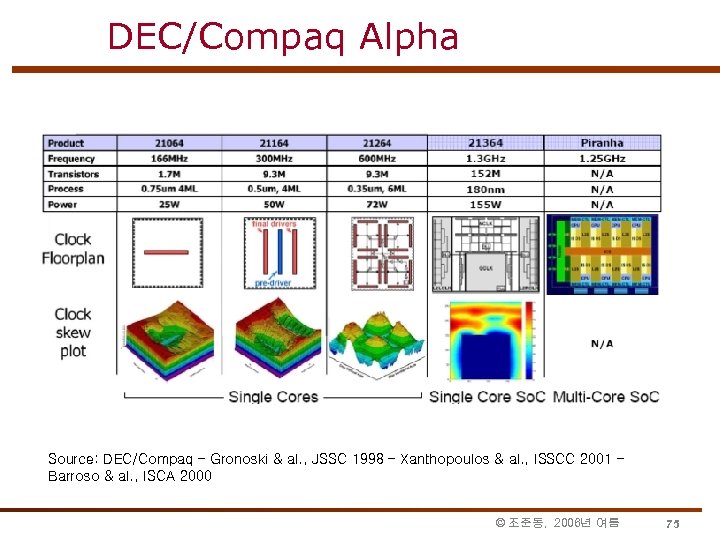

DEC/Compaq Alpha Source: DEC/Compaq – Gronoski & al. , JSSC 1998 – Xanthopoulos & al. , ISSCC 2001 – Barroso & al. , ISCA 2000 © 조준동, 2006년 여름 75

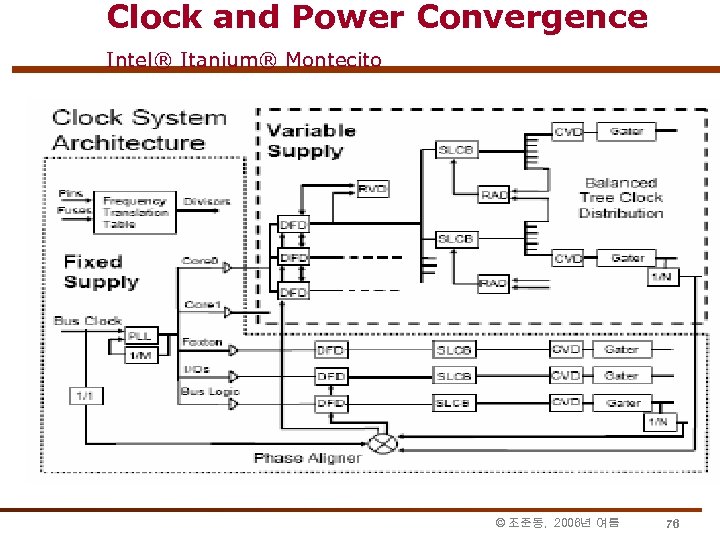

Clock and Power Convergence Intel® Itanium® Montecito © 조준동, 2006년 여름 76

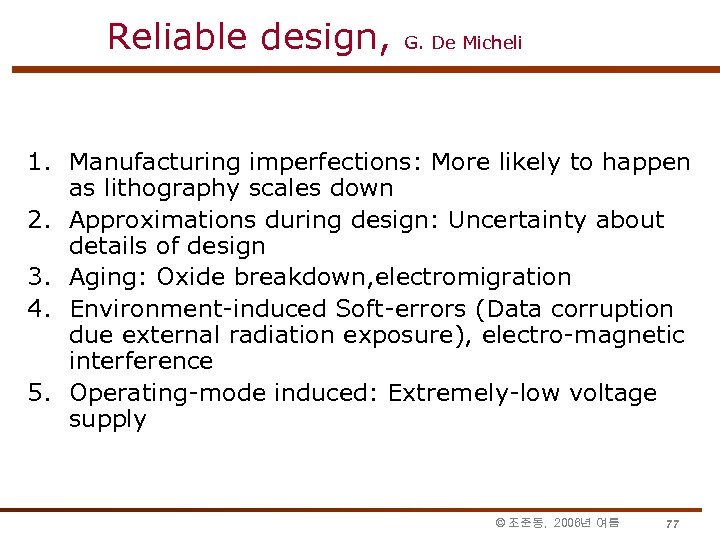

Reliable design, G. De Micheli 1. Manufacturing imperfections: More likely to happen as lithography scales down 2. Approximations during design: Uncertainty about details of design 3. Aging: Oxide breakdown, electromigration 4. Environment-induced Soft-errors (Data corruption due external radiation exposure), electro-magnetic interference 5. Operating-mode induced: Extremely-low voltage supply © 조준동, 2006년 여름 77

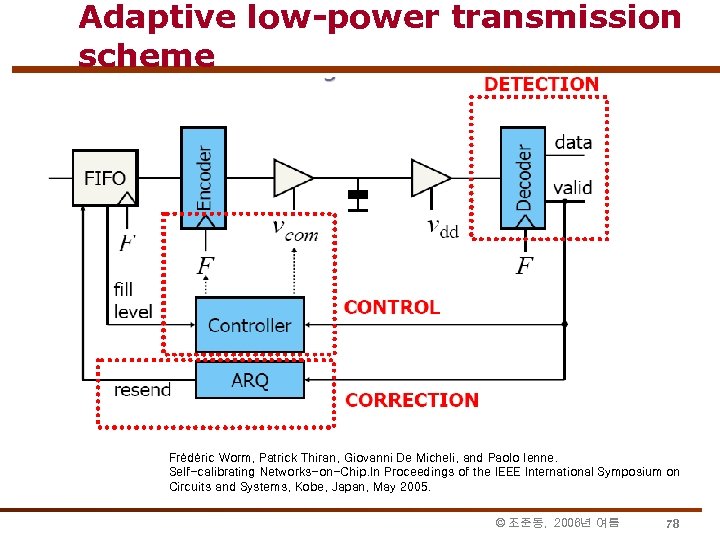

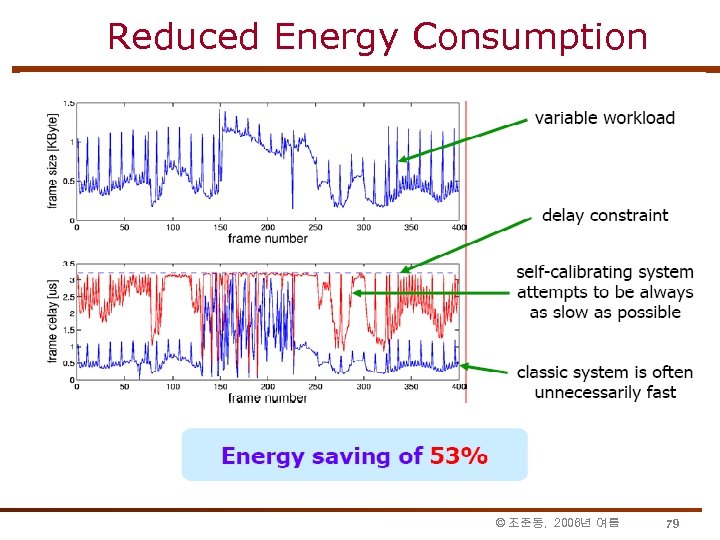

Adaptive low-power transmission scheme Frédéric Worm, Patrick Thiran, Giovanni De Micheli, and Paolo Ienne. Self-calibrating Networks-on-Chip. In Proceedings of the IEEE International Symposium on Circuits and Systems, Kobe, Japan, May 2005. © 조준동, 2006년 여름 78

Reduced Energy Consumption © 조준동, 2006년 여름 79

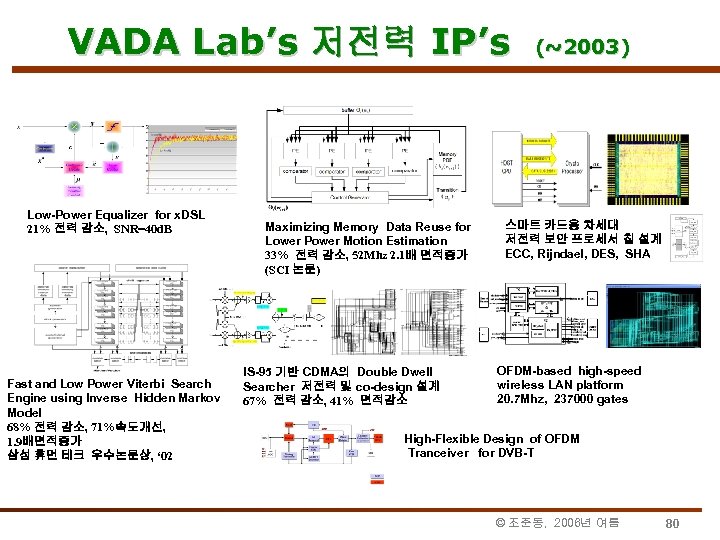

VADA Lab’s 저전력 IP’s (~2003) Low-Power Equalizer for x. DSL 21% 전력 감소, SNR=40 d. B Fast and Low Power Viterbi Search Engine using Inverse Hidden Markov Model 68% 전력 감소, 71%속도개선, 1. 9배면적증가 삼성 휴먼 테크 우수논문상, ‘ 02 Maximizing Memory Data Reuse for Lower Power Motion Estimation 33% 전력 감소, 52 Mhz 2. 1배 면적증가 (SCI 논문) IS-95 기반 CDMA의 Double Dwell Searcher 저전력 및 co-design 설계 67% 전력 감소, 41% 면적감소 스마트 카드용 차세대 저전력 보안 프로세서 칩 설계 ECC, Rijndael, DES, SHA OFDM-based high-speed wireless LAN platform 20. 7 Mhz, 237000 gates High-Flexible Design of OFDM Tranceiver for DVB-T © 조준동, 2006년 여름 80

감사합니다. 성균관대학교 정보통신공학부 © 조준동 2006년 여름 81

382c21f0e73989244674d3bcb2bd63cc.ppt