Spartan-3А Starter Kit.ppt

- Количество слайдов: 39

Spartan-3 А Starter Kit Шведков Михаил По материалам Зотова Валерия ВГТУ 2013

Spartan-3 А Starter Kit Шведков Михаил По материалам Зотова Валерия ВГТУ 2013

Назначение и состав инструментального комплекта Spartan-3 A Starter Kit • Инструментальный комплект Spartan-3 A Starter Kit можно эффективно применять в учебных лабораториях университетов для организации практического изучения, например, современных методов проектирования цифровых устройств, микропроцессорных систем с различной архитектурой, устройств цифровой обработки сигналов, микроконтроллеров. • Инструментальный комплект Spartan-3 A Starter Kit включает в себя все необходимые аппаратные и программные средства, которые требуются для практического изучения основ проектирования цифровых устройств и встраиваемых микропроцессорных систем на базе ПЛИС фирмы Xilinx и отладки собственных разрабатываемых проектов.

Назначение и состав инструментального комплекта Spartan-3 A Starter Kit • Инструментальный комплект Spartan-3 A Starter Kit можно эффективно применять в учебных лабораториях университетов для организации практического изучения, например, современных методов проектирования цифровых устройств, микропроцессорных систем с различной архитектурой, устройств цифровой обработки сигналов, микроконтроллеров. • Инструментальный комплект Spartan-3 A Starter Kit включает в себя все необходимые аппаратные и программные средства, которые требуются для практического изучения основ проектирования цифровых устройств и встраиваемых микропроцессорных систем на базе ПЛИС фирмы Xilinx и отладки собственных разрабатываемых проектов.

В состав рассматриваемого стартового комплекта входят: • плата инструментального модуля Xilinx Spartan-3 A Starter Board; • сетевой адаптер импульсного типа с выходным стабилизированным напряжением 5 В и максимальным током нагрузки 2, 5 А, который предназначен для использования в качестве первичного источника питания инструментального модуля; • стандартный USB-кабель типа Type A/Type B, предназначенный для загрузки конфигурационной последовательности в ПЛИС и программирования конфигурационных ППЗУ, установленных на плате инструментального модуля Xilinx Spartan-3 A Starter Board, а также для обратного считывания информации через соответствующий порт компьютера с помощью интегрированной схемы загрузочного кабеля; • диск DVD-ROM, содержащий новую полнофункциональную версию системы проектирования ISE™ (Integrated Software Environment/Integrated Synthesis Environment) Web. PACK™, а также оценочные версии САПР ISE Foundation™ и средств аппаратной внутрикристальной отладки разрабатываемых устройств Xilinx Chip. Scope Pro™, которые могут использоваться в течение 60 дней с момента установки.

В состав рассматриваемого стартового комплекта входят: • плата инструментального модуля Xilinx Spartan-3 A Starter Board; • сетевой адаптер импульсного типа с выходным стабилизированным напряжением 5 В и максимальным током нагрузки 2, 5 А, который предназначен для использования в качестве первичного источника питания инструментального модуля; • стандартный USB-кабель типа Type A/Type B, предназначенный для загрузки конфигурационной последовательности в ПЛИС и программирования конфигурационных ППЗУ, установленных на плате инструментального модуля Xilinx Spartan-3 A Starter Board, а также для обратного считывания информации через соответствующий порт компьютера с помощью интегрированной схемы загрузочного кабеля; • диск DVD-ROM, содержащий новую полнофункциональную версию системы проектирования ISE™ (Integrated Software Environment/Integrated Synthesis Environment) Web. PACK™, а также оценочные версии САПР ISE Foundation™ и средств аппаратной внутрикристальной отладки разрабатываемых устройств Xilinx Chip. Scope Pro™, которые могут использоваться в течение 60 дней с момента установки.

Руководства пользователя • http: //www. xilinx. com/bvdocs/userguides/ug 33 0. pdf (REV C) • http: //www. xilinx. com/bvdocs/userguides/ug 33 4. pdf (REV D) • http: //www. xilinx. com/products/boards/files/s 3 a_starter_schematic. pdf (Принципиальная схема)

Руководства пользователя • http: //www. xilinx. com/bvdocs/userguides/ug 33 0. pdf (REV C) • http: //www. xilinx. com/bvdocs/userguides/ug 33 4. pdf (REV D) • http: //www. xilinx. com/products/boards/files/s 3 a_starter_schematic. pdf (Принципиальная схема)

Основные функциональные возможности • использование в качестве основного компонента ПЛИС из семейства Spartan-3 A с объемом 700 000 системных вентилей (13 248 логических ячеек) в корпусе FGG 484, объем логических и трассировочных ресурсов которой в сочетании с большим количеством пользовательских выводов обеспечивает возможность реализации проектов устройств высокого уровня сложности; • применение в качестве стандартного ППЗУ для хранения конфигурационных данных кристалла Flash-памяти серии Platform Flash, программируемой в системе, объемом 4 Мбит; • наличие двух видов последовательной Flash-памяти объемом 16 Мбит с интерфейсом SPI (Serial Peripheral Interface), которые могут применяться для записи конфигурационной информации кристалла семейства Spartan-3 A, исполняемого программного кода для встраиваемой микропроцессорной системы, реализуемой на базе 32 -разрядного ядра семейства Micro. Blaze, или в качестве энергонезависимой памяти данных; • возможность использования модуля параллельной NOR Flash-памяти емкостью 4 Мбайт (32 Мбит), которая по выбору пользователя может выполнять функции хранения конфигурационной последовательности данных ПЛИС семейства Spartan 3 A или программного кода встраиваемой микропроцессорной системы, реализуемой на основе 32 -разрядного ядра семейства Micro. Blaze;

Основные функциональные возможности • использование в качестве основного компонента ПЛИС из семейства Spartan-3 A с объемом 700 000 системных вентилей (13 248 логических ячеек) в корпусе FGG 484, объем логических и трассировочных ресурсов которой в сочетании с большим количеством пользовательских выводов обеспечивает возможность реализации проектов устройств высокого уровня сложности; • применение в качестве стандартного ППЗУ для хранения конфигурационных данных кристалла Flash-памяти серии Platform Flash, программируемой в системе, объемом 4 Мбит; • наличие двух видов последовательной Flash-памяти объемом 16 Мбит с интерфейсом SPI (Serial Peripheral Interface), которые могут применяться для записи конфигурационной информации кристалла семейства Spartan-3 A, исполняемого программного кода для встраиваемой микропроцессорной системы, реализуемой на базе 32 -разрядного ядра семейства Micro. Blaze, или в качестве энергонезависимой памяти данных; • возможность использования модуля параллельной NOR Flash-памяти емкостью 4 Мбайт (32 Мбит), которая по выбору пользователя может выполнять функции хранения конфигурационной последовательности данных ПЛИС семейства Spartan 3 A или программного кода встраиваемой микропроцессорной системы, реализуемой на основе 32 -разрядного ядра семейства Micro. Blaze;

Основные функциональные возможности • применение внешнего высокоскоростного синхронного динамического ОЗУ с удвоенной скоростью передачи данных, выполненного в виде DDR 2 SDRAM емкостью 64 Мбайт (512 Мбит), существенно расширяющее возможности оперативной памяти встраиваемых систем, реализуемой на основе соответствующих внутренних ресурсов ПЛИС; • наличие на плате разъемов стандартных интерфейсов вычислительных систем RS 232, PS/2, VGA и Ethernet, позволяющих разрабатывать и отлаживать проекты устройств с соответствующими интерфейсами, а также подключать к инструментальному модулю внешние устройства с последовательным интерфейсом, клавиатуру, мышь, дисплей (при поддержке этих устройств на уровне проектов); • применение в составе модуля преобразователя уровней RS-232 и двух девятиконтактных разъемов DB-9 (типа DTE и DCE), которые обеспечивают возможность непосредственного одновременного подключения к последовательным портам отладочной платы двух внешних устройств различного типа (при реализации универсального асинхронного приемопередатчика UART на основе ресурсов кристалла ПЛИС);

Основные функциональные возможности • применение внешнего высокоскоростного синхронного динамического ОЗУ с удвоенной скоростью передачи данных, выполненного в виде DDR 2 SDRAM емкостью 64 Мбайт (512 Мбит), существенно расширяющее возможности оперативной памяти встраиваемых систем, реализуемой на основе соответствующих внутренних ресурсов ПЛИС; • наличие на плате разъемов стандартных интерфейсов вычислительных систем RS 232, PS/2, VGA и Ethernet, позволяющих разрабатывать и отлаживать проекты устройств с соответствующими интерфейсами, а также подключать к инструментальному модулю внешние устройства с последовательным интерфейсом, клавиатуру, мышь, дисплей (при поддержке этих устройств на уровне проектов); • применение в составе модуля преобразователя уровней RS-232 и двух девятиконтактных разъемов DB-9 (типа DTE и DCE), которые обеспечивают возможность непосредственного одновременного подключения к последовательным портам отладочной платы двух внешних устройств различного типа (при реализации универсального асинхронного приемопередатчика UART на основе ресурсов кристалла ПЛИС);

Основные функциональные возможности • наличие дополнительных компонентов, предназначенных для формирования физического уровня интерфейса 10/100 Ethernet PHY, который позволяет подключать инструментальный модуль через стандартный разъем непосредственно к соответствующей сети, при реализации контроллера Ethernet MAC в составе проекта, загружаемого в кристалл семейства Spartan-3 A; • подключение специальных и пользовательских выводов ПЛИС к контактам четырех разъемов расширения, соответствующих различным стандартам, поддерживаемым дополнительными периферийными инструментальными модулями (картами расширения), которые выпускаются фирмой Digilent Incorporated; • присутствие на плате двух разъемов, предназначенных для подключения высокоскоростных входных и выходных сигналов, соответствующих цифровым дифференциальным стандартам, которые поддерживаются блоками ввода/вывода ПЛИС семейства Spartan-3 A;

Основные функциональные возможности • наличие дополнительных компонентов, предназначенных для формирования физического уровня интерфейса 10/100 Ethernet PHY, который позволяет подключать инструментальный модуль через стандартный разъем непосредственно к соответствующей сети, при реализации контроллера Ethernet MAC в составе проекта, загружаемого в кристалл семейства Spartan-3 A; • подключение специальных и пользовательских выводов ПЛИС к контактам четырех разъемов расширения, соответствующих различным стандартам, поддерживаемым дополнительными периферийными инструментальными модулями (картами расширения), которые выпускаются фирмой Digilent Incorporated; • присутствие на плате двух разъемов, предназначенных для подключения высокоскоростных входных и выходных сигналов, соответствующих цифровым дифференциальным стандартам, которые поддерживаются блоками ввода/вывода ПЛИС семейства Spartan-3 A;

Основные функциональные возможности • применение двухканального аналого-цифрового преобразователя ADC (Analog-to. Digital Converter) с интерфейсом управления SPI и шестиконтактного входного разъема, предоставляющих возможность сопряжения входов цифровой части разрабатываемого устройства, реализуемого на основе ресурсов ПЛИС, с выходами аналогового блока; • наличие четырехканального последовательного цифро-аналогового преобразователя DAC (Digital-to-Analog Converter) с 12 -разрядным разрешением, управляемого с помощью интерфейса SPI, ишестиконтактного выходного разъема, которые обеспечивают возможность сопряжения выходов цифровой части проектируемого устройства, реализуемого на базе кристалла, со входами аналогового блока; • использование кварцевого генератора с частотой 50 МГц, предназначенного для формирования сигнала синхронизации большинства компонентов инструментального модуля, включая ПЛИС; • полная совместимость аппаратного модуля со всем семейством систем проектирования и программирования кристаллов фирмы Xilinx серии ISE (ISE Web. PACK [13] и ISE Foundation) версии 9. x и поддержка средствами разработки встраиваемых микропроцессорных систем Xilinx EDK [3, 12].

Основные функциональные возможности • применение двухканального аналого-цифрового преобразователя ADC (Analog-to. Digital Converter) с интерфейсом управления SPI и шестиконтактного входного разъема, предоставляющих возможность сопряжения входов цифровой части разрабатываемого устройства, реализуемого на основе ресурсов ПЛИС, с выходами аналогового блока; • наличие четырехканального последовательного цифро-аналогового преобразователя DAC (Digital-to-Analog Converter) с 12 -разрядным разрешением, управляемого с помощью интерфейса SPI, ишестиконтактного выходного разъема, которые обеспечивают возможность сопряжения выходов цифровой части проектируемого устройства, реализуемого на базе кристалла, со входами аналогового блока; • использование кварцевого генератора с частотой 50 МГц, предназначенного для формирования сигнала синхронизации большинства компонентов инструментального модуля, включая ПЛИС; • полная совместимость аппаратного модуля со всем семейством систем проектирования и программирования кристаллов фирмы Xilinx серии ISE (ISE Web. PACK [13] и ISE Foundation) версии 9. x и поддержка средствами разработки встраиваемых микропроцессорных систем Xilinx EDK [3, 12].

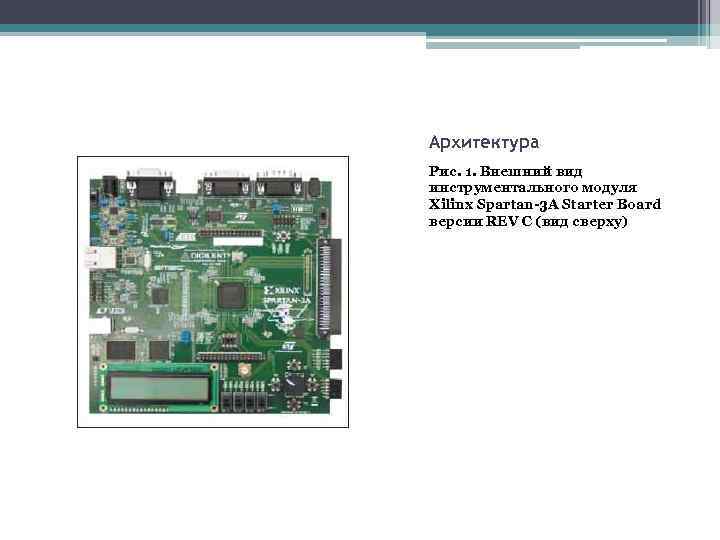

Архитектура Рис. 1. Внешний вид инструментального модуля Xilinx Spartan-3 A Starter Board версии REV C (вид сверху)

Архитектура Рис. 1. Внешний вид инструментального модуля Xilinx Spartan-3 A Starter Board версии REV C (вид сверху)

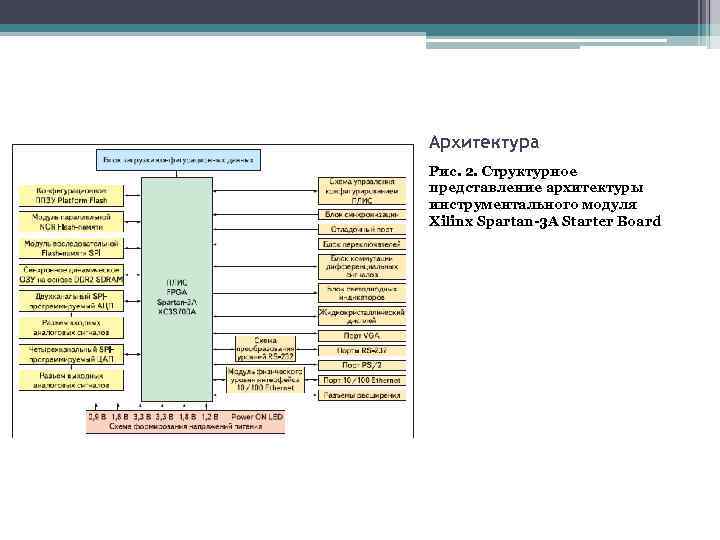

Архитектура Рис. 2. Структурное представление архитектуры инструментального модуля Xilinx Spartan-3 A Starter Board

Архитектура Рис. 2. Структурное представление архитектуры инструментального модуля Xilinx Spartan-3 A Starter Board

Основные элементы архитектуры • кристалл XC 3 S 700 A семейства Spartan-3 A в корпусе FGG 484 с шариковыми выводами для бессвинцовой пайки, на основе ресурсов которой реализуется проектируемая система; • программируемое в системе ППЗУ серии Platform Flash XCF 04 S, предназначенное для хранения конфигурационных данных ПЛИС XC 3 S 700 A; • блок загрузки конфигурационных данных; • схема управления конфигурированием ПЛИС; • блок синхронизации, предназначенный для формирования исходных внешних (по отношению к кристаллу) тактовых сигналов; • внешнее высокоскоростное ОЗУ; • узел двухканального аналого-цифрового преобразователя (АЦП); • узел четырехканального цифро-аналогового преобразователя (ЦАП); • блок параллельной NOR Flash-памяти емкостью 4 Мбайт (32 Мбит); • блок последовательной Flash-памяти объемом 2× 16 Мбит с интерфейсом SPI;

Основные элементы архитектуры • кристалл XC 3 S 700 A семейства Spartan-3 A в корпусе FGG 484 с шариковыми выводами для бессвинцовой пайки, на основе ресурсов которой реализуется проектируемая система; • программируемое в системе ППЗУ серии Platform Flash XCF 04 S, предназначенное для хранения конфигурационных данных ПЛИС XC 3 S 700 A; • блок загрузки конфигурационных данных; • схема управления конфигурированием ПЛИС; • блок синхронизации, предназначенный для формирования исходных внешних (по отношению к кристаллу) тактовых сигналов; • внешнее высокоскоростное ОЗУ; • узел двухканального аналого-цифрового преобразователя (АЦП); • узел четырехканального цифро-аналогового преобразователя (ЦАП); • блок параллельной NOR Flash-памяти емкостью 4 Мбайт (32 Мбит); • блок последовательной Flash-памяти объемом 2× 16 Мбит с интерфейсом SPI;

Основные элементы архитектуры • узел последовательного интерфейса RS-232; • узел интерфейса 10/100 Ethernet; • блок коммутации высокоскоростных дифференциальных сигналов; • схема формирования и контроля питающих напряжений; • блок светодиодных индикаторов; • двухстрочный 16 -значный жидкокристаллический дисплей; • блок ползунковых и кнопочных переключателей; • отладочный порт; • стандартные разъемы интерфейсов PS/2, VGA и Audio Stereo Mini Jack; • четыре разъема расширения.

Основные элементы архитектуры • узел последовательного интерфейса RS-232; • узел интерфейса 10/100 Ethernet; • блок коммутации высокоскоростных дифференциальных сигналов; • схема формирования и контроля питающих напряжений; • блок светодиодных индикаторов; • двухстрочный 16 -значный жидкокристаллический дисплей; • блок ползунковых и кнопочных переключателей; • отладочный порт; • стандартные разъемы интерфейсов PS/2, VGA и Audio Stereo Mini Jack; • четыре разъема расширения.

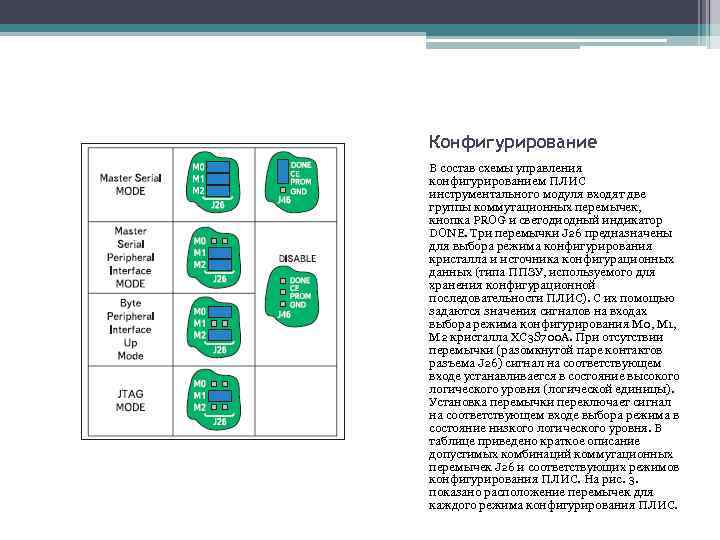

Конфигурирование В состав схемы управления конфигурированием ПЛИС инструментального модуля входят две группы коммутационных перемычек, кнопка PROG и светодиодный индикатор DONE. Три перемычки J 26 предназначены для выбора режима конфигурирования кристалла и источника конфигурационных данных (типа ППЗУ, используемого для хранения конфигурационной последовательности ПЛИС). С их помощью задаются значения сигналов на входах выбора режима конфигурирования M 0, M 1, M 2 кристалла XC 3 S 700 A. При отсутствии перемычки (разомкнутой паре контактов разъема J 26) сигнал на соответствующем входе устанавливается в состояние высокого логического уровня (логической единицы). Установка перемычки переключает сигнал на соответствующем входе выбора режима в состояние низкого логического уровня. В таблице приведено краткое описание допустимых комбинаций коммутационных перемычек J 26 и соответствующих режимов конфигурирования ПЛИС. На рис. 3. показано расположение перемычек для каждого режима конфигурирования ПЛИС.

Конфигурирование В состав схемы управления конфигурированием ПЛИС инструментального модуля входят две группы коммутационных перемычек, кнопка PROG и светодиодный индикатор DONE. Три перемычки J 26 предназначены для выбора режима конфигурирования кристалла и источника конфигурационных данных (типа ППЗУ, используемого для хранения конфигурационной последовательности ПЛИС). С их помощью задаются значения сигналов на входах выбора режима конфигурирования M 0, M 1, M 2 кристалла XC 3 S 700 A. При отсутствии перемычки (разомкнутой паре контактов разъема J 26) сигнал на соответствующем входе устанавливается в состояние высокого логического уровня (логической единицы). Установка перемычки переключает сигнал на соответствующем входе выбора режима в состояние низкого логического уровня. В таблице приведено краткое описание допустимых комбинаций коммутационных перемычек J 26 и соответствующих режимов конфигурирования ПЛИС. На рис. 3. показано расположение перемычек для каждого режима конфигурирования ПЛИС.

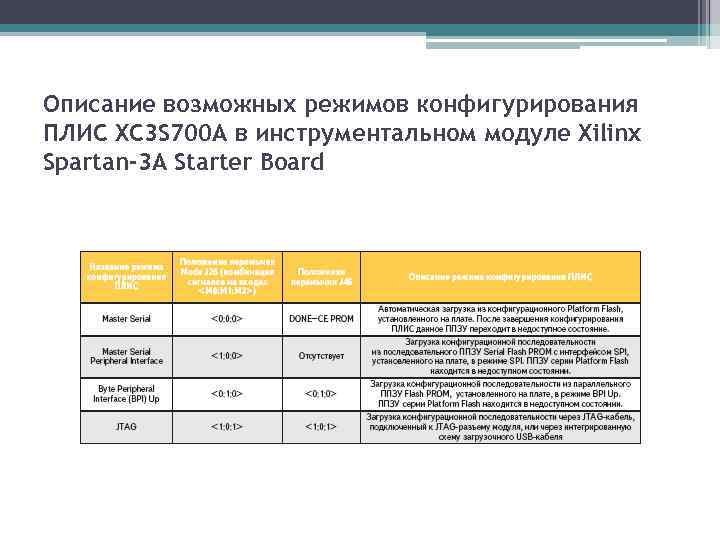

Описание возможных режимов конфигурирования ПЛИС XC 3 S 700 A в инструментальном модуле Xilinx Spartan-3 A Starter Board

Описание возможных режимов конфигурирования ПЛИС XC 3 S 700 A в инструментальном модуле Xilinx Spartan-3 A Starter Board

Блок синхронизации • Основными элементами блока синхронизации являются: кварцевый генератор с частотой 50 МГц, панель для установки дополнительного кварцевого генератора в восьмиконтактном DIP-корпусе и высокочастотный разъем типа SMA, который может использоваться для подключения внешнего сигнала синхронизации или вывода тактового сигнала, сформированного соответствующими внутренними модулями ПЛИС. Внешний тактовый сигнал, который вырабатывает кварцевый генератор, установленный на плате инструментального модуля, поступает на один из шестнадцати специально выделенных контактов кристалла, сопряженных с глобальными буферными элементами, а именно на GCLK 5 (вывод E 12 для корпуса FGG 484). Так как выход каждого глобального буфера связан (через глобальные тактовые мультиплексоры) с глобальной сетью тактовых линий и цифровыми блоками управления синхронизацией (Digital Clock Manager, DCM) ПЛИС семейства Spartan-3 A, то такое решение оптимальным образом обеспечивает возможность применения модуля DCM для получения сетки тактовых частот, соответствующих требованиям реализуемого проекта.

Блок синхронизации • Основными элементами блока синхронизации являются: кварцевый генератор с частотой 50 МГц, панель для установки дополнительного кварцевого генератора в восьмиконтактном DIP-корпусе и высокочастотный разъем типа SMA, который может использоваться для подключения внешнего сигнала синхронизации или вывода тактового сигнала, сформированного соответствующими внутренними модулями ПЛИС. Внешний тактовый сигнал, который вырабатывает кварцевый генератор, установленный на плате инструментального модуля, поступает на один из шестнадцати специально выделенных контактов кристалла, сопряженных с глобальными буферными элементами, а именно на GCLK 5 (вывод E 12 для корпуса FGG 484). Так как выход каждого глобального буфера связан (через глобальные тактовые мультиплексоры) с глобальной сетью тактовых линий и цифровыми блоками управления синхронизацией (Digital Clock Manager, DCM) ПЛИС семейства Spartan-3 A, то такое решение оптимальным образом обеспечивает возможность применения модуля DCM для получения сетки тактовых частот, соответствующих требованиям реализуемого проекта.

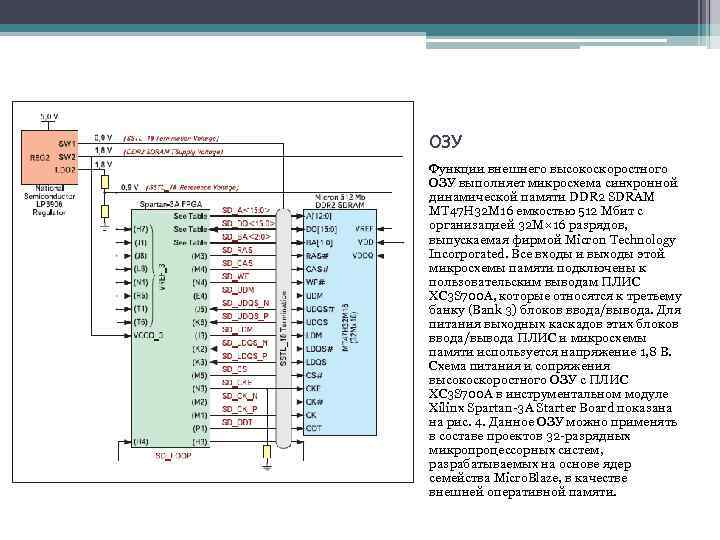

ОЗУ Функции внешнего высокоскоростного ОЗУ выполняет микросхема синхронной динамической памяти DDR 2 SDRAM MT 47 H 32 M 16 емкостью 512 Мбит с организацией 32 М× 16 разрядов, выпускаемая фирмой Micron Technology Incorporated. Все входы и выходы этой микросхемы памяти подключены к пользовательским выводам ПЛИС XC 3 S 700 A, которые относятся к третьему банку (Bank 3) блоков ввода/вывода. Для питания выходных каскадов этих блоков ввода/вывода ПЛИС и микросхемы памяти используется напряжение 1, 8 В. Схема питания и сопряжения высокоскоростного ОЗУ с ПЛИС XC 3 S 700 A в инструментальном модуле Xilinx Spartan-3 A Starter Board показана на рис. 4. Данное ОЗУ можно применять в составе проектов 32 -разрядных микропроцессорных систем, разрабатываемых на основе ядер семейства Micro. Blaze, в качестве внешней оперативной памяти.

ОЗУ Функции внешнего высокоскоростного ОЗУ выполняет микросхема синхронной динамической памяти DDR 2 SDRAM MT 47 H 32 M 16 емкостью 512 Мбит с организацией 32 М× 16 разрядов, выпускаемая фирмой Micron Technology Incorporated. Все входы и выходы этой микросхемы памяти подключены к пользовательским выводам ПЛИС XC 3 S 700 A, которые относятся к третьему банку (Bank 3) блоков ввода/вывода. Для питания выходных каскадов этих блоков ввода/вывода ПЛИС и микросхемы памяти используется напряжение 1, 8 В. Схема питания и сопряжения высокоскоростного ОЗУ с ПЛИС XC 3 S 700 A в инструментальном модуле Xilinx Spartan-3 A Starter Board показана на рис. 4. Данное ОЗУ можно применять в составе проектов 32 -разрядных микропроцессорных систем, разрабатываемых на основе ядер семейства Micro. Blaze, в качестве внешней оперативной памяти.

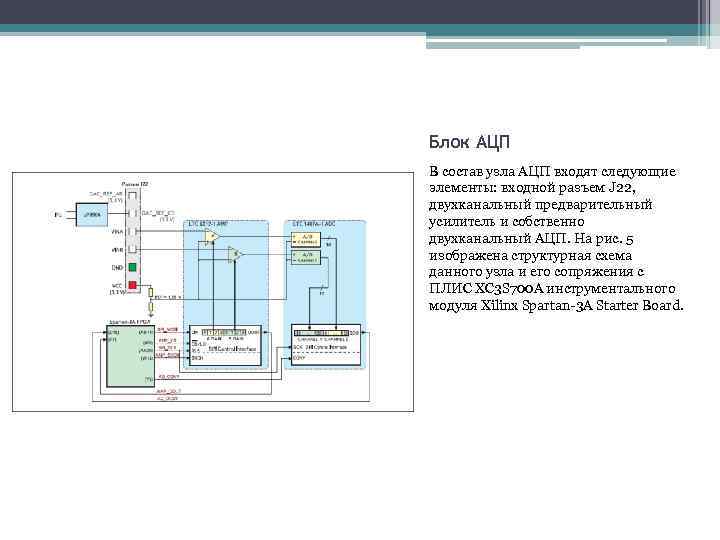

Блок АЦП В состав узла АЦП входят следующие элементы: входной разъем J 22, двухканальный предварительный усилитель и собственно двухканальный АЦП. На рис. 5 изображена структурная схема данного узла и его сопряжения с ПЛИС XC 3 S 700 A инструментального модуля Xilinx Spartan-3 A Starter Board.

Блок АЦП В состав узла АЦП входят следующие элементы: входной разъем J 22, двухканальный предварительный усилитель и собственно двухканальный АЦП. На рис. 5 изображена структурная схема данного узла и его сопряжения с ПЛИС XC 3 S 700 A инструментального модуля Xilinx Spartan-3 A Starter Board.

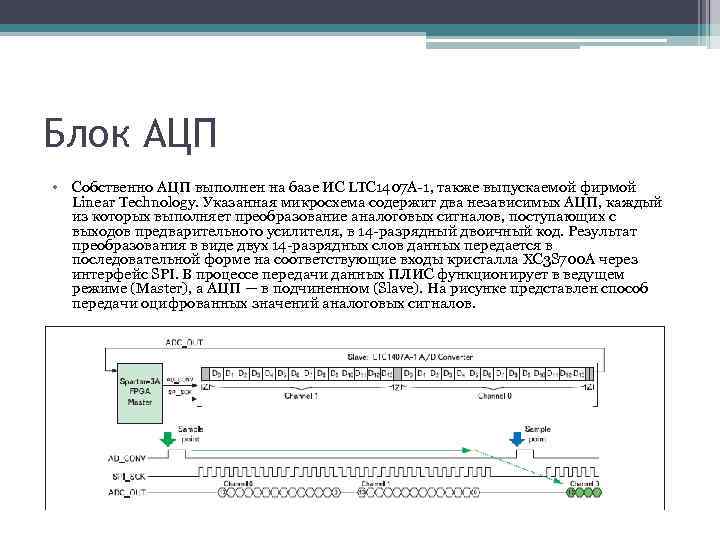

Блок АЦП • Собственно АЦП выполнен на базе ИС LTC 1407 A-1, также выпускаемой фирмой Linear Technology. Указанная микросхема содержит два независимых АЦП, каждый из которых выполняет преобразование аналоговых сигналов, поступающих с выходов предварительного усилителя, в 14 -разрядный двоичный код. Результат преобразования в виде двух 14 -разрядных слов данных передается в последовательной форме на соответствующие входы кристалла XC 3 S 700 A через интерфейс SPI. В процессе передачи данных ПЛИС функционирует в ведущем режиме (Master), а АЦП — в подчиненном (Slave). На рисунке представлен способ передачи оцифрованных значений аналоговых сигналов.

Блок АЦП • Собственно АЦП выполнен на базе ИС LTC 1407 A-1, также выпускаемой фирмой Linear Technology. Указанная микросхема содержит два независимых АЦП, каждый из которых выполняет преобразование аналоговых сигналов, поступающих с выходов предварительного усилителя, в 14 -разрядный двоичный код. Результат преобразования в виде двух 14 -разрядных слов данных передается в последовательной форме на соответствующие входы кристалла XC 3 S 700 A через интерфейс SPI. В процессе передачи данных ПЛИС функционирует в ведущем режиме (Master), а АЦП — в подчиненном (Slave). На рисунке представлен способ передачи оцифрованных значений аналоговых сигналов.

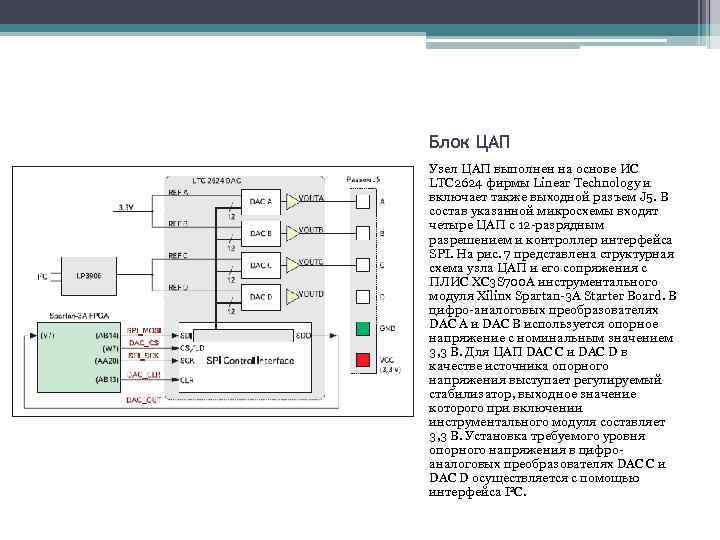

Блок ЦАП Узел ЦАП выполнен на основе ИС LTC 2624 фирмы Linear Technology и включает также выходной разъем J 5. В состав указанной микросхемы входят четыре ЦАП с 12 -разрядным разрешением и контроллер интерфейса SPI. На рис. 7 представлена структурная схема узла ЦАП и его сопряжения с ПЛИС XC 3 S 700 A инструментального модуля Xilinx Spartan-3 A Starter Board. В цифро-аналоговых преобразователях DAC A и DAC B используется опорное напряжение с номинальным значением 3, 3 В. Для ЦАП DAC C и DAC D в качестве источника опорного напряжения выступает регулируемый стабилизатор, выходное значение которого при включении инструментального модуля составляет 3, 3 В. Установка требуемого уровня опорного напряжения в цифроаналоговых преобразователях DAC C и DAC D осуществляется с помощью интерфейса I 2 C.

Блок ЦАП Узел ЦАП выполнен на основе ИС LTC 2624 фирмы Linear Technology и включает также выходной разъем J 5. В состав указанной микросхемы входят четыре ЦАП с 12 -разрядным разрешением и контроллер интерфейса SPI. На рис. 7 представлена структурная схема узла ЦАП и его сопряжения с ПЛИС XC 3 S 700 A инструментального модуля Xilinx Spartan-3 A Starter Board. В цифро-аналоговых преобразователях DAC A и DAC B используется опорное напряжение с номинальным значением 3, 3 В. Для ЦАП DAC C и DAC D в качестве источника опорного напряжения выступает регулируемый стабилизатор, выходное значение которого при включении инструментального модуля составляет 3, 3 В. Установка требуемого уровня опорного напряжения в цифроаналоговых преобразователях DAC C и DAC D осуществляется с помощью интерфейса I 2 C.

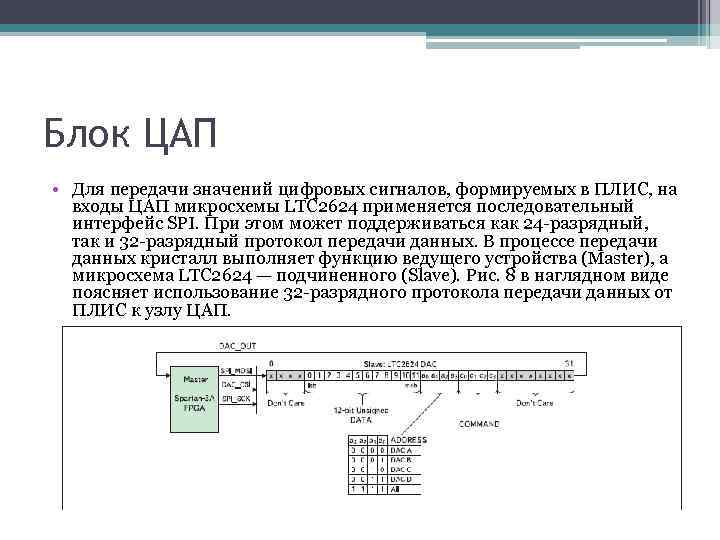

Блок ЦАП • Для передачи значений цифровых сигналов, формируемых в ПЛИС, на входы ЦАП микросхемы LTC 2624 применяется последовательный интерфейс SPI. При этом может поддерживаться как 24 -разрядный, так и 32 -разрядный протокол передачи данных. В процессе передачи данных кристалл выполняет функцию ведущего устройства (Master), а микросхема LTC 2624 — подчиненного (Slave). Рис. 8 в наглядном виде поясняет использование 32 -разрядного протокола передачи данных от ПЛИС к узлу ЦАП.

Блок ЦАП • Для передачи значений цифровых сигналов, формируемых в ПЛИС, на входы ЦАП микросхемы LTC 2624 применяется последовательный интерфейс SPI. При этом может поддерживаться как 24 -разрядный, так и 32 -разрядный протокол передачи данных. В процессе передачи данных кристалл выполняет функцию ведущего устройства (Master), а микросхема LTC 2624 — подчиненного (Slave). Рис. 8 в наглядном виде поясняет использование 32 -разрядного протокола передачи данных от ПЛИС к узлу ЦАП.

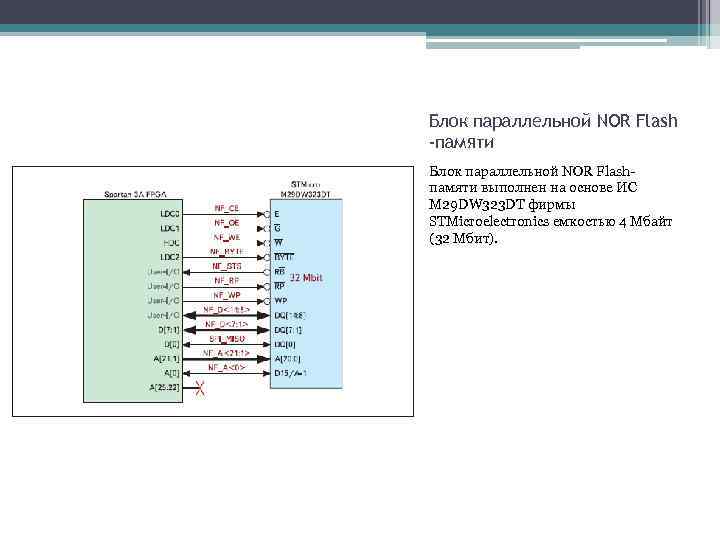

Блок параллельной NOR Flash -памяти Блок параллельной NOR Flashпамяти выполнен на основе ИС M 29 DW 323 DT фирмы STMicroelectronics емкостью 4 Мбайт (32 Мбит).

Блок параллельной NOR Flash -памяти Блок параллельной NOR Flashпамяти выполнен на основе ИС M 29 DW 323 DT фирмы STMicroelectronics емкостью 4 Мбайт (32 Мбит).

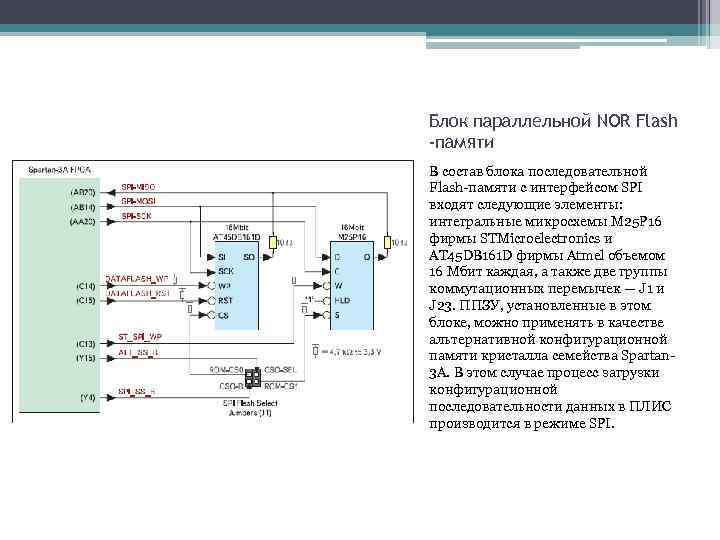

Блок параллельной NOR Flash -памяти В состав блока последовательной Flash-памяти с интерфейсом SPI входят следующие элементы: интегральные микросхемы M 25 P 16 фирмы STMicroelectronics и AT 45 DB 161 D фирмы Atmel объемом 16 Мбит каждая, а также две группы коммутационных перемычек — J 1 и J 23. ППЗУ, установленные в этом блоке, можно применять в качестве альтернативной конфигурационной памяти кристалла семейства Spartan 3 A. В этом случае процесс загрузки конфигурационной последовательности данных в ПЛИС производится в режиме SPI.

Блок параллельной NOR Flash -памяти В состав блока последовательной Flash-памяти с интерфейсом SPI входят следующие элементы: интегральные микросхемы M 25 P 16 фирмы STMicroelectronics и AT 45 DB 161 D фирмы Atmel объемом 16 Мбит каждая, а также две группы коммутационных перемычек — J 1 и J 23. ППЗУ, установленные в этом блоке, можно применять в качестве альтернативной конфигурационной памяти кристалла семейства Spartan 3 A. В этом случае процесс загрузки конфигурационной последовательности данных в ПЛИС производится в режиме SPI.

Перемычки J 1 • После завершения процесса конфигурирования кристалла последовательные Flash ППЗУ могут использоваться для выполнения других функций, например, для хранения исполняемого программного кода встраиваемых микропроцессорных систем, проектируемых на базе 32 -разрядных ядер семейства Micro. Blaze. Кроме того, на основе этих Flash ППЗУ может быть реализована энергонезависимая память данных встраиваемых систем. Выбор одной из микросхем Flash-памяти, используемой в качестве источника конфигурационной последовательности данных в режиме SPI, осуществляется с помощью группы коммутационных перемычек J 1.

Перемычки J 1 • После завершения процесса конфигурирования кристалла последовательные Flash ППЗУ могут использоваться для выполнения других функций, например, для хранения исполняемого программного кода встраиваемых микропроцессорных систем, проектируемых на базе 32 -разрядных ядер семейства Micro. Blaze. Кроме того, на основе этих Flash ППЗУ может быть реализована энергонезависимая память данных встраиваемых систем. Выбор одной из микросхем Flash-памяти, используемой в качестве источника конфигурационной последовательности данных в режиме SPI, осуществляется с помощью группы коммутационных перемычек J 1.

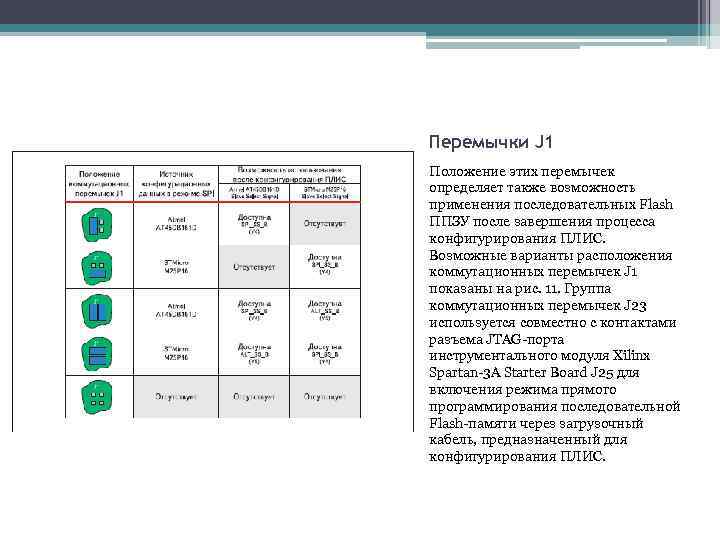

Перемычки J 1 Положение этих перемычек определяет также возможность применения последовательных Flash ППЗУ после завершения процесса конфигурирования ПЛИС. Возможные варианты расположения коммутационных перемычек J 1 показаны на рис. 11. Группа коммутационных перемычек J 23 используется совместно с контактами разъема JTAG-порта инструментального модуля Xilinx Spartan-3 A Starter Board J 25 для включения режима прямого программирования последовательной Flash-памяти через загрузочный кабель, предназначенный для конфигурирования ПЛИС.

Перемычки J 1 Положение этих перемычек определяет также возможность применения последовательных Flash ППЗУ после завершения процесса конфигурирования ПЛИС. Возможные варианты расположения коммутационных перемычек J 1 показаны на рис. 11. Группа коммутационных перемычек J 23 используется совместно с контактами разъема JTAG-порта инструментального модуля Xilinx Spartan-3 A Starter Board J 25 для включения режима прямого программирования последовательной Flash-памяти через загрузочный кабель, предназначенный для конфигурирования ПЛИС.

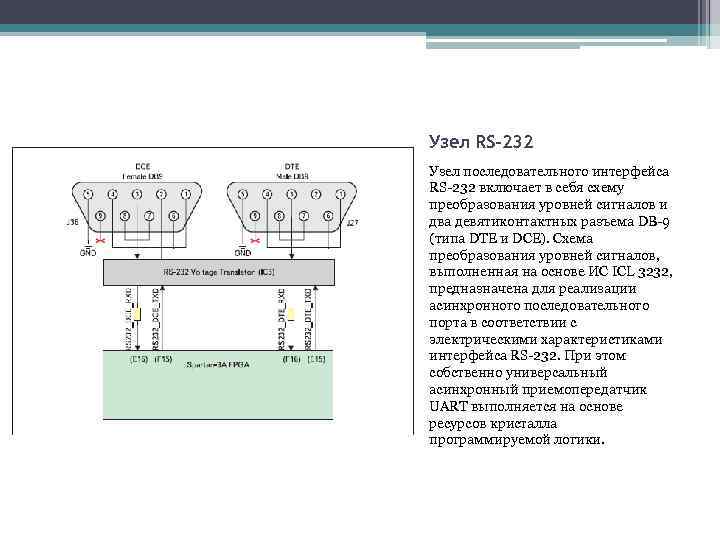

Узел RS-232 Узел последовательного интерфейса RS-232 включает в себя схему преобразования уровней сигналов и два девятиконтактных разъема DB-9 (типа DTE и DCE). Схема преобразования уровней сигналов, выполненная на основе ИС ICL 3232, предназначена для реализации асинхронного последовательного порта в соответствии с электрическими характеристиками интерфейса RS-232. При этом собственно универсальный асинхронный приемопередатчик UART выполняется на основе ресурсов кристалла программируемой логики.

Узел RS-232 Узел последовательного интерфейса RS-232 включает в себя схему преобразования уровней сигналов и два девятиконтактных разъема DB-9 (типа DTE и DCE). Схема преобразования уровней сигналов, выполненная на основе ИС ICL 3232, предназначена для реализации асинхронного последовательного порта в соответствии с электрическими характеристиками интерфейса RS-232. При этом собственно универсальный асинхронный приемопередатчик UART выполняется на основе ресурсов кристалла программируемой логики.

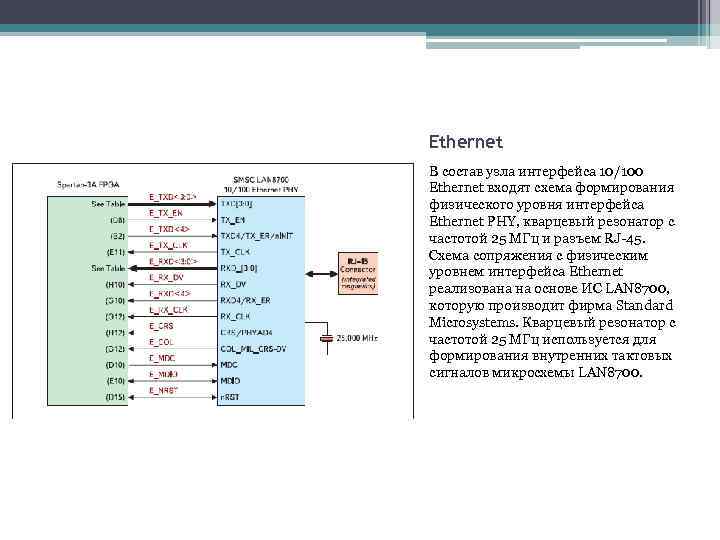

Ethernet В состав узла интерфейса 10/100 Ethernet входят схема формирования физического уровня интерфейса Ethernet PHY, кварцевый резонатор с частотой 25 МГц и разъем RJ-45. Схема сопряжения с физическим уровнем интерфейса Ethernet реализована на основе ИС LAN 8700, которую производит фирма Standard Microsystems. Кварцевый резонатор с частотой 25 МГц используется для формирования внутренних тактовых сигналов микросхемы LAN 8700.

Ethernet В состав узла интерфейса 10/100 Ethernet входят схема формирования физического уровня интерфейса Ethernet PHY, кварцевый резонатор с частотой 25 МГц и разъем RJ-45. Схема сопряжения с физическим уровнем интерфейса Ethernet реализована на основе ИС LAN 8700, которую производит фирма Standard Microsystems. Кварцевый резонатор с частотой 25 МГц используется для формирования внутренних тактовых сигналов микросхемы LAN 8700.

Блок коммутации • Блок коммутации высокоскоростных сигналов состоит из двух разъемов Receive (J 2) и Transmit (J 15), контакты которых соединены с контактами ПЛИС, допускающими их использование для организации ввода/вывода в соответствии с поддерживаемыми дифференциальными цифровыми сигнальными стандартами. Контакты разъема Receive (J 2) предназначены для подключения входных дифференциальных сигналов, а контакты разъема Transmit — для коммутации выходных дифференциальных сигналов. Применение цифровых высокоскоростных дифференциальных сигнальных стандартов ввода/вывода позволяет организовать передачу данных со скоростью, достигающей 600 Мбит/с. Контакты разъемов Receive и Transmit могут использоваться также и для коммутации обычных (однополюсных) сигналов.

Блок коммутации • Блок коммутации высокоскоростных сигналов состоит из двух разъемов Receive (J 2) и Transmit (J 15), контакты которых соединены с контактами ПЛИС, допускающими их использование для организации ввода/вывода в соответствии с поддерживаемыми дифференциальными цифровыми сигнальными стандартами. Контакты разъема Receive (J 2) предназначены для подключения входных дифференциальных сигналов, а контакты разъема Transmit — для коммутации выходных дифференциальных сигналов. Применение цифровых высокоскоростных дифференциальных сигнальных стандартов ввода/вывода позволяет организовать передачу данных со скоростью, достигающей 600 Мбит/с. Контакты разъемов Receive и Transmit могут использоваться также и для коммутации обычных (однополюсных) сигналов.

Питающие напряжения • Комплексная схема формирования и контроля питающих напряжений выполнена на основе двух комбинированных интегральных стабилизаторов LP 3906, выпускаемых фирмой National Semiconductor. Кроме того, в эту схему входят группа коммутационных перемычек J 9 -J 13 и светодиодный индикатор POWER. Каждая микросхема LP 3906 включает в себя два импульсных DC/DC-преобразователя и два линейных стабилизатора с низким падением напряжения на управляющем элементе LDO (Low Drop Out). Для программирования значений выходных напряжений в указанных микросхемах применяют стандартный интерфейс управления I 2 C. В качестве входного напряжения для этих комбинированных стабилизаторов используется напряжение 5 В, поступающее от сетевого адаптера. Наличие в цепи входного напряжения 5 В выключателя POWER, установленного непосредственно на плате, делает более удобной работу с инструментальным модулем.

Питающие напряжения • Комплексная схема формирования и контроля питающих напряжений выполнена на основе двух комбинированных интегральных стабилизаторов LP 3906, выпускаемых фирмой National Semiconductor. Кроме того, в эту схему входят группа коммутационных перемычек J 9 -J 13 и светодиодный индикатор POWER. Каждая микросхема LP 3906 включает в себя два импульсных DC/DC-преобразователя и два линейных стабилизатора с низким падением напряжения на управляющем элементе LDO (Low Drop Out). Для программирования значений выходных напряжений в указанных микросхемах применяют стандартный интерфейс управления I 2 C. В качестве входного напряжения для этих комбинированных стабилизаторов используется напряжение 5 В, поступающее от сетевого адаптера. Наличие в цепи входного напряжения 5 В выключателя POWER, установленного непосредственно на плате, делает более удобной работу с инструментальным модулем.

Блок индикации • Блок индикации инструментального модуля образуют восемь светодиодов, подключенных к пользовательским выводам ПЛИС. Данные светодиодные индикаторы можно использовать в проекте разрабатываемой системы, например, для визуального контроля выполнения алгоритма ее функционирования или в процессе тестирования инструментального модуля.

Блок индикации • Блок индикации инструментального модуля образуют восемь светодиодов, подключенных к пользовательским выводам ПЛИС. Данные светодиодные индикаторы можно использовать в проекте разрабатываемой системы, например, для визуального контроля выполнения алгоритма ее функционирования или в процессе тестирования инструментального модуля.

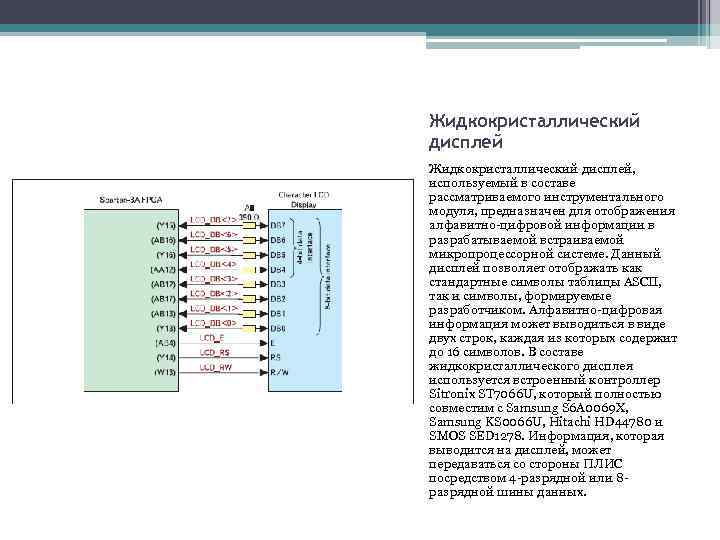

Жидкокристаллический дисплей, используемый в составе рассматриваемого инструментального модуля, предназначен для отображения алфавитно-цифровой информации в разрабатываемой встраиваемой микропроцессорной системе. Данный дисплей позволяет отображать как стандартные символы таблицы ASCII, так и символы, формируемые разработчиком. Алфавитно-цифровая информация может выводиться в виде двух строк, каждая из которых содержит до 16 символов. В составе жидкокристаллического дисплея используется встроенный контроллер Sitronix ST 7066 U, который полностью совместим с Samsung S 6 A 0069 X, Samsung KS 0066 U, Hitachi HD 44780 и SMOS SED 1278. Информация, которая выводится на дисплей, может передаваться со стороны ПЛИС посредством 4 -разрядной или 8 разрядной шины данных.

Жидкокристаллический дисплей, используемый в составе рассматриваемого инструментального модуля, предназначен для отображения алфавитно-цифровой информации в разрабатываемой встраиваемой микропроцессорной системе. Данный дисплей позволяет отображать как стандартные символы таблицы ASCII, так и символы, формируемые разработчиком. Алфавитно-цифровая информация может выводиться в виде двух строк, каждая из которых содержит до 16 символов. В составе жидкокристаллического дисплея используется встроенный контроллер Sitronix ST 7066 U, который полностью совместим с Samsung S 6 A 0069 X, Samsung KS 0066 U, Hitachi HD 44780 и SMOS SED 1278. Информация, которая выводится на дисплей, может передаваться со стороны ПЛИС посредством 4 -разрядной или 8 разрядной шины данных.

Блок переключателей • Блок кнопочных и ползунковых переключателей состоит из четырех кнопок без фиксации и четырех двухпозиционных переключателей, сопряженных с пользовательскими входами ПЛИС. Кнопочные переключатели можно использовать в проектируемых устройствах и системах для выполнения различных функций, например сброса, инициализации, изменения режима. Ползунковые переключатели позволяют устанавливать высокий или низкий логический уровень сигнала на пользовательских входах кристалла, к которым они подключены. Кроме того, к данному блоку можно отнести кнопочный переключатель, совмещенный с инкрементным энкодером, и ползунковый переключатель SUSPEND, предназначенный для перевода ПЛИС XC 3 S 700 A, используемой в инструментальном модуле Xilinx Spartan-3 A Starter Board, в приостановленный режим (режим пониженного потребления).

Блок переключателей • Блок кнопочных и ползунковых переключателей состоит из четырех кнопок без фиксации и четырех двухпозиционных переключателей, сопряженных с пользовательскими входами ПЛИС. Кнопочные переключатели можно использовать в проектируемых устройствах и системах для выполнения различных функций, например сброса, инициализации, изменения режима. Ползунковые переключатели позволяют устанавливать высокий или низкий логический уровень сигнала на пользовательских входах кристалла, к которым они подключены. Кроме того, к данному блоку можно отнести кнопочный переключатель, совмещенный с инкрементным энкодером, и ползунковый переключатель SUSPEND, предназначенный для перевода ПЛИС XC 3 S 700 A, используемой в инструментальном модуле Xilinx Spartan-3 A Starter Board, в приостановленный режим (режим пониженного потребления).

Отладочный порт • Отладочный порт выполнен в виде контактных площадок на верхней стороне платы инструментального модуля, предназначенных для подключения соответствующего разъема логического анализатора, который используется совместно с пакетом средств аппаратной внутрикристальной отладки Xilinx Chip. Scope Pro.

Отладочный порт • Отладочный порт выполнен в виде контактных площадок на верхней стороне платы инструментального модуля, предназначенных для подключения соответствующего разъема логического анализатора, который используется совместно с пакетом средств аппаратной внутрикристальной отладки Xilinx Chip. Scope Pro.

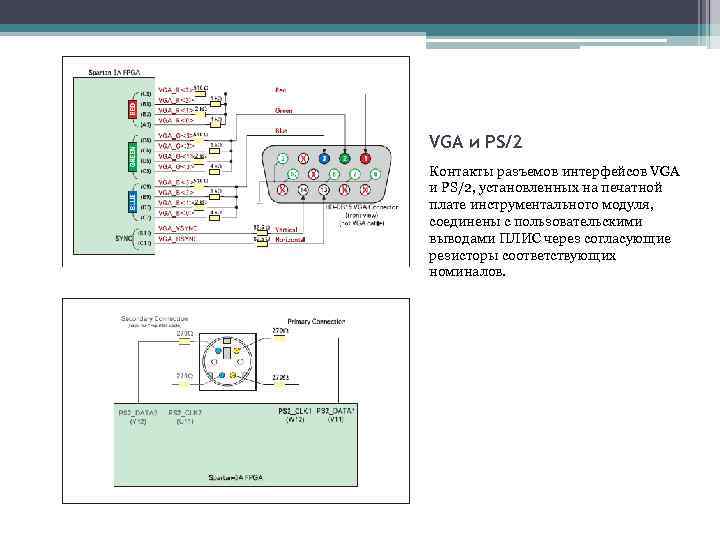

VGA и PS/2 Контакты разъемов интерфейсов VGA и PS/2, установленных на печатной плате инструментального модуля, соединены с пользовательскими выводами ПЛИС через согласующие резисторы соответствующих номиналов.

VGA и PS/2 Контакты разъемов интерфейсов VGA и PS/2, установленных на печатной плате инструментального модуля, соединены с пользовательскими выводами ПЛИС через согласующие резисторы соответствующих номиналов.

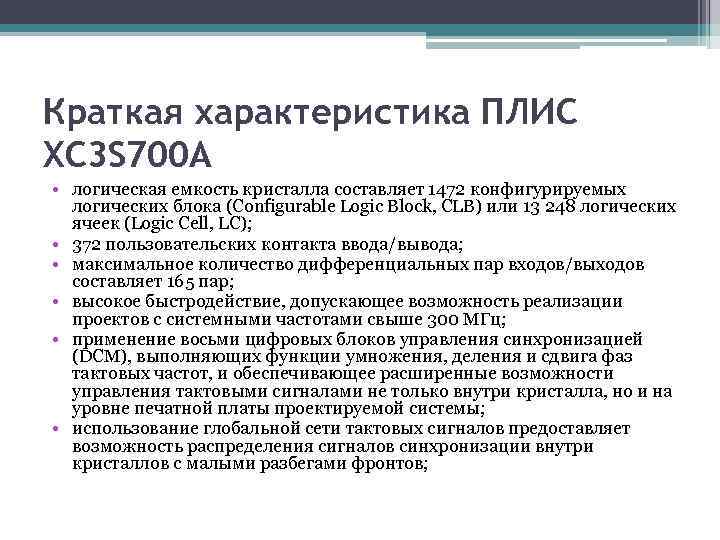

Краткая характеристика ПЛИС XC 3 S 700 A • логическая емкость кристалла составляет 1472 конфигурируемых логических блока (Configurable Logic Block, CLB) или 13 248 логических ячеек (Logic Cell, LC); • 372 пользовательских контакта ввода/вывода; • максимальное количество дифференциальных пар входов/выходов составляет 165 пар; • высокое быстродействие, допускающее возможность реализации проектов с системными частотами свыше 300 МГц; • применение восьми цифровых блоков управления синхронизацией (DCM), выполняющих функции умножения, деления и сдвига фаз тактовых частот, и обеспечивающее расширенные возможности управления тактовыми сигналами не только внутри кристалла, но и на уровне печатной платы проектируемой системы; • использование глобальной сети тактовых сигналов предоставляет возможность распределения сигналов синхронизации внутри кристаллов с малыми разбегами фронтов;

Краткая характеристика ПЛИС XC 3 S 700 A • логическая емкость кристалла составляет 1472 конфигурируемых логических блока (Configurable Logic Block, CLB) или 13 248 логических ячеек (Logic Cell, LC); • 372 пользовательских контакта ввода/вывода; • максимальное количество дифференциальных пар входов/выходов составляет 165 пар; • высокое быстродействие, допускающее возможность реализации проектов с системными частотами свыше 300 МГц; • применение восьми цифровых блоков управления синхронизацией (DCM), выполняющих функции умножения, деления и сдвига фаз тактовых частот, и обеспечивающее расширенные возможности управления тактовыми сигналами не только внутри кристалла, но и на уровне печатной платы проектируемой системы; • использование глобальной сети тактовых сигналов предоставляет возможность распределения сигналов синхронизации внутри кристаллов с малыми разбегами фронтов;

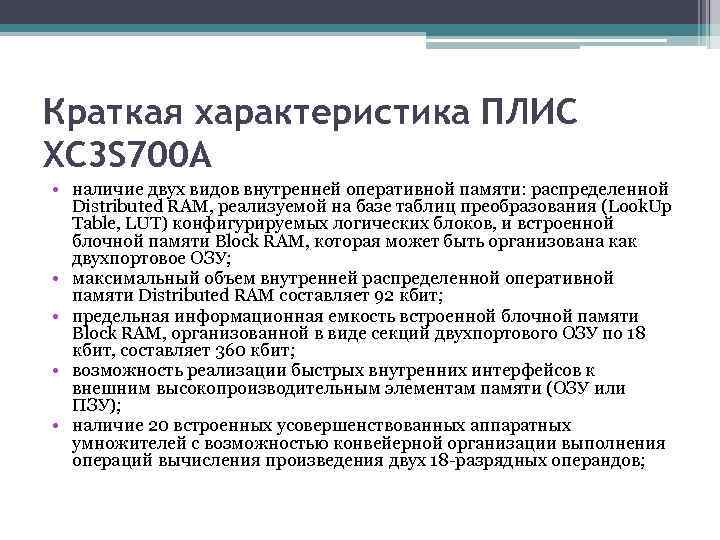

Краткая характеристика ПЛИС XC 3 S 700 A • наличие двух видов внутренней оперативной памяти: распределенной Distributed RAM, реализуемой на базе таблиц преобразования (Look. Up Table, LUT) конфигурируемых логических блоков, и встроенной блочной памяти Block RAM, которая может быть организована как двухпортовое ОЗУ; • максимальный объем внутренней распределенной оперативной памяти Distributed RAM составляет 92 кбит; • предельная информационная емкость встроенной блочной памяти Block RAM, организованной в виде секций двухпортового ОЗУ по 18 кбит, составляет 360 кбит; • возможность реализации быстрых внутренних интерфейсов к внешним высокопроизводительным элементам памяти (ОЗУ или ПЗУ); • наличие 20 встроенных усовершенствованных аппаратных умножителей с возможностью конвейерной организации выполнения операций вычисления произведения двух 18 -разрядных операндов;

Краткая характеристика ПЛИС XC 3 S 700 A • наличие двух видов внутренней оперативной памяти: распределенной Distributed RAM, реализуемой на базе таблиц преобразования (Look. Up Table, LUT) конфигурируемых логических блоков, и встроенной блочной памяти Block RAM, которая может быть организована как двухпортовое ОЗУ; • максимальный объем внутренней распределенной оперативной памяти Distributed RAM составляет 92 кбит; • предельная информационная емкость встроенной блочной памяти Block RAM, организованной в виде секций двухпортового ОЗУ по 18 кбит, составляет 360 кбит; • возможность реализации быстрых внутренних интерфейсов к внешним высокопроизводительным элементам памяти (ОЗУ или ПЗУ); • наличие 20 встроенных усовершенствованных аппаратных умножителей с возможностью конвейерной организации выполнения операций вычисления произведения двух 18 -разрядных операндов;

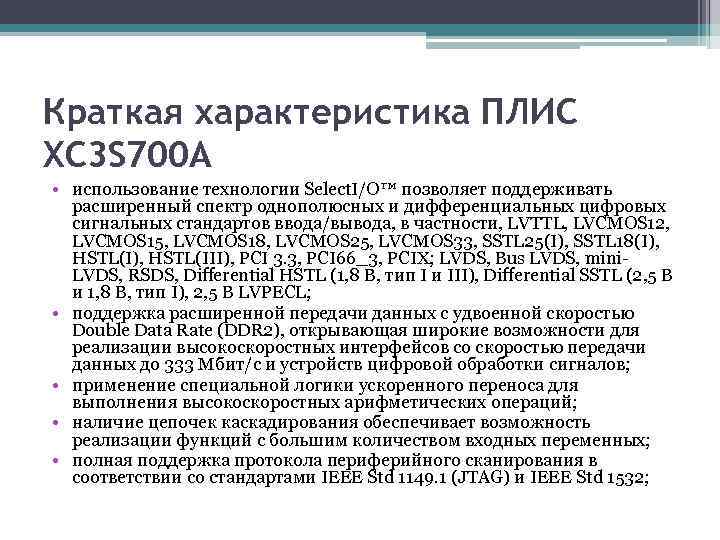

Краткая характеристика ПЛИС XC 3 S 700 A • использование технологии Select. I/O™ позволяет поддерживать расширенный спектр однополюсных и дифференциальных цифровых сигнальных стандартов ввода/вывода, в частности, LVTTL, LVCMOS 12, LVCMOS 15, LVCMOS 18, LVCMOS 25, LVCMOS 33, SSTL 25(I), SSTL 18(I), HSTL(I), HSTL(III), PCI 3. 3, PCI 66_3, PCIX; LVDS, Bus LVDS, mini. LVDS, RSDS, Differential HSTL (1, 8 В, тип I и III), Differential SSTL (2, 5 В и 1, 8 В, тип I), 2, 5 В LVPECL; • поддержка расширенной передачи данных с удвоенной скоростью Double Data Rate (DDR 2), открывающая широкие возможности для реализации высокоскоростных интерфейсов со скоростью передачи данных до 333 Мбит/с и устройств цифровой обработки сигналов; • применение специальной логики ускоренного переноса для выполнения высокоскоростных арифметических операций; • наличие цепочек каскадирования обеспечивает возможность реализации функций с большим количеством входных переменных; • полная поддержка протокола периферийного сканирования в соответствии со стандартами IEEE Std 1149. 1 (JTAG) и IEEE Std 1532;

Краткая характеристика ПЛИС XC 3 S 700 A • использование технологии Select. I/O™ позволяет поддерживать расширенный спектр однополюсных и дифференциальных цифровых сигнальных стандартов ввода/вывода, в частности, LVTTL, LVCMOS 12, LVCMOS 15, LVCMOS 18, LVCMOS 25, LVCMOS 33, SSTL 25(I), SSTL 18(I), HSTL(I), HSTL(III), PCI 3. 3, PCI 66_3, PCIX; LVDS, Bus LVDS, mini. LVDS, RSDS, Differential HSTL (1, 8 В, тип I и III), Differential SSTL (2, 5 В и 1, 8 В, тип I), 2, 5 В LVPECL; • поддержка расширенной передачи данных с удвоенной скоростью Double Data Rate (DDR 2), открывающая широкие возможности для реализации высокоскоростных интерфейсов со скоростью передачи данных до 333 Мбит/с и устройств цифровой обработки сигналов; • применение специальной логики ускоренного переноса для выполнения высокоскоростных арифметических операций; • наличие цепочек каскадирования обеспечивает возможность реализации функций с большим количеством входных переменных; • полная поддержка протокола периферийного сканирования в соответствии со стандартами IEEE Std 1149. 1 (JTAG) и IEEE Std 1532;

Краткая характеристика ПЛИС XC 3 S 700 A • наличие уникального идентификационного кода DNA у каждого кристалла, существенно упрощающего защиту прав интеллектуальной собственности; • возможность использования в качестве конфигурационного ППЗУ широкого спектра недорогой Flash-памяти с различными интерфейсами; • неограниченное количество циклов загрузки конфигурационных данных; • поддержка шести режимов конфигурирования ПЛИС (Master Serial, Slave Parallel, JTAG, Serial Peripheral Interface, Byte Peripheral Interface Up); • низкая стоимость в сочетании с высокой производительностью, позволяющая использовать данный тип ПЛИС для реализации серийно выпускаемых устройств и систем.

Краткая характеристика ПЛИС XC 3 S 700 A • наличие уникального идентификационного кода DNA у каждого кристалла, существенно упрощающего защиту прав интеллектуальной собственности; • возможность использования в качестве конфигурационного ППЗУ широкого спектра недорогой Flash-памяти с различными интерфейсами; • неограниченное количество циклов загрузки конфигурационных данных; • поддержка шести режимов конфигурирования ПЛИС (Master Serial, Slave Parallel, JTAG, Serial Peripheral Interface, Byte Peripheral Interface Up); • низкая стоимость в сочетании с высокой производительностью, позволяющая использовать данный тип ПЛИС для реализации серийно выпускаемых устройств и систем.

Краткая характеристика ПЛИС XC 3 S 700 A • В состав архитектуры кристаллов Spartan-3 A XC 3 S 700 A входят те же структурные элементы, что и в ПЛИС семейств Spartan-3 и Spartan-3 Е. Основное отличие кристаллов семейства Spartan-3 A проявляется в оптимизированном расположении программируемых блоков ввода/вывода (Input/Output block, IOB). Более подробное описание архитектуры и особенностей кристаллов семейства Spartan-3 A можно найти в [14, 15].

Краткая характеристика ПЛИС XC 3 S 700 A • В состав архитектуры кристаллов Spartan-3 A XC 3 S 700 A входят те же структурные элементы, что и в ПЛИС семейств Spartan-3 и Spartan-3 Е. Основное отличие кристаллов семейства Spartan-3 A проявляется в оптимизированном расположении программируемых блоков ввода/вывода (Input/Output block, IOB). Более подробное описание архитектуры и особенностей кристаллов семейства Spartan-3 A можно найти в [14, 15].

Литература • • • • Зотов В. Инструментальный комплект Spartan-3 Starter Kit для практического освоения методов проектирования встраиваемых микропроцессорных систем на основе ПЛИС семейств FPGA фирмы Xilinx // Компоненты и технологии. 2005. № 7. Зотов В. Новый инструментальный комплект Spartan-3 E Starter Kit для практического освоения методов проектирования встраиваемых микропроцессорных систем на основе ПЛИС семейств FPGA фирмы Xilinx // Компоненты и технологии. 2006. № 10. Зотов В. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx. М. : Горячая линия — Телеком, 2006. Зотов В. Pico. Blaze — семейство 8 -разрядных микропроцессорных ядер, реализуемых на основе ПЛИС фирмы Xilinx // Компоненты и технологии. 2003. № 4. Зотов В. Система команд микропроцессорного ядра Pico. Blaze, реализуемого на основе ПЛИС семейств Spartan-II, Spartan-IIE, Virtex-E // Компоненты и технологии. 2003. № 5. Зотов В. Особенности микропроцессорного ядра Pico. Blaze, предназначенного для применения в проектах, реализуемых на основе ПЛИС семейства Virtex-II // Компоненты и технологии. 2003. № 6. Зотов В. Особенности микропроцессорного ядра Pico. Blaze, предназначенного для применения в проектах, реализуемых на основе ПЛИС семейства Cool. Runner-II // Компоненты и технологии. 2003. № 7. Зотов В. Особенности микропроцессорного ядра Pico. Blaze, предназначенного для применения в проектах, реализуемых на основе ПЛИС семейств Spartan-3, Virtex-II и Virtex-IIPRO // Компоненты и технологии. 2005. № 5– 6. Зотов В. Micro. Blaze — семейство 32 -разрядных микропроцессорных ядер, реализуемых на основе ПЛИС фирмы Xilinx // Компоненты и технологии. 2003. № 9. Зотов В. Система команд микропроцессорного ядра Micro. Blaze // Компоненты и технологии. 2004. № 1– 3. Зотов В. Организация памяти микропроцессорного ядра Micro. Blaze // Компоненты и технологии. 2004. № 5. Зотов В. Embedded Development Kit — система проектирования встраиваемых микропроцессорных систем на основе ПЛИС серий FPGA фирмы Xilinx // Компоненты и технологии. 2004. № 4. Зотов В. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР Web. Pack ISE. М. : Горячая линия–Телеком, 2003. Spartan-3 A FPGA Family: Data Sheet. Xilinx, 2007. Spartan-3 Generation FPGA: User Guide. Xilinx, 2007.

Литература • • • • Зотов В. Инструментальный комплект Spartan-3 Starter Kit для практического освоения методов проектирования встраиваемых микропроцессорных систем на основе ПЛИС семейств FPGA фирмы Xilinx // Компоненты и технологии. 2005. № 7. Зотов В. Новый инструментальный комплект Spartan-3 E Starter Kit для практического освоения методов проектирования встраиваемых микропроцессорных систем на основе ПЛИС семейств FPGA фирмы Xilinx // Компоненты и технологии. 2006. № 10. Зотов В. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx. М. : Горячая линия — Телеком, 2006. Зотов В. Pico. Blaze — семейство 8 -разрядных микропроцессорных ядер, реализуемых на основе ПЛИС фирмы Xilinx // Компоненты и технологии. 2003. № 4. Зотов В. Система команд микропроцессорного ядра Pico. Blaze, реализуемого на основе ПЛИС семейств Spartan-II, Spartan-IIE, Virtex-E // Компоненты и технологии. 2003. № 5. Зотов В. Особенности микропроцессорного ядра Pico. Blaze, предназначенного для применения в проектах, реализуемых на основе ПЛИС семейства Virtex-II // Компоненты и технологии. 2003. № 6. Зотов В. Особенности микропроцессорного ядра Pico. Blaze, предназначенного для применения в проектах, реализуемых на основе ПЛИС семейства Cool. Runner-II // Компоненты и технологии. 2003. № 7. Зотов В. Особенности микропроцессорного ядра Pico. Blaze, предназначенного для применения в проектах, реализуемых на основе ПЛИС семейств Spartan-3, Virtex-II и Virtex-IIPRO // Компоненты и технологии. 2005. № 5– 6. Зотов В. Micro. Blaze — семейство 32 -разрядных микропроцессорных ядер, реализуемых на основе ПЛИС фирмы Xilinx // Компоненты и технологии. 2003. № 9. Зотов В. Система команд микропроцессорного ядра Micro. Blaze // Компоненты и технологии. 2004. № 1– 3. Зотов В. Организация памяти микропроцессорного ядра Micro. Blaze // Компоненты и технологии. 2004. № 5. Зотов В. Embedded Development Kit — система проектирования встраиваемых микропроцессорных систем на основе ПЛИС серий FPGA фирмы Xilinx // Компоненты и технологии. 2004. № 4. Зотов В. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР Web. Pack ISE. М. : Горячая линия–Телеком, 2003. Spartan-3 A FPGA Family: Data Sheet. Xilinx, 2007. Spartan-3 Generation FPGA: User Guide. Xilinx, 2007.