Презентация lec01 my

- Размер: 1.4 Mегабайта

- Количество слайдов: 33

Описание презентации Презентация lec01 my по слайдам

Проектирование стандартных элементов цифровых интегральных схем. Основы HDL VERILOG Ильин Сергей, vermut. 42@gmail. com

Проектирование стандартных элементов цифровых интегральных схем. Основы HDL VERILOG Ильин Сергей, vermut. 42@gmail. com

Классификация микросхем по элементной базе • биполярные ( ЭСЛ, ТТЛ) ; • полевые ( n. M ОП, p МОП, к. МОП) ; • смешанные (Би. КМОП) ;

Классификация микросхем по элементной базе • биполярные ( ЭСЛ, ТТЛ) ; • полевые ( n. M ОП, p МОП, к. МОП) ; • смешанные (Би. КМОП) ;

ЭСЛ Эмиттерно связная логика – переключатели тока. Построенные на основе дифференциальных каскадов, схемы обладают очень высоким быстродействием за счет того что транзисторы находятся в нормально активном режиме, но при этом очень низкая помехозащищенностью.

ЭСЛ Эмиттерно связная логика – переключатели тока. Построенные на основе дифференциальных каскадов, схемы обладают очень высоким быстродействием за счет того что транзисторы находятся в нормально активном режиме, но при этом очень низкая помехозащищенностью.

ТТЛ Разновидность цифровых логических микросхем, построенная с применение биполярных n-p-n транзисторов. Обладает средним быстродействием и энергопотреблением. Для повышения быстродействия применяются транзисторы с диодами Шоттки.

ТТЛ Разновидность цифровых логических микросхем, построенная с применение биполярных n-p-n транзисторов. Обладает средним быстродействием и энергопотреблением. Для повышения быстродействия применяются транзисторы с диодами Шоттки.

p. МОП Разновидность цифровых логических микросхем, построенная с применение только p-канального транзистора. Обладает средним быстродействием и энергопотреблением

p. МОП Разновидность цифровых логических микросхем, построенная с применение только p-канального транзистора. Обладает средним быстродействием и энергопотреблением

n. МОП Разновидность цифровых логических микросхем, построенная с применение только n-канального транзистора. Обладает средним быстродействием и энергопотреблением

n. МОП Разновидность цифровых логических микросхем, построенная с применение только n-канального транзистора. Обладает средним быстродействием и энергопотреблением

КМОП Комплементарная логика построенная на МОП транзисторах обоих типов проводимости Обладает низким энергопотреблением в статическом режиме и высоким быстродействием

КМОП Комплементарная логика построенная на МОП транзисторах обоих типов проводимости Обладает низким энергопотреблением в статическом режиме и высоким быстродействием

Би. КМОП Разновидность цифровых логических микросхем, построенная с применение МОП транзисторов проводимости двух типов и биполярного транзистора n-p-n или p-n-p типа.

Би. КМОП Разновидность цифровых логических микросхем, построенная с применение МОП транзисторов проводимости двух типов и биполярного транзистора n-p-n или p-n-p типа.

Классификация микросхем по способу проектирования • Полузаказные ИС ; • Заказные ИС

Классификация микросхем по способу проектирования • Полузаказные ИС ; • Заказные ИС

Полузаказные ИС — предназначены для средне- и мало-серийного производства. Технологический цикл их разработки и изготовления разбит на несколько этапов. К полузаказным относят СБИС на таких полуфабрикатах, как транзисторные матрицы, вентильные матрицы, матрицы стандартных ячеек (Gate Array-based ASICs), ПЗУ, программируемые логические матрицы (ПЛМ), программируемые матрицы логики (Programmable ASICs).

Полузаказные ИС — предназначены для средне- и мало-серийного производства. Технологический цикл их разработки и изготовления разбит на несколько этапов. К полузаказным относят СБИС на таких полуфабрикатах, как транзисторные матрицы, вентильные матрицы, матрицы стандартных ячеек (Gate Array-based ASICs), ПЗУ, программируемые логические матрицы (ПЛМ), программируемые матрицы логики (Programmable ASICs).

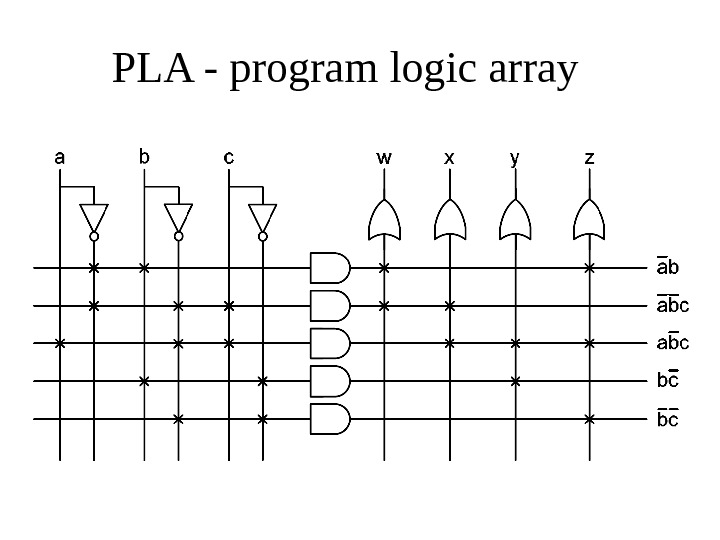

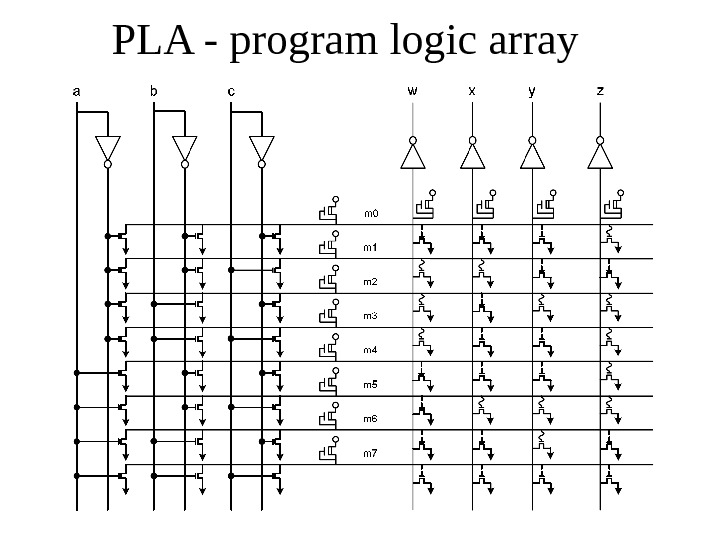

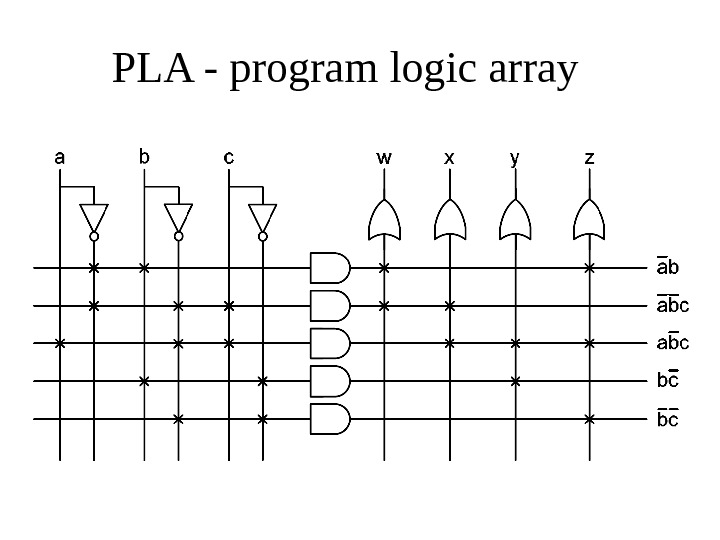

PLA — program logic array, программируемый массив логики — PLA и PLM в русскоязычной литературе не различались и обозначились как ПЛМ. Отличаются доступностью программирования внутренней структуры (матриц) ПЛМ

PLA — program logic array, программируемый массив логики — PLA и PLM в русскоязычной литературе не различались и обозначились как ПЛМ. Отличаются доступностью программирования внутренней структуры (матриц) ПЛМ

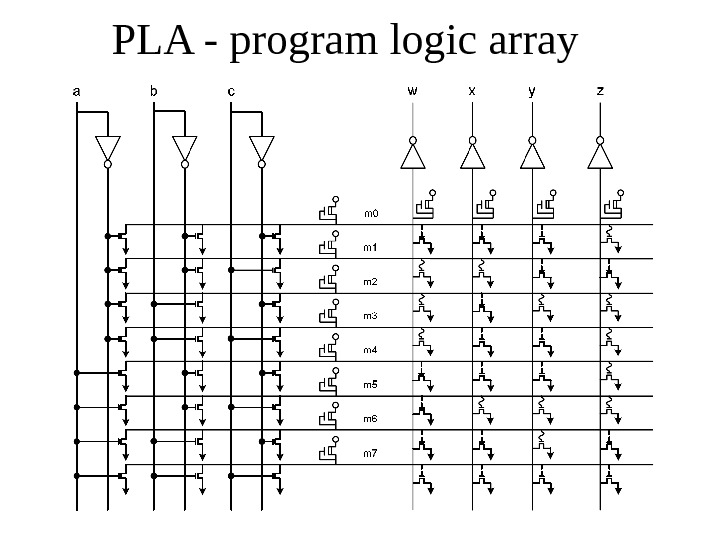

PLA — program logic array

PLA — program logic array

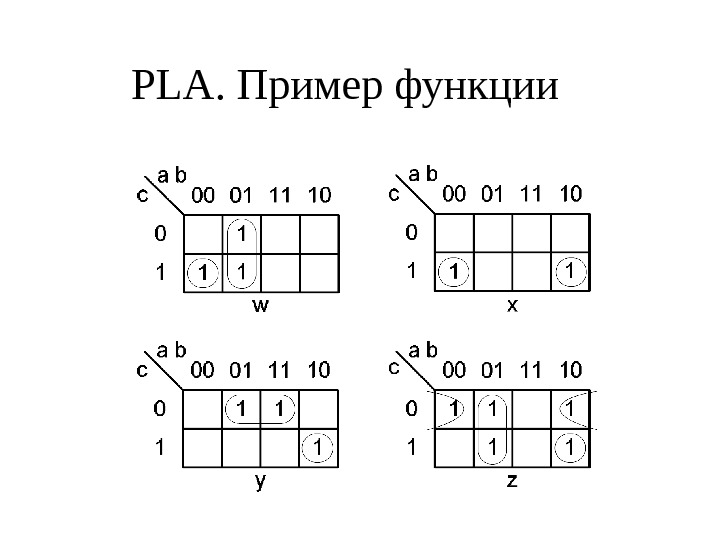

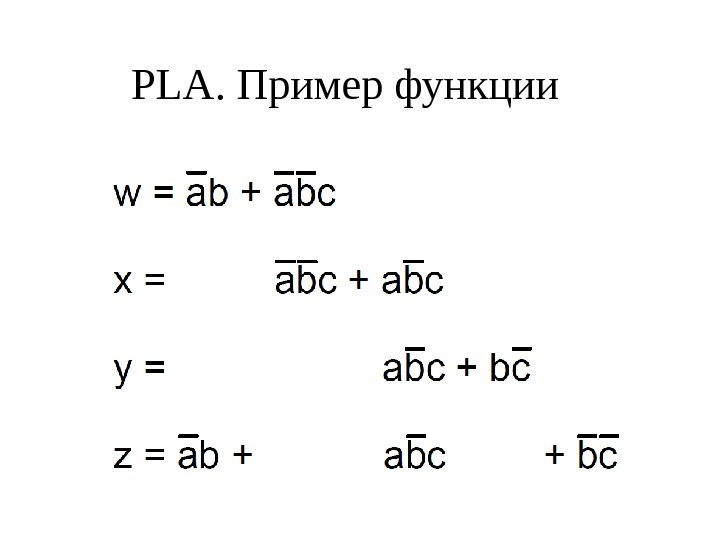

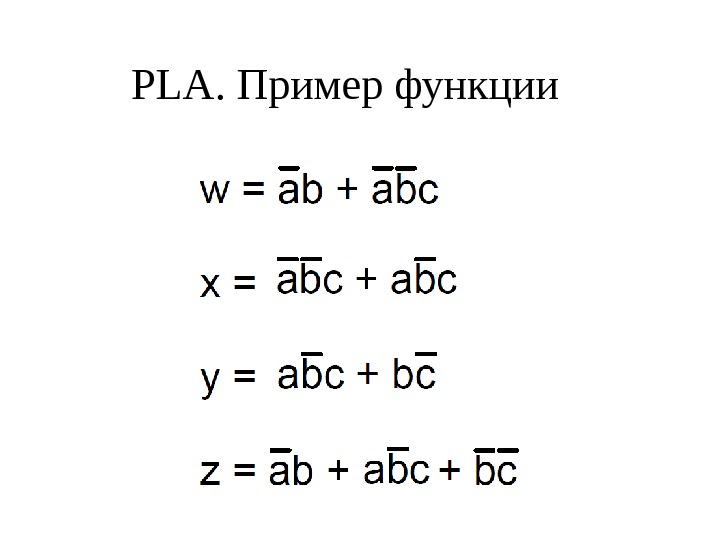

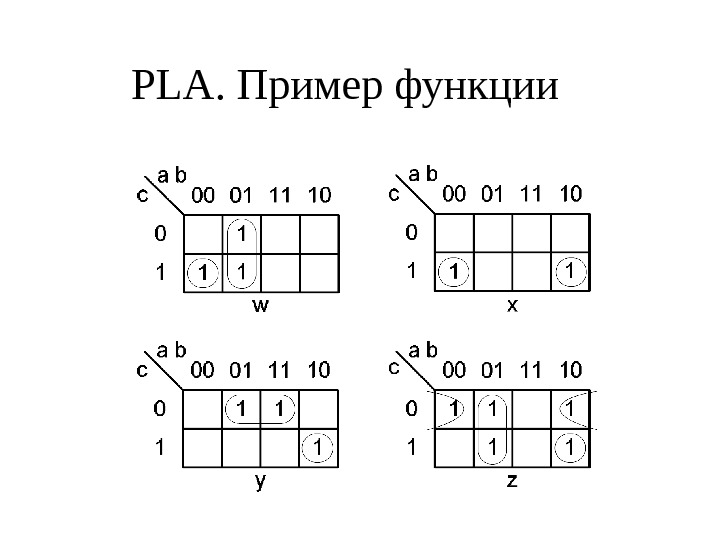

PLA. Пример функции

PLA. Пример функции

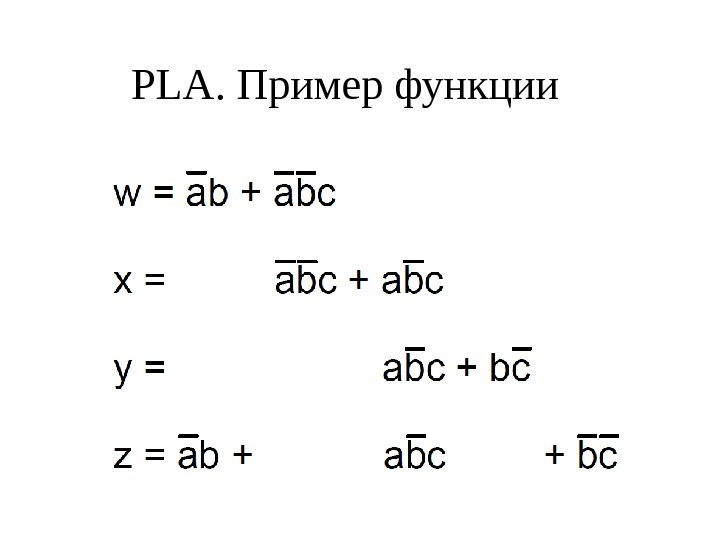

PLA. Пример функции

PLA. Пример функции

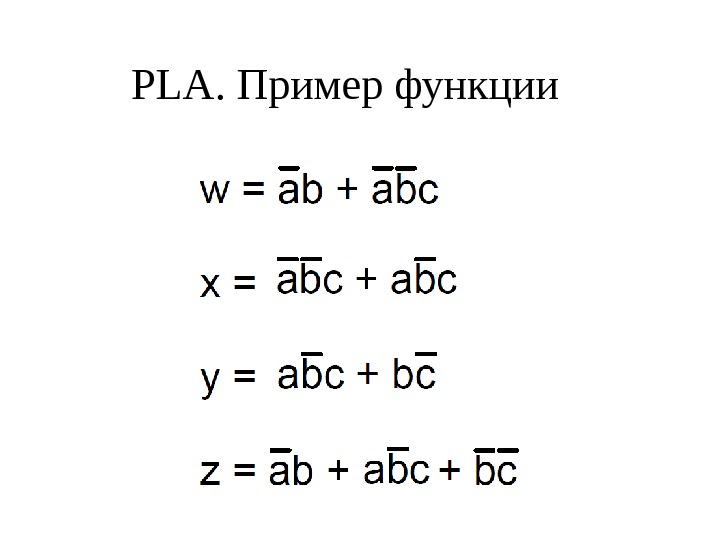

PLA. Пример функции

PLA. Пример функции

PLA — program logic array

PLA — program logic array

CPLD – complex programmable logic device, сложные программируемые логические устройства содержат включают в себя крупные программируемые логические блоки — макроячейки, соединённые с внешними выводами и внутренними шинами. Зашивка хранится в энергонезависимой памяти. При зашивки больших схем применяются несколько микросхем.

CPLD – complex programmable logic device, сложные программируемые логические устройства содержат включают в себя крупные программируемые логические блоки — макроячейки, соединённые с внешними выводами и внутренними шинами. Зашивка хранится в энергонезависимой памяти. При зашивки больших схем применяются несколько микросхем.

FPGA — field programmable gate array, дополнительно включает блоки умножения-суммирования, а также логические элементы (LUT) и их блоки коммутации. FPGA имеют больше логических элементов и более гибкую архитектуру, чем CPLD. Зашивка для FPGA хранится в распределённой памяти, которая может быть выполнена как на основе энергозависимых ячеек так и статического или перемычек antifuse.

FPGA — field programmable gate array, дополнительно включает блоки умножения-суммирования, а также логические элементы (LUT) и их блоки коммутации. FPGA имеют больше логических элементов и более гибкую архитектуру, чем CPLD. Зашивка для FPGA хранится в распределённой памяти, которая может быть выполнена как на основе энергозависимых ячеек так и статического или перемычек antifuse.

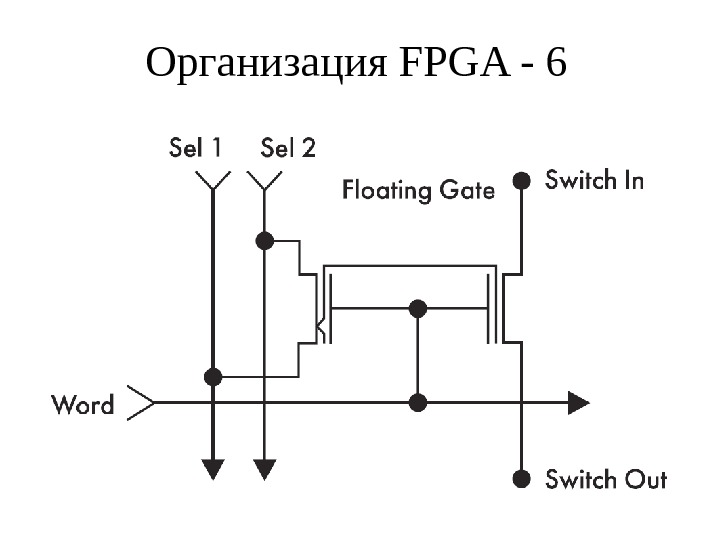

Способы хранения зашивки FPGA — принцип статического ОЗУ (SRAM) – информация храниться во внутреннем “теневом” ОЗУ, а инициализация осуществляется из внешнего массива памяти

Способы хранения зашивки FPGA — принцип статического ОЗУ (SRAM) – информация храниться во внутреннем “теневом” ОЗУ, а инициализация осуществляется из внешнего массива памяти

— FLASH-память – конфигурация сохраняется во внутренней энергонезависимой памяти и в любой момент может быть перезагружена. Срок хранения конфигурации – 10 лет. Способы хранения зашивки FPG

— FLASH-память – конфигурация сохраняется во внутренней энергонезависимой памяти и в любой момент может быть перезагружена. Срок хранения конфигурации – 10 лет. Способы хранения зашивки FPG

— электрически однократно программируемые логические схемы (PROM) программируются до установки в систему, энергонезависимы и занимают промежуточное положение между ПЛИС и полузаказными БИС на основе базовых матричных кристаллов (БМК). Способы хранения зашивки FPG

— электрически однократно программируемые логические схемы (PROM) программируются до установки в систему, энергонезависимы и занимают промежуточное положение между ПЛИС и полузаказными БИС на основе базовых матричных кристаллов (БМК). Способы хранения зашивки FPG

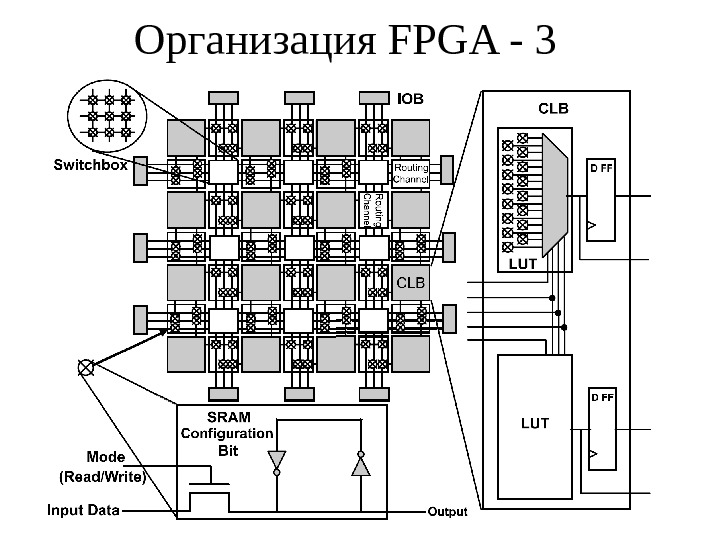

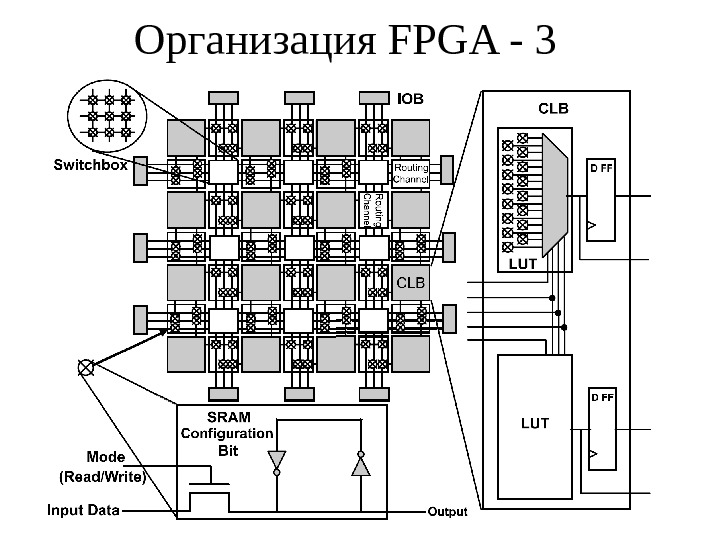

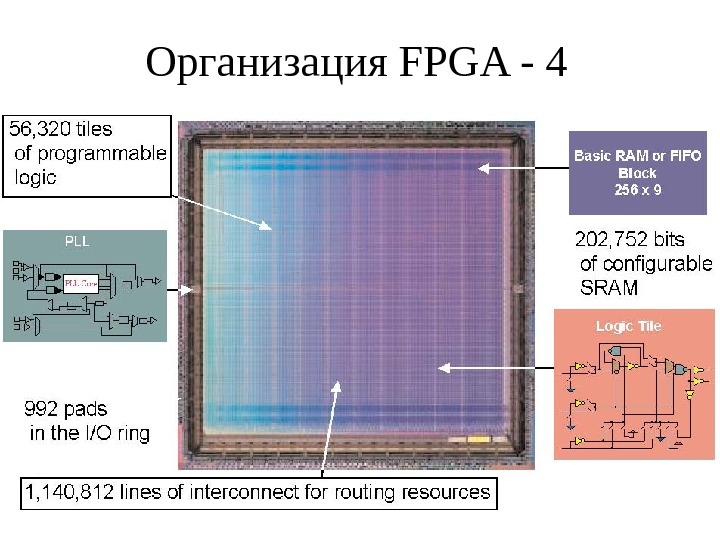

Организация FPGA — 1 В основе структуры FPGA лежат конфигурируемые логические блоки CLB ( configurable logic blocks ). В свою очередь каждый CLB содержит четыре одинаковые части, каждая из которых содержит два блока памяти RAM – LUT ( look up tables ), которые используются для придания блоку определенной функции.

Организация FPGA — 1 В основе структуры FPGA лежат конфигурируемые логические блоки CLB ( configurable logic blocks ). В свою очередь каждый CLB содержит четыре одинаковые части, каждая из которых содержит два блока памяти RAM – LUT ( look up tables ), которые используются для придания блоку определенной функции.

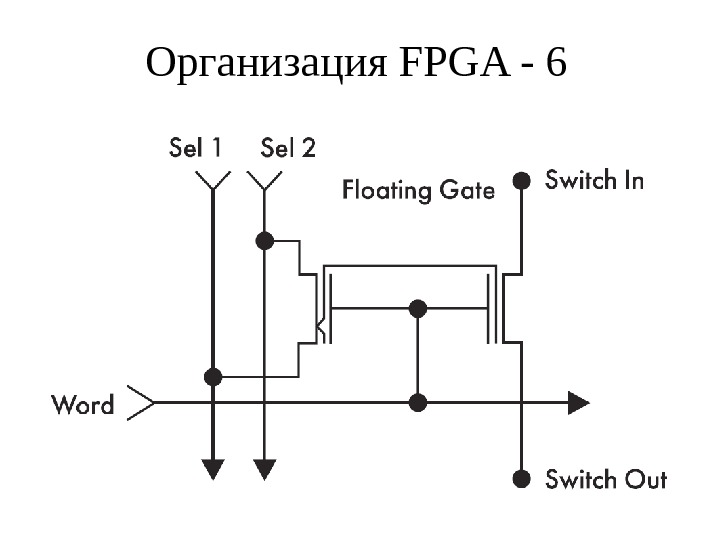

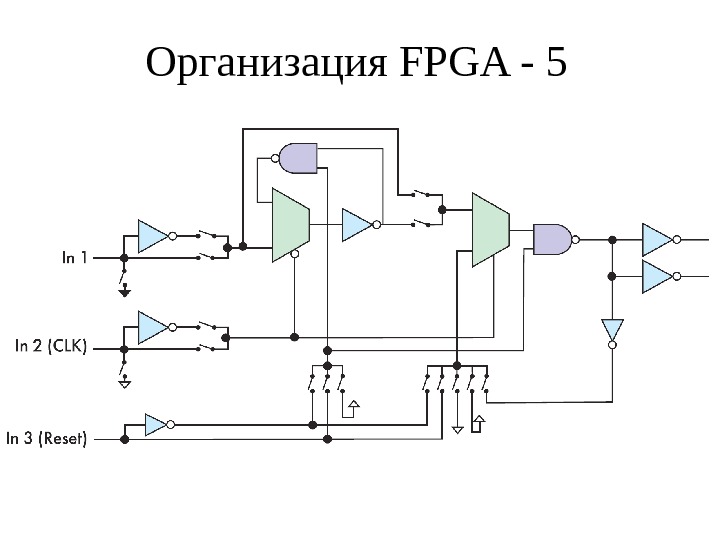

Организация FPGA —

Организация FPGA —

Организация FPGA —

Организация FPGA —

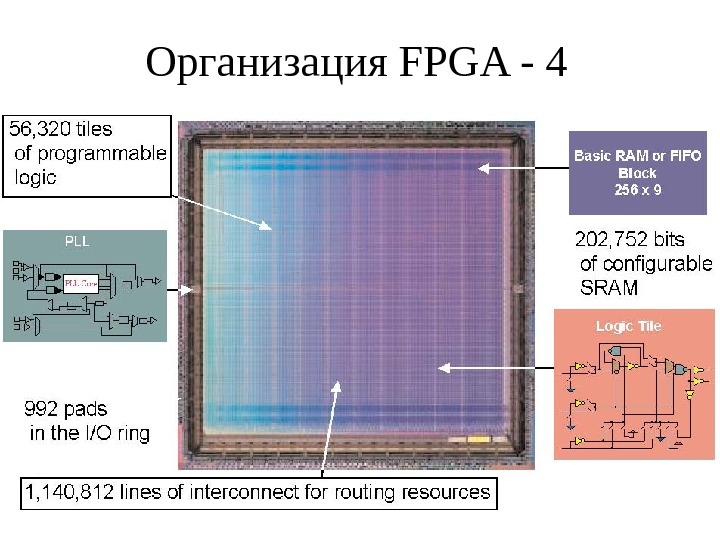

Организация FPGA —

Организация FPGA —

Организация FPGA —

Организация FPGA —

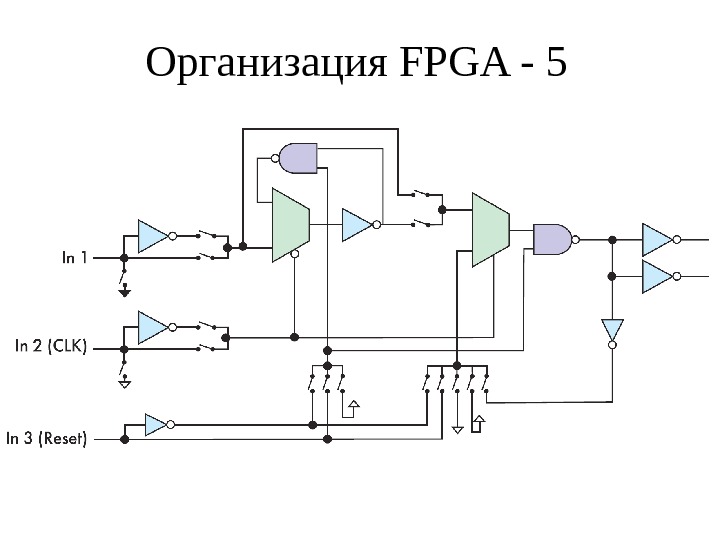

Организация FPGA —

Организация FPGA —

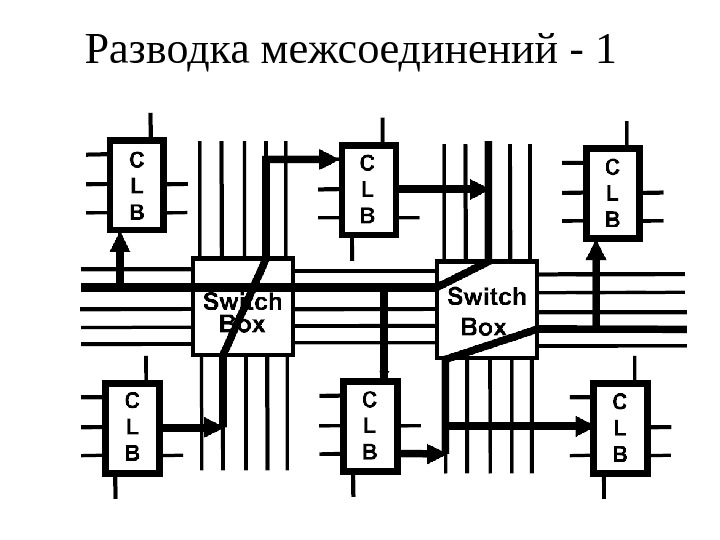

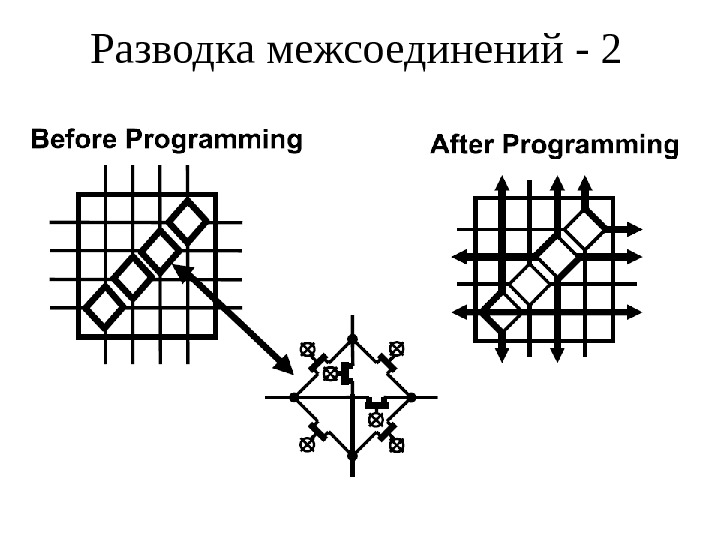

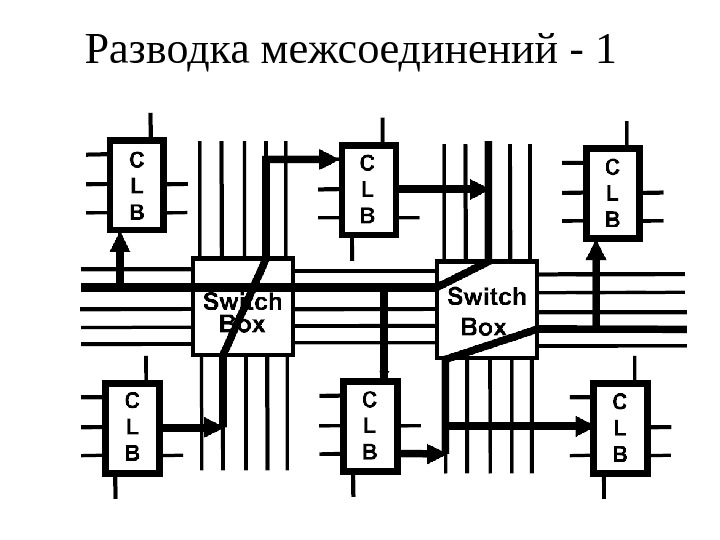

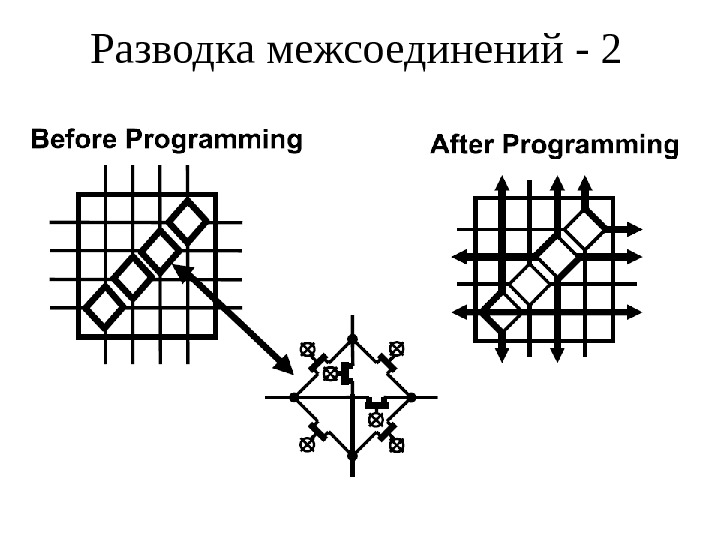

Разводка межсоединений —

Разводка межсоединений —

Разводка межсоединений —

Разводка межсоединений —

БМК Базовый Матричный Кристалл – полузаказная ИС, функция зашивается на технологическом этапе металлизации. По сравнению с предыдущим классом имеет более массовое производство и более низкую себестоимость.

БМК Базовый Матричный Кристалл – полузаказная ИС, функция зашивается на технологическом этапе металлизации. По сравнению с предыдущим классом имеет более массовое производство и более низкую себестоимость.

Организация БМК

Организация БМК

Заказные ИС Заказная ИС (Full-custom ASICs) — архитектура схемы, структура кристалла на уровне транзисторов определяются индивидуальным заказом потребителя. Все фотошаблоны определяются заказчиком. Получение схемы проводится путем полного проведения технологического маршрута.

Заказные ИС Заказная ИС (Full-custom ASICs) — архитектура схемы, структура кристалла на уровне транзисторов определяются индивидуальным заказом потребителя. Все фотошаблоны определяются заказчиком. Получение схемы проводится путем полного проведения технологического маршрута.

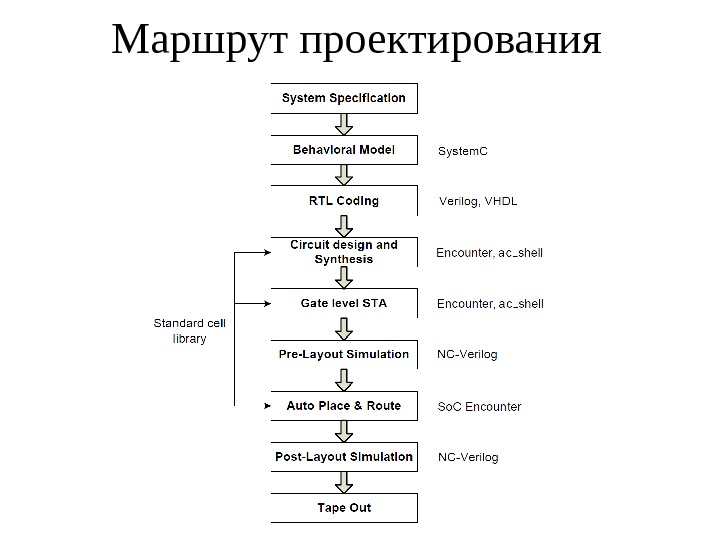

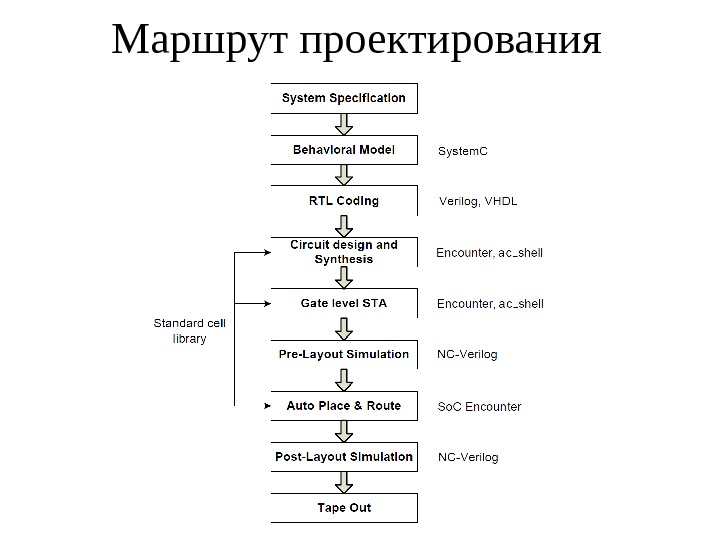

Маршрут проектирования

Маршрут проектирования