П Р О Е К Т И Р

ddca_ch2.pptx

- Размер: 2.9 Мб

- Автор: Владимир Алексеев

- Количество слайдов: 84

Описание презентации П Р О Е К Т И Р по слайдам

П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИГлава 2 Цифровая схемотехника и архитектура компьютера, второе издание Глава 2 Дэвид М. Харрис и Сара Л. Харрис

П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИГлава 2 Цифровая схемотехника и архитектура компьютера, второе издание Глава 2 Дэвид М. Харрис и Сара Л. Харрис

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИЦифровая схемотехника и архитектура компьютера Эти слайды предназначены для преподавателей, которые читают лекции на основе учебника «Цифровая схемотехника и архитектура компьютера» авторов Дэвида Харриса и Сары Харрис. Бесплатный русский перевод второго издания этого учебника можно загрузить с сайта компании Imagination Technologies: https: //community. imgtec. com/downloads/digital-design-and-computer-a rchitecture-russian-edition-second-edition Процедура регистрации на сайте компании Imagination Technologies описана на станице: http: //www. silicon-russia. com/2016/08/04/harris-and-harris-2/

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИЦифровая схемотехника и архитектура компьютера Эти слайды предназначены для преподавателей, которые читают лекции на основе учебника «Цифровая схемотехника и архитектура компьютера» авторов Дэвида Харриса и Сары Харрис. Бесплатный русский перевод второго издания этого учебника можно загрузить с сайта компании Imagination Technologies: https: //community. imgtec. com/downloads/digital-design-and-computer-a rchitecture-russian-edition-second-edition Процедура регистрации на сайте компании Imagination Technologies описана на станице: http: //www. silicon-russia. com/2016/08/04/harris-and-harris-2/

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБлагодарности Перевод данных слайдов на русский язык был выполнен командой сотрудников университетов и компаний из России, Украины, США в составе: • Александр Барабанов — доцент кафедры компьютерной инженерии факультета радиофизики, электроники и компьютерных систем Киевского национального университета имени Тараса Шевченко, кандидат физ. -мат. наук, Киев, Украина; • Антон Брюзгин — начальник отдела АО «Вибро-прибор» , Санкт-Петербург, Россия. • Евгений Короткий — доцент кафедры конструирования электронно-вычислительной аппаратуры факультета электроники Национального технического университета Украины «Киевский Политехнический Институт» , руководитель открытой лаборатории электроники Lampa, кандидат технических наук, Киев, Украина; • Евгения Литвинова – заместитель декана факультета компьютерной инженерии и управления, доктор технических наук, профессор кафедры автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, Харьков, Украина; • Юрий Панчул — старший инженер по разработке и верификации блоков микропроцессорного ядра в команде MIPS I 6400, Imagination Technologies, отделение в Санта-Кларе, Калифорния, США; • Дмитрий Рожко — инженер-программист АО «Вибро-прибор» , магистр Санкт-Петербургского государственного автономного университета аэрокосмического приборостроения (ГУАП), Санкт-Петербург, Россия; • Владимир Хаханов – декан факультета компьютерной инженерии и управления, проректор по научной работе, доктор технических наук, профессор кафедры автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, Харьков, Украина; • Светлана Чумаченко – заведующая кафедрой автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, доктор технических наук, профессор, Харьков, Украина.

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБлагодарности Перевод данных слайдов на русский язык был выполнен командой сотрудников университетов и компаний из России, Украины, США в составе: • Александр Барабанов — доцент кафедры компьютерной инженерии факультета радиофизики, электроники и компьютерных систем Киевского национального университета имени Тараса Шевченко, кандидат физ. -мат. наук, Киев, Украина; • Антон Брюзгин — начальник отдела АО «Вибро-прибор» , Санкт-Петербург, Россия. • Евгений Короткий — доцент кафедры конструирования электронно-вычислительной аппаратуры факультета электроники Национального технического университета Украины «Киевский Политехнический Институт» , руководитель открытой лаборатории электроники Lampa, кандидат технических наук, Киев, Украина; • Евгения Литвинова – заместитель декана факультета компьютерной инженерии и управления, доктор технических наук, профессор кафедры автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, Харьков, Украина; • Юрий Панчул — старший инженер по разработке и верификации блоков микропроцессорного ядра в команде MIPS I 6400, Imagination Technologies, отделение в Санта-Кларе, Калифорния, США; • Дмитрий Рожко — инженер-программист АО «Вибро-прибор» , магистр Санкт-Петербургского государственного автономного университета аэрокосмического приборостроения (ГУАП), Санкт-Петербург, Россия; • Владимир Хаханов – декан факультета компьютерной инженерии и управления, проректор по научной работе, доктор технических наук, профессор кафедры автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, Харьков, Украина; • Светлана Чумаченко – заведующая кафедрой автоматизации проектирования вычислительной техники Харьковского национального университета радиоэлектроники, доктор технических наук, профессор, Харьков, Украина.

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Введение • Булевы выражения • Булева алгебра • От логики к логическим элементам • Многоуровневая комбинационная логика • Что за X и Z? • Карты Карно • Базовые комбинационные блоки • Временные характеристик. Глава 2 : : Темы

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Введение • Булевы выражения • Булева алгебра • От логики к логическим элементам • Многоуровневая комбинационная логика • Что за X и Z? • Карты Карно • Базовые комбинационные блоки • Временные характеристик. Глава 2 : : Темы

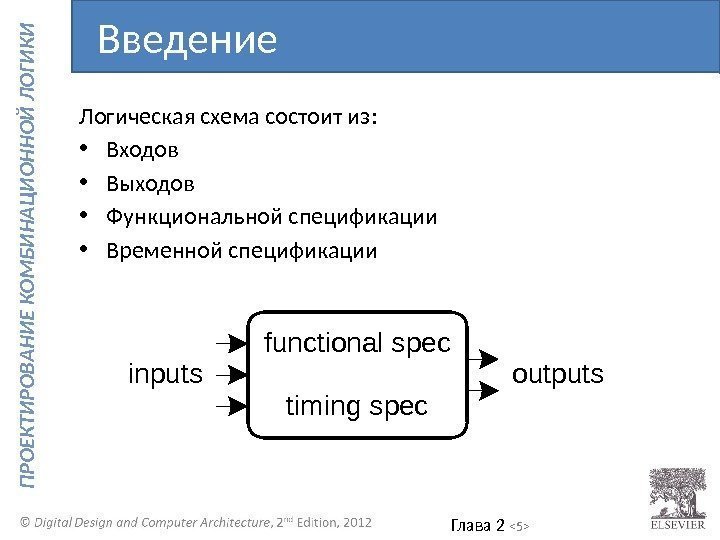

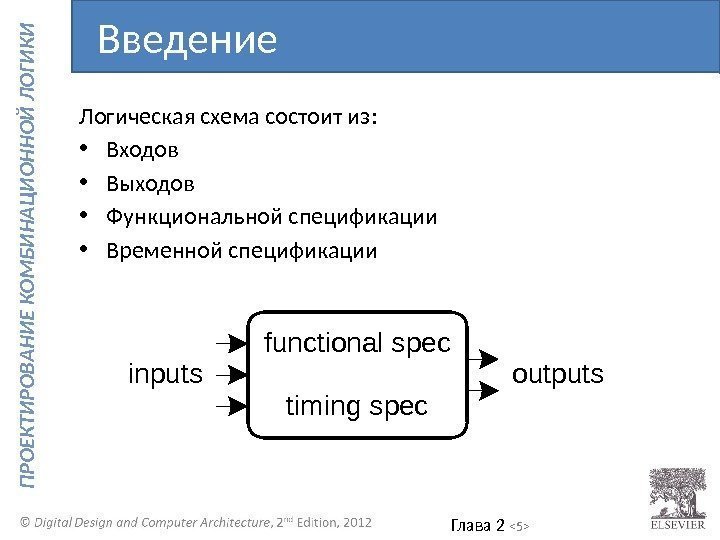

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИЛогическая схема состоит из: • Входов • Выходов • Функциональной спецификации • Временной спецификации. Введение inputsoutputs functional spec timing spec

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИЛогическая схема состоит из: • Входов • Выходов • Функциональной спецификации • Временной спецификации. Введение inputsoutputs functional spec timing spec

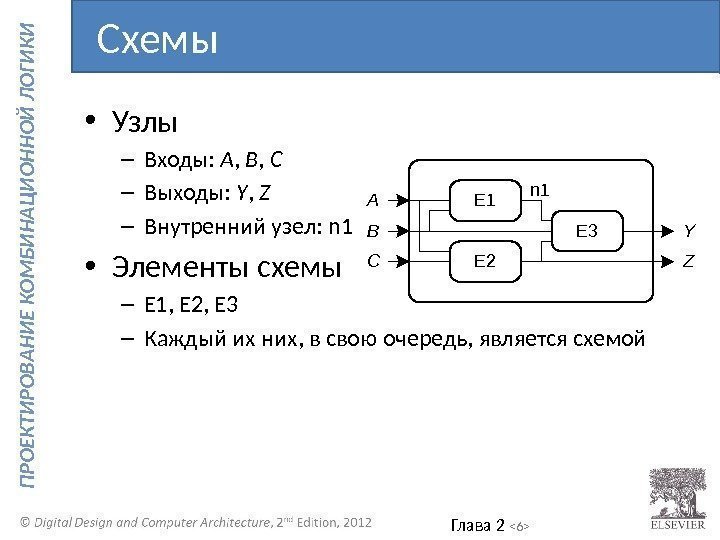

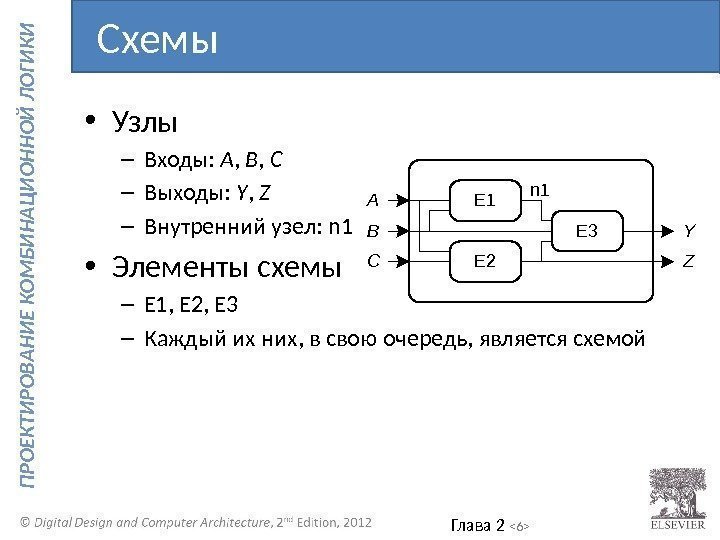

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Узлы – Входы: A , B , C – Выходы: Y , Z – Внутренний узел: n 1 • Элементы схемы – E 1, E 2, E 3 – Каждый их них, в свою очередь, является схемой. Схемы AE 1 E 2 E 3 B C n 1 Y Z

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Узлы – Входы: A , B , C – Выходы: Y , Z – Внутренний узел: n 1 • Элементы схемы – E 1, E 2, E 3 – Каждый их них, в свою очередь, является схемой. Схемы AE 1 E 2 E 3 B C n 1 Y Z

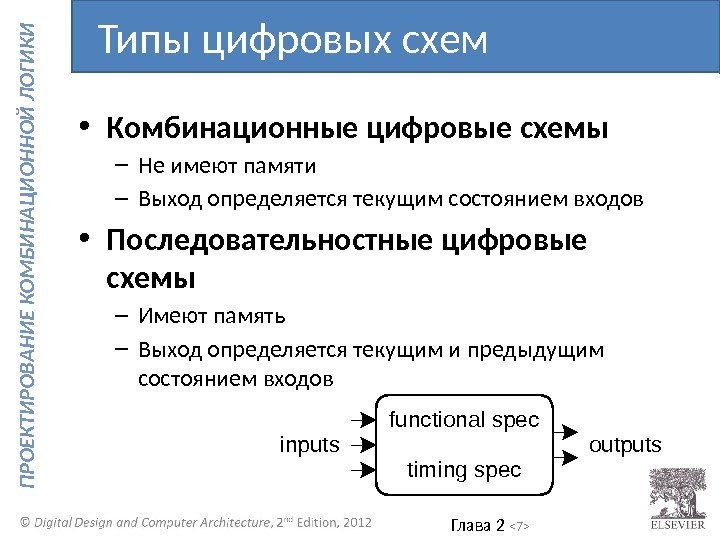

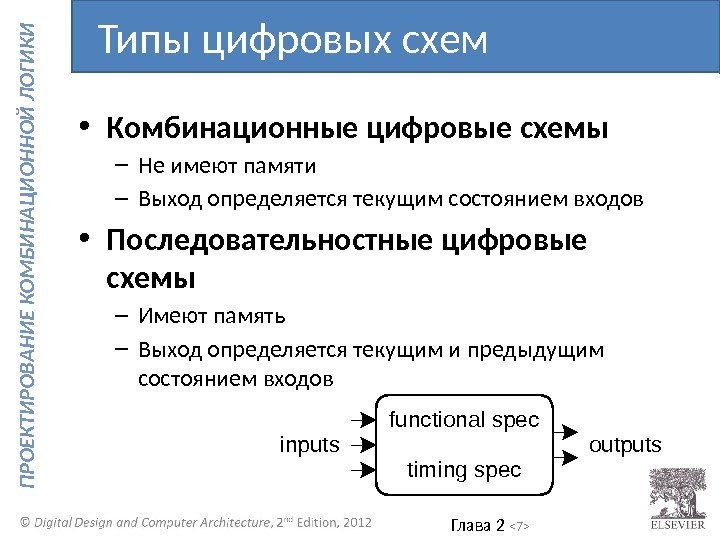

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Комбинационные цифровые схемы – Не имеют памяти – Выход определяется текущим состоянием входов • Последовательностные цифровые схемы – Имеют память – Выход определяется текущим и предыдущим состоянием входов. Типы цифровых схем inputsoutputs functional spec timing spec

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Комбинационные цифровые схемы – Не имеют памяти – Выход определяется текущим состоянием входов • Последовательностные цифровые схемы – Имеют память – Выход определяется текущим и предыдущим состоянием входов. Типы цифровых схем inputsoutputs functional spec timing spec

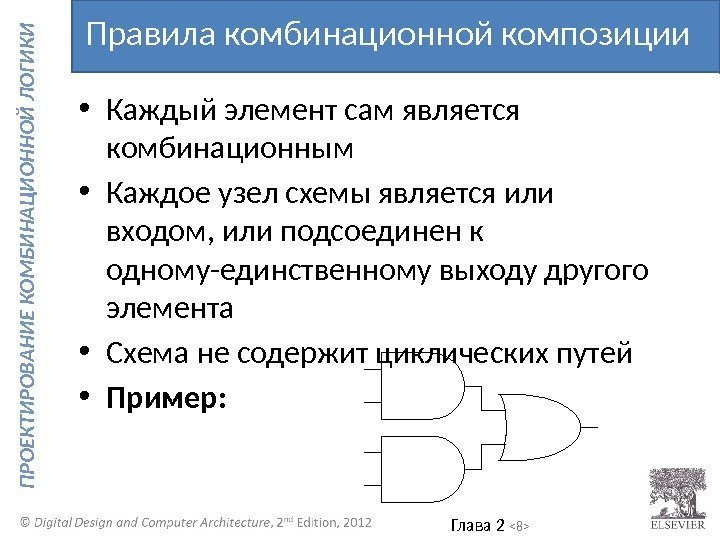

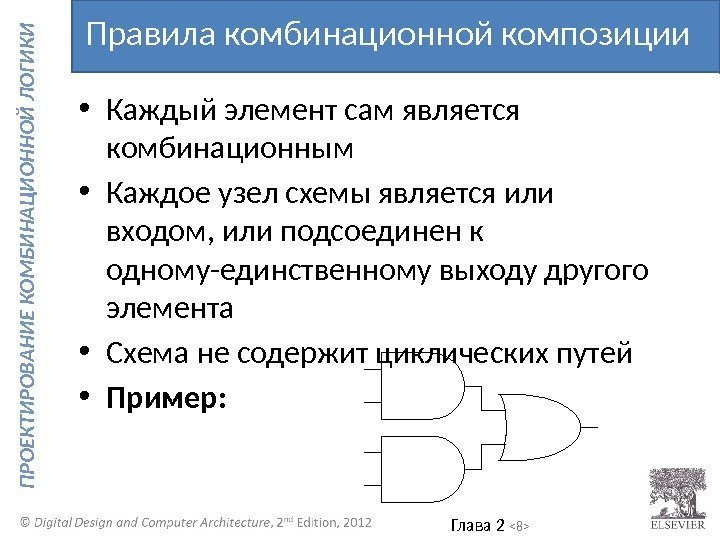

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Каждый элемент сам является комбинационным • Каждое узел схемы является или входом, или подсоединен к одному-единственному выходу другого элемента • Схема не содержит циклических путей • Пример: Правила комбинационной композиции

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Каждый элемент сам является комбинационным • Каждое узел схемы является или входом, или подсоединен к одному-единственному выходу другого элемента • Схема не содержит циклических путей • Пример: Правила комбинационной композиции

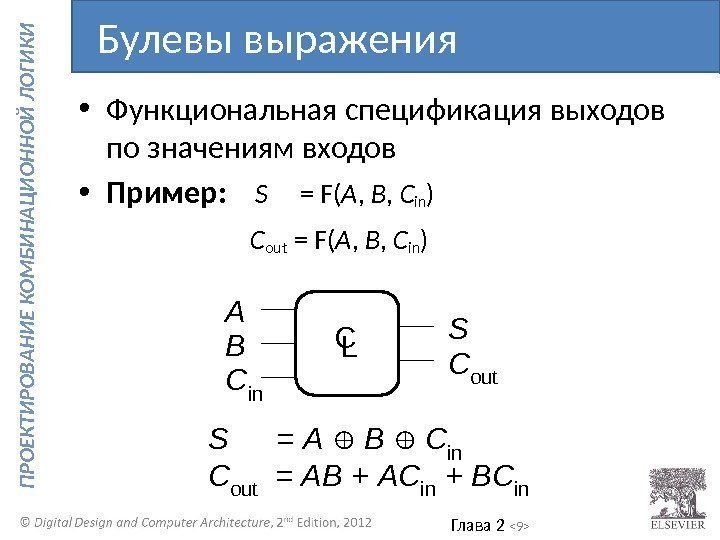

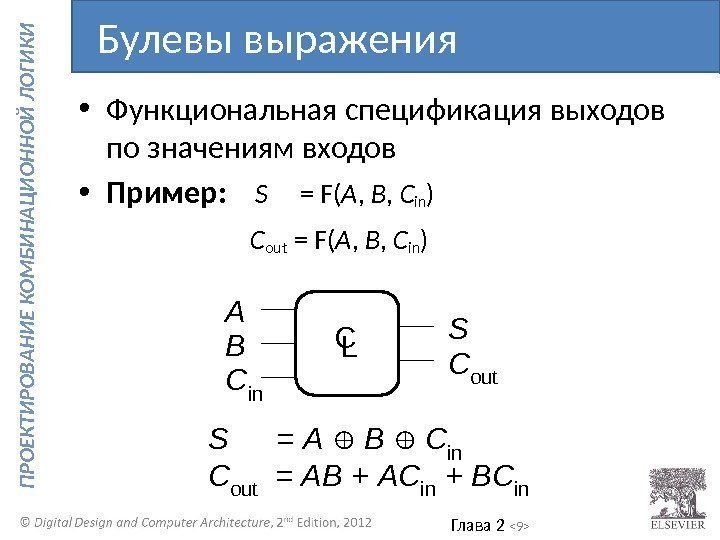

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Функциональная спецификация выходов по значениям входов • Пример: S = F( A , B , C in ) C out = F( A , B , C in ) Булевы выражения A S S = A B C in C out = AB + AC in + BC in B Cin CL C out

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Функциональная спецификация выходов по значениям входов • Пример: S = F( A , B , C in ) C out = F( A , B , C in ) Булевы выражения A S S = A B C in C out = AB + AC in + BC in B Cin CL C out

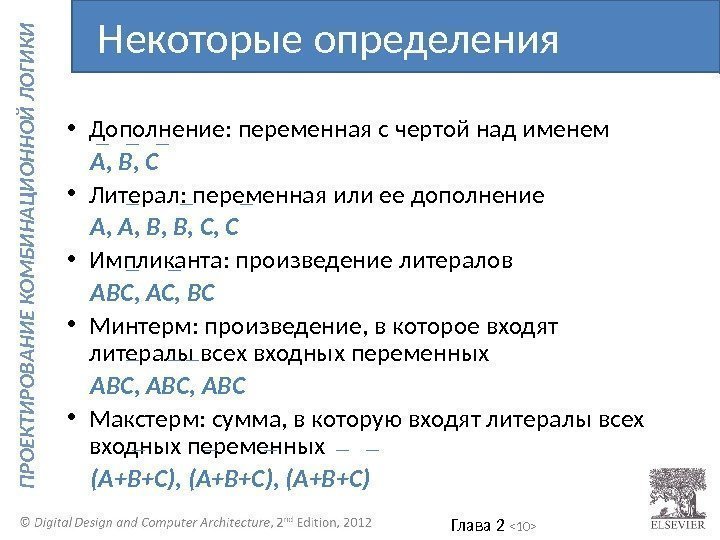

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Дополнение: переменная с чертой над именем A , B , C • Литерал: переменная или ее дополнение A , B , C • Импликанта: произведение литералов ABC , AC , BC • Минтерм: произведение, в которое входят литералы всех входных переменных ABC , ABC • Макстерм: сумма, в которую входят литералы всех входных переменных (A+B+C) , (A+B+C)Некоторые определения

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Дополнение: переменная с чертой над именем A , B , C • Литерал: переменная или ее дополнение A , B , C • Импликанта: произведение литералов ABC , AC , BC • Минтерм: произведение, в которое входят литералы всех входных переменных ABC , ABC • Макстерм: сумма, в которую входят литералы всех входных переменных (A+B+C) , (A+B+C)Некоторые определения

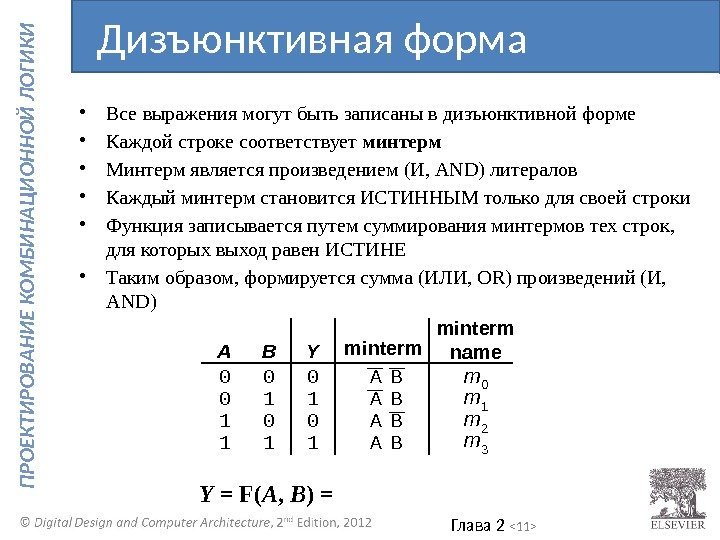

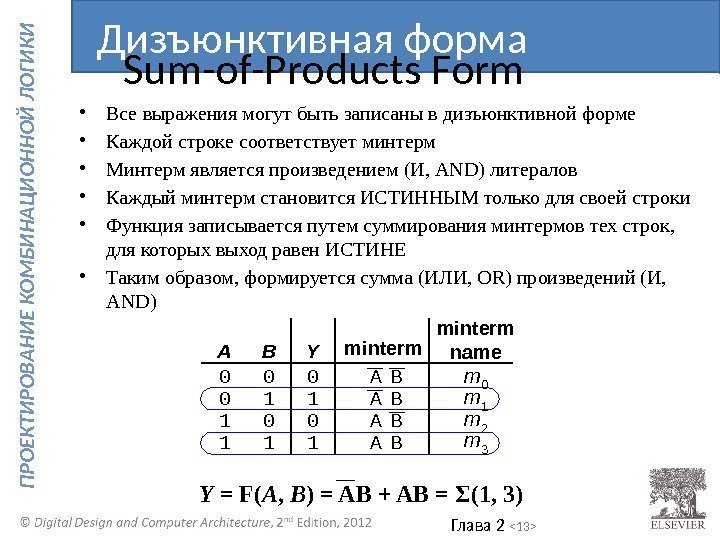

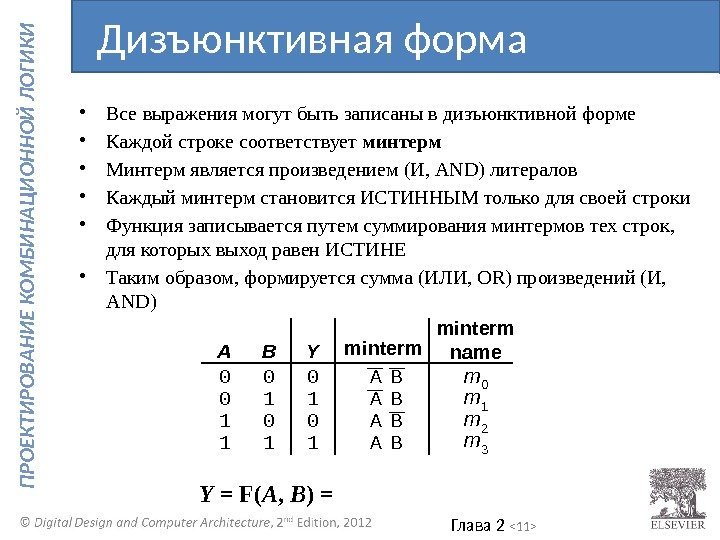

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИY = F( A , B ) = • Все выражения могут быть записаны в дизъюнктивной форме • Каждой строке соответствует минтерм • Минтерм является произведением (И, AND) литералов • Каждый минтерм становится ИСТИННЫМ только для своей строки • Функция записывается путем суммирования минтермов тех строк, для которых выход равен ИСТИНЕ • Таким образом, формируется сумма (ИЛИ, OR) произведений (И, AND)Дизъюнктивная форма ABY 00 01 10 11 0 1 minterm A B A B minterm name m 0 m 1 m 2 m

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИY = F( A , B ) = • Все выражения могут быть записаны в дизъюнктивной форме • Каждой строке соответствует минтерм • Минтерм является произведением (И, AND) литералов • Каждый минтерм становится ИСТИННЫМ только для своей строки • Функция записывается путем суммирования минтермов тех строк, для которых выход равен ИСТИНЕ • Таким образом, формируется сумма (ИЛИ, OR) произведений (И, AND)Дизъюнктивная форма ABY 00 01 10 11 0 1 minterm A B A B minterm name m 0 m 1 m 2 m

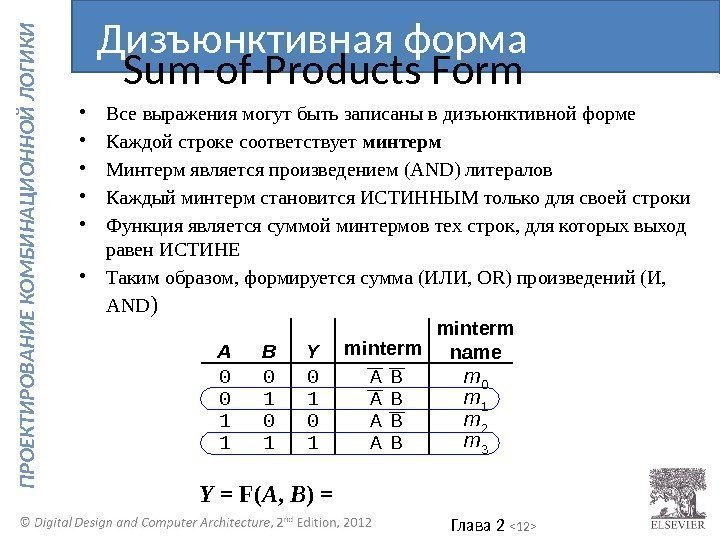

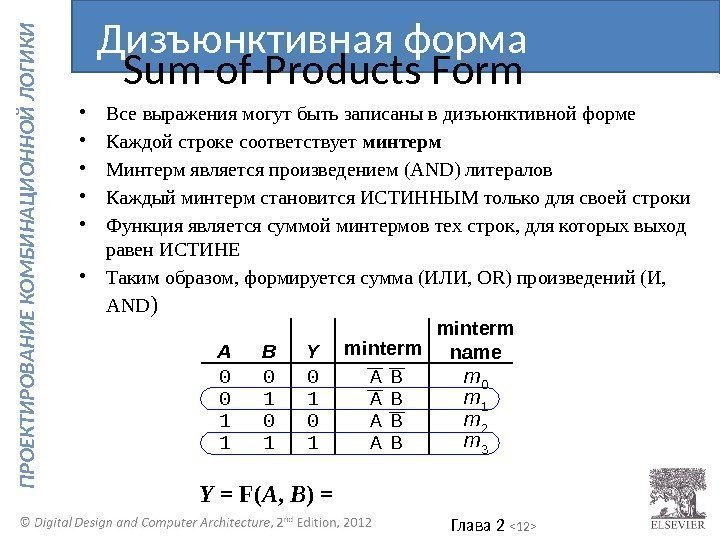

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИSum-of-Products Form Y = F( A , B ) =Дизъюнктивная форма • Все выражения могут быть записаны в дизъюнктивной форме • Каждой строке соответствует минтерм • Минтерм является произведением (AND) литералов • Каждый минтерм становится ИСТИННЫМ только для своей строки • Функция является суммой минтермов тех строк, для которых выход равен ИСТИНЕ • Таким образом, формируется сумма (ИЛИ, OR) произведений (И, AND ) ABY 00 01 10 11 0 1 minterm A B A B minterm name m 0 m 1 m 2 m

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИSum-of-Products Form Y = F( A , B ) =Дизъюнктивная форма • Все выражения могут быть записаны в дизъюнктивной форме • Каждой строке соответствует минтерм • Минтерм является произведением (AND) литералов • Каждый минтерм становится ИСТИННЫМ только для своей строки • Функция является суммой минтермов тех строк, для которых выход равен ИСТИНЕ • Таким образом, формируется сумма (ИЛИ, OR) произведений (И, AND ) ABY 00 01 10 11 0 1 minterm A B A B minterm name m 0 m 1 m 2 m

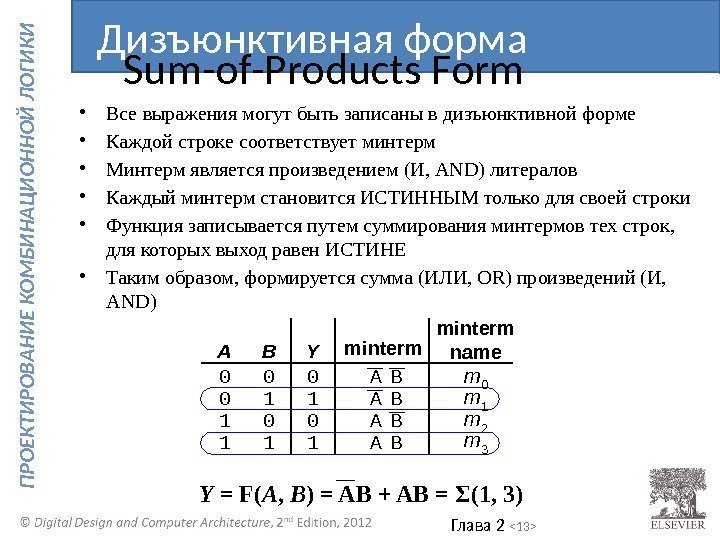

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИSum-of-Products Form Y = F( A , B ) = AB + AB = Σ(1, 3)Дизъюнктивная форма • Все выражения могут быть записаны в дизъюнктивной форме • Каждой строке соответствует минтерм • Минтерм является произведением (И, AND) литералов • Каждый минтерм становится ИСТИННЫМ только для своей строки • Функция записывается путем суммирования минтермов тех строк, для которых выход равен ИСТИНЕ • Таким образом, формируется сумма (ИЛИ, OR) произведений (И, AND) ABY 00 01 10 11 0 1 minterm A B A B minterm name m 0 m 1 m 2 m

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИSum-of-Products Form Y = F( A , B ) = AB + AB = Σ(1, 3)Дизъюнктивная форма • Все выражения могут быть записаны в дизъюнктивной форме • Каждой строке соответствует минтерм • Минтерм является произведением (И, AND) литералов • Каждый минтерм становится ИСТИННЫМ только для своей строки • Функция записывается путем суммирования минтермов тех строк, для которых выход равен ИСТИНЕ • Таким образом, формируется сумма (ИЛИ, OR) произведений (И, AND) ABY 00 01 10 11 0 1 minterm A B A B minterm name m 0 m 1 m 2 m

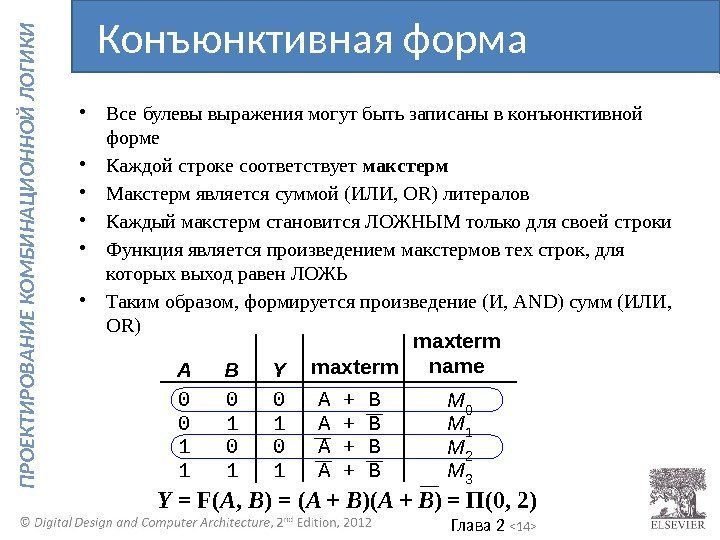

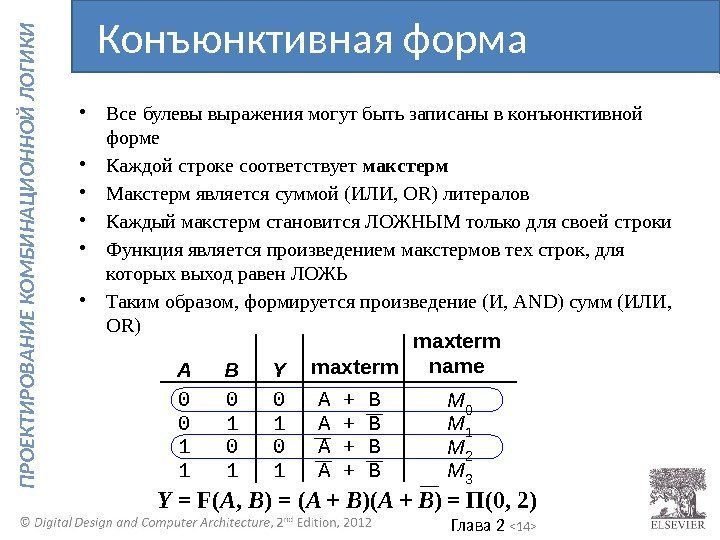

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИY = F( A , B ) = ( A + B ) = Π(0, 2) • Все булевы выражения могут быть записаны в конъюнктивной форме • Каждой строке соответствует макстерм • Макстерм является суммой (ИЛИ, OR) литералов • Каждый макстерм становится ЛОЖНЫМ только для своей строки • Функция является произведением макстермов тех строк, для которых выход равен ЛОЖЬ • Таким образом, формируется произведение (И, AND) сумм (ИЛИ, OR) Конъюнктивная форма A + B ABY 00 01 10 11 0 1 maxterm A + B maxterm name M 0 M 1 M 2 M

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИY = F( A , B ) = ( A + B ) = Π(0, 2) • Все булевы выражения могут быть записаны в конъюнктивной форме • Каждой строке соответствует макстерм • Макстерм является суммой (ИЛИ, OR) литералов • Каждый макстерм становится ЛОЖНЫМ только для своей строки • Функция является произведением макстермов тех строк, для которых выход равен ЛОЖЬ • Таким образом, формируется произведение (И, AND) сумм (ИЛИ, OR) Конъюнктивная форма A + B ABY 00 01 10 11 0 1 maxterm A + B maxterm name M 0 M 1 M 2 M

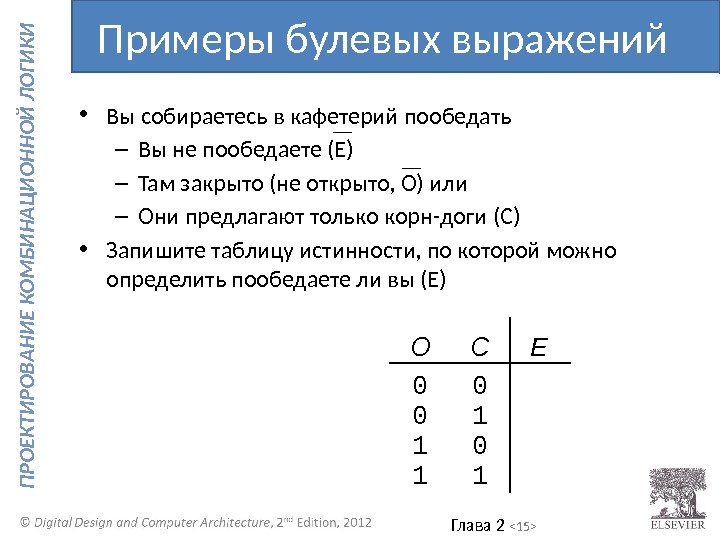

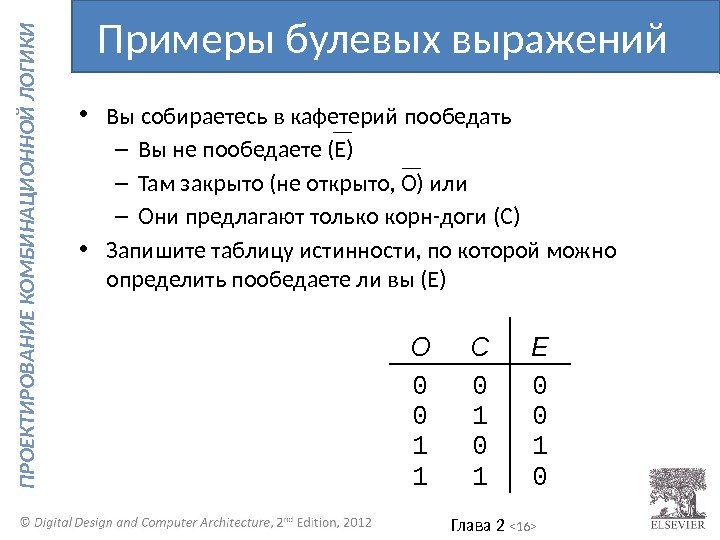

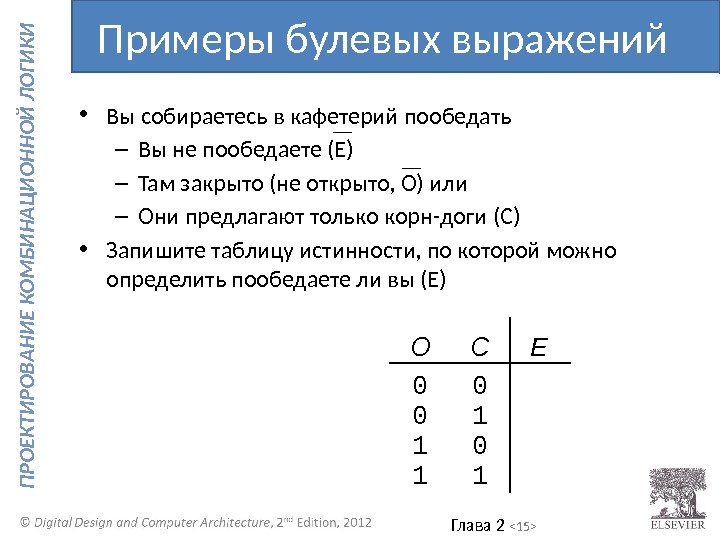

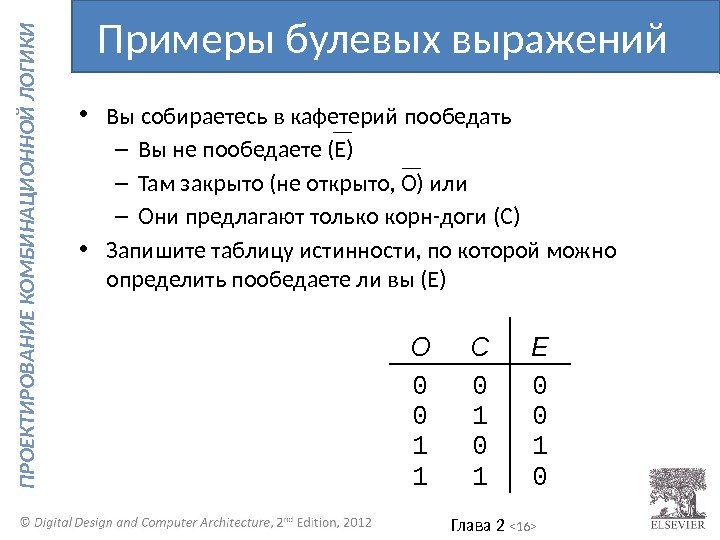

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Вы собираетесь в кафетерий пообедать – Вы не пообедаете (E) – Там закрыто (не открыто, O) или – Они предлагают только корн-доги (C) • Запишите таблицу истинности, по которой можно определить пообедаете ли вы (E)Примеры булевых выражений O

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Вы собираетесь в кафетерий пообедать – Вы не пообедаете (E) – Там закрыто (не открыто, O) или – Они предлагают только корн-доги (C) • Запишите таблицу истинности, по которой можно определить пообедаете ли вы (E)Примеры булевых выражений O

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Вы собираетесь в кафетерий пообедать – Вы не пообедаете (E) – Там закрыто (не открыто, O) или – Они предлагают только корн-доги (C) • Запишите таблицу истинности, по которой можно определить пообедаете ли вы (E)Примеры булевых выражений O

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Вы собираетесь в кафетерий пообедать – Вы не пообедаете (E) – Там закрыто (не открыто, O) или – Они предлагают только корн-доги (C) • Запишите таблицу истинности, по которой можно определить пообедаете ли вы (E)Примеры булевых выражений O

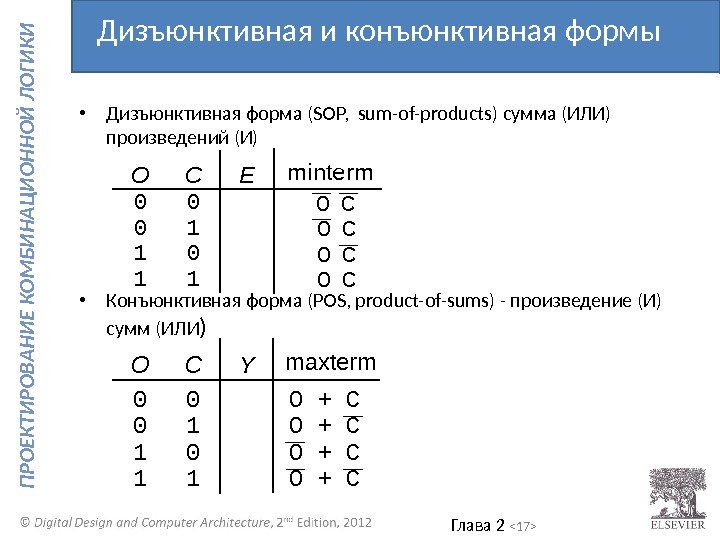

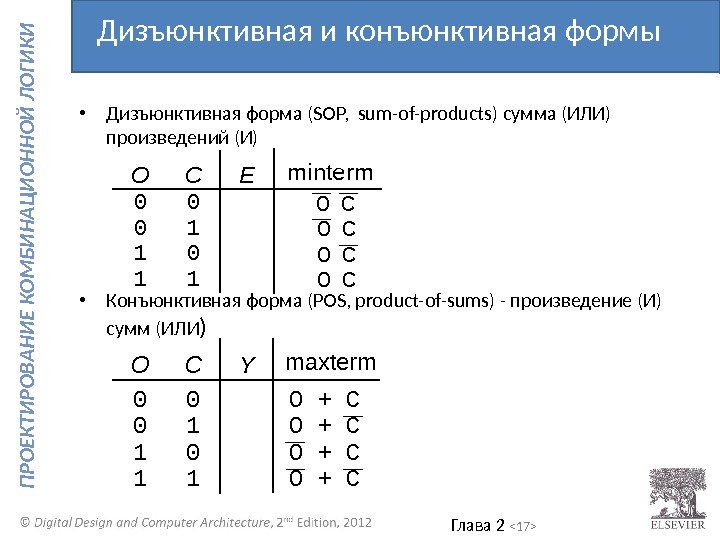

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Дизъюнктивная форма (SOP, sum-of-products) сумма (ИЛИ) произведений (И) • Конъюнктивная форма (POS, product-of-sums) — произведение (И) сумм (ИЛИ )Дизъюнктивная и конъюнктивная формы OCE 00 01 10 11 minterm O C O C O + CO C Y 0 0 0 1 1 maxterm O +

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Дизъюнктивная форма (SOP, sum-of-products) сумма (ИЛИ) произведений (И) • Конъюнктивная форма (POS, product-of-sums) — произведение (И) сумм (ИЛИ )Дизъюнктивная и конъюнктивная формы OCE 00 01 10 11 minterm O C O C O + CO C Y 0 0 0 1 1 maxterm O +

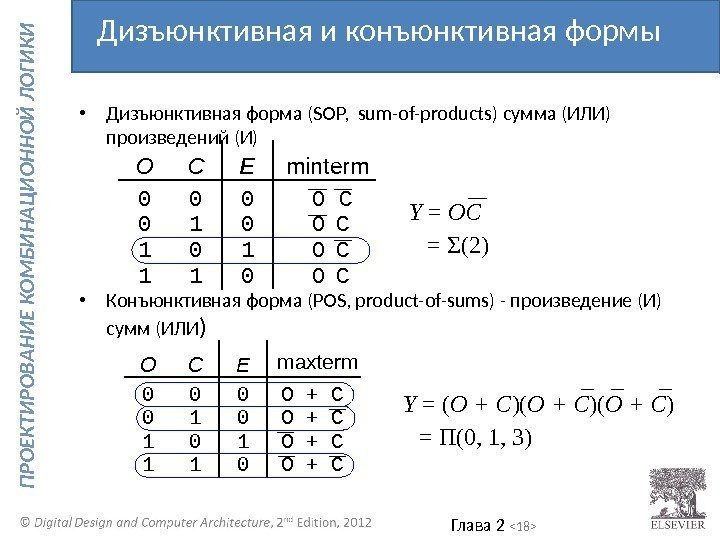

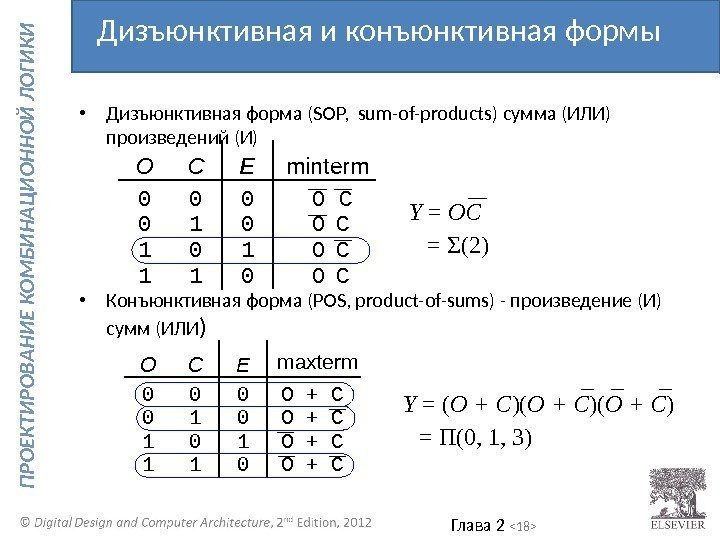

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Дизъюнктивная форма (SOP, sum-of-products) сумма (ИЛИ) произведений (И) • Конъюнктивная форма (POS, product-of-sums) — произведение (И) сумм (ИЛИ ) Y = ( O + C )( O + C ) = Π(0, 1, 3)Y = OC = Σ(2)Дизъюнктивная и конъюнктивная формы O + C OCE 00 01 10 11 0 0 1 0 maxterm O + C O C E 0 0 0 1 1 0 0 1 0 minterm O CO

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Дизъюнктивная форма (SOP, sum-of-products) сумма (ИЛИ) произведений (И) • Конъюнктивная форма (POS, product-of-sums) — произведение (И) сумм (ИЛИ ) Y = ( O + C )( O + C ) = Π(0, 1, 3)Y = OC = Σ(2)Дизъюнктивная и конъюнктивная формы O + C OCE 00 01 10 11 0 0 1 0 maxterm O + C O C E 0 0 0 1 1 0 0 1 0 minterm O CO

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Аксиомы и теоремы позволяют упрощать булевы выражения • Подобно обычной алгебре, но проще: переменные принимают только два значения (0 или 1) • Двойственность аксиом и теорем: – Можно взаимно заменить И и ИЛИ, 0 и 1 Булева алгебра

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Аксиомы и теоремы позволяют упрощать булевы выражения • Подобно обычной алгебре, но проще: переменные принимают только два значения (0 или 1) • Двойственность аксиом и теорем: – Можно взаимно заменить И и ИЛИ, 0 и 1 Булева алгебра

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБулевы аксиомы

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБулевы аксиомы

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B 1 = B • B + 0 = BT 1: Теорема идентичности

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B 1 = B • B + 0 = BT 1: Теорема идентичности

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B 1 = B • B + 0 = BT 1: Теорема идентичности 1= =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B 1 = B • B + 0 = BT 1: Теорема идентичности 1= =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B 0 = 0 • B + 1 = 1 T 2: Теорема о нулевом элементе

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B 0 = 0 • B + 1 = 1 T 2: Теорема о нулевом элементе

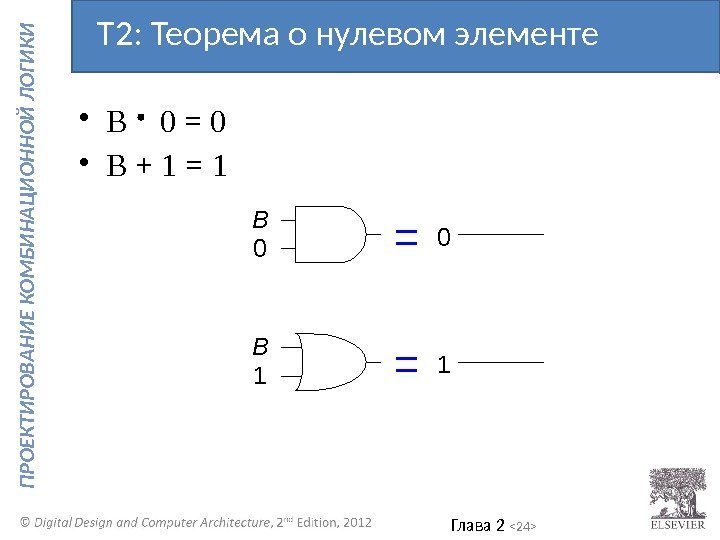

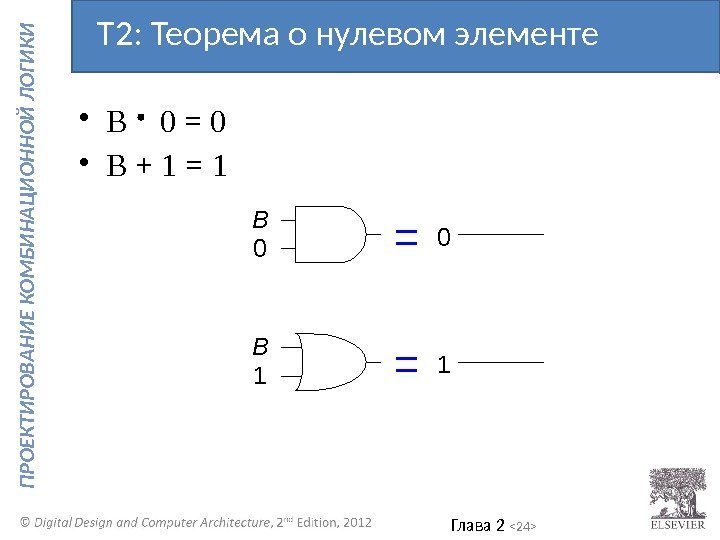

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B 0 = 0 • B + 1 = 1 T 2: Теорема о нулевом элементе 0 = =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B 0 = 0 • B + 1 = 1 T 2: Теорема о нулевом элементе 0 = =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B B = B • B + B = BT 3: Теорема об идемпотентности

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B B = B • B + B = BT 3: Теорема об идемпотентности

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B B = B • B + B = BT 3: Теорема об идемпотентности B= =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B B = B • B + B = BT 3: Теорема об идемпотентности B= =

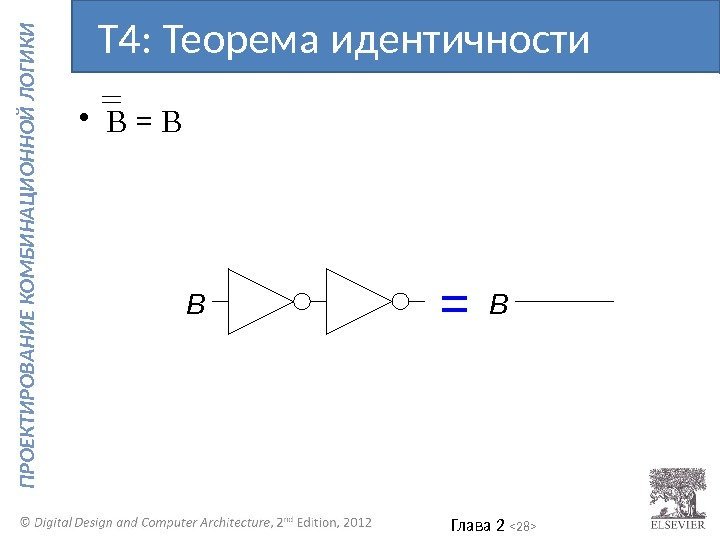

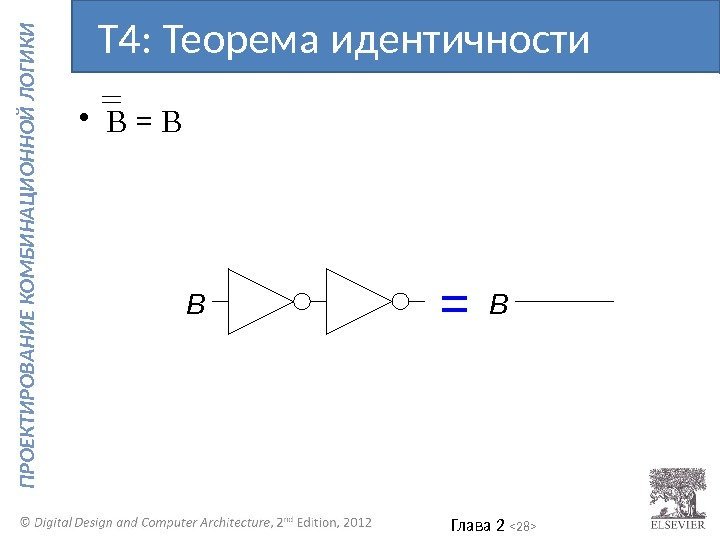

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B = BT 4: Теорема идентичности

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B = BT 4: Теорема идентичности

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B = BT 4: Теорема идентичности =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B = BT 4: Теорема идентичности =

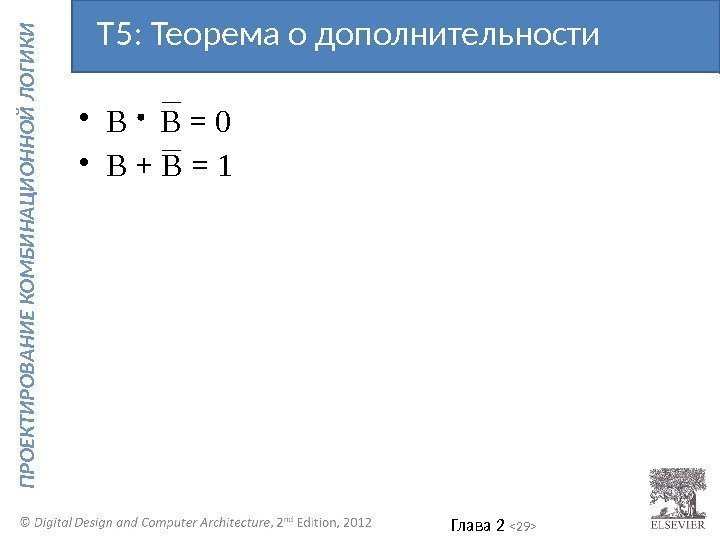

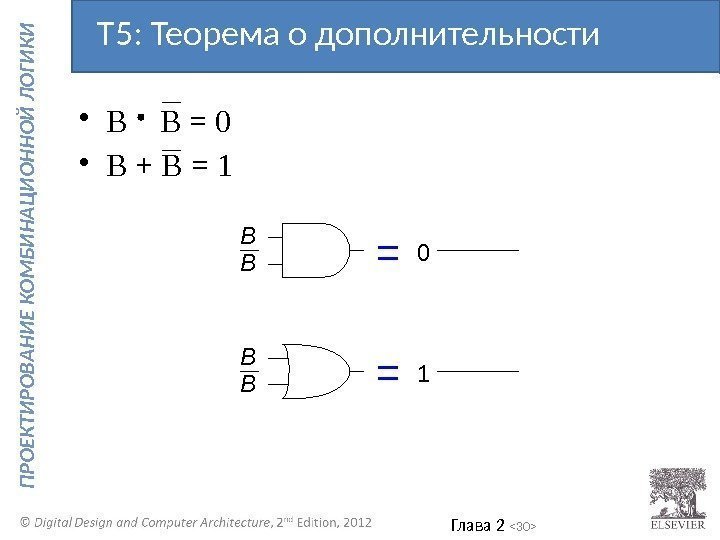

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B B = 0 • B + B = 1 T 5: Теорема о дополнительности

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B B = 0 • B + B = 1 T 5: Теорема о дополнительности

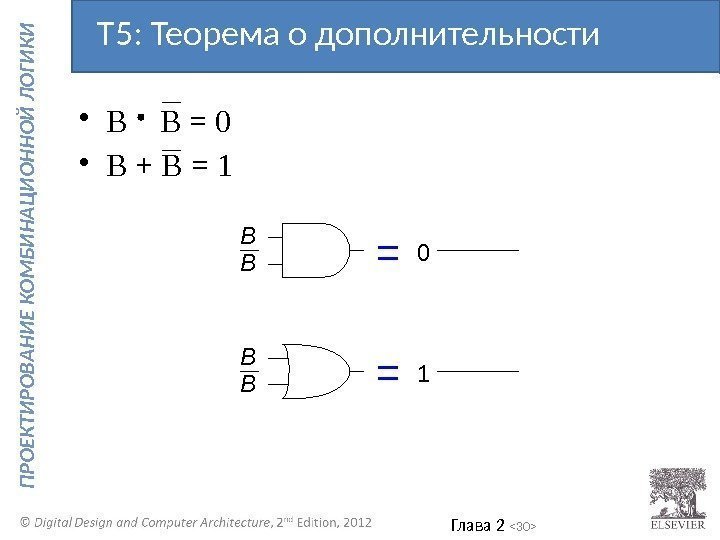

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B B = 0 • B + B = 1 T 5: Теорема о дополнительности B= =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • B B = 0 • B + B = 1 T 5: Теорема о дополнительности B= =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБулевы теоремы, обзор

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБулевы теоремы, обзор

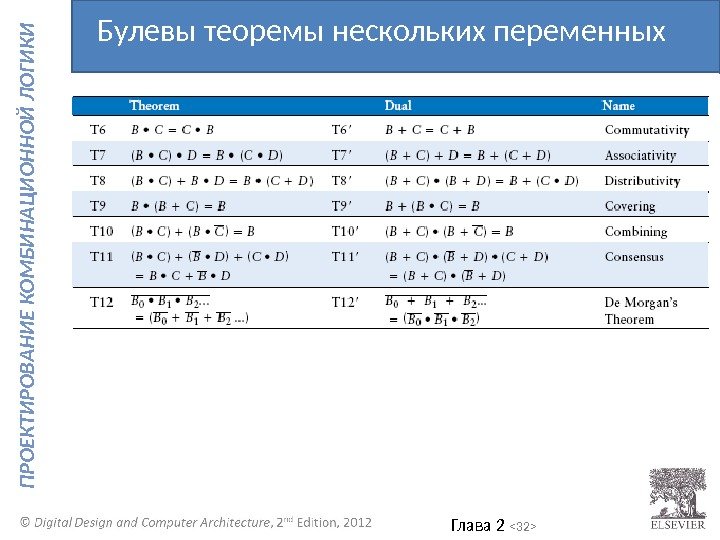

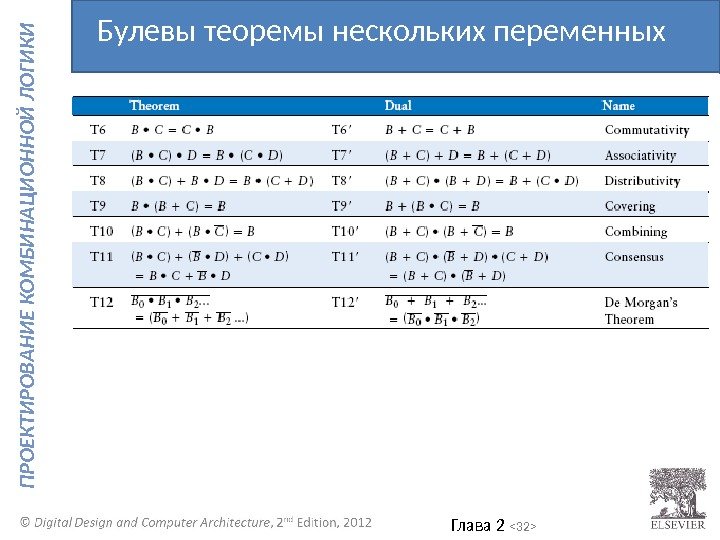

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБулевы теоремы нескольких переменных

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБулевы теоремы нескольких переменных

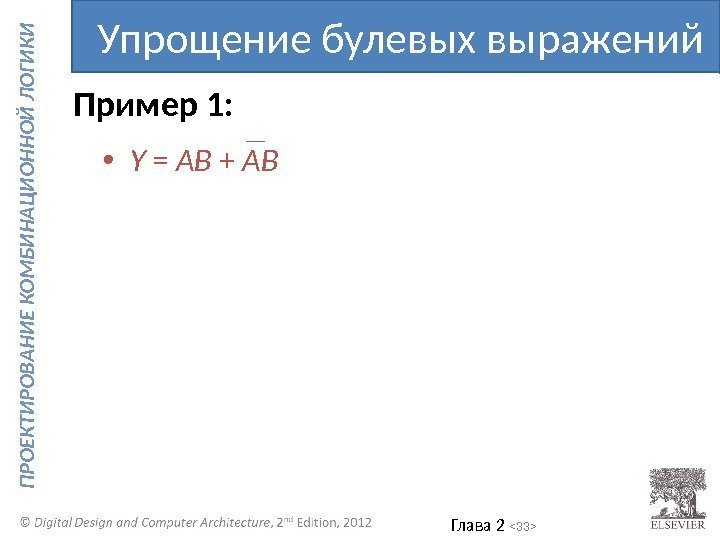

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Y = AB + AB Упрощение булевых выражений Пример 1:

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Y = AB + AB Упрощение булевых выражений Пример 1:

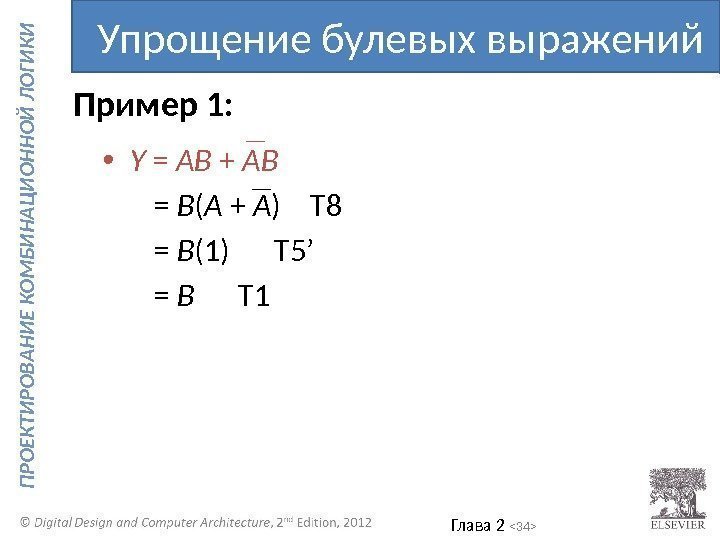

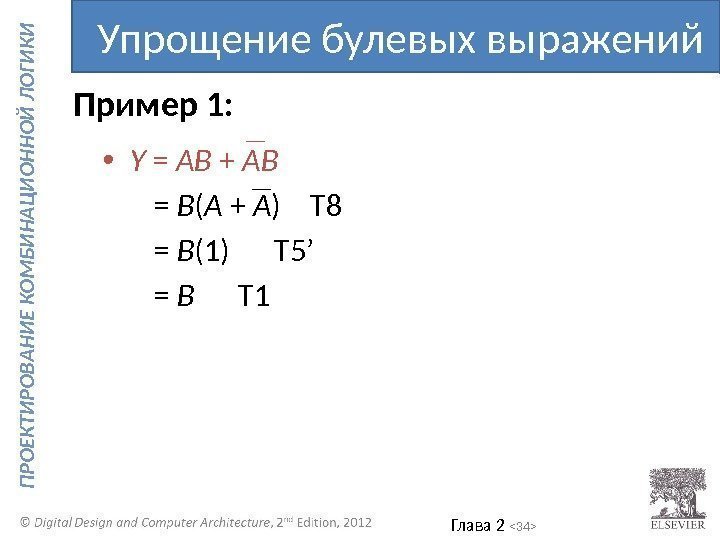

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Y = AB + AB = B ( A + A ) T 8 = B (1) T 5’ = B T 1 Упрощение булевых выражений Пример 1:

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Y = AB + AB = B ( A + A ) T 8 = B (1) T 5’ = B T 1 Упрощение булевых выражений Пример 1:

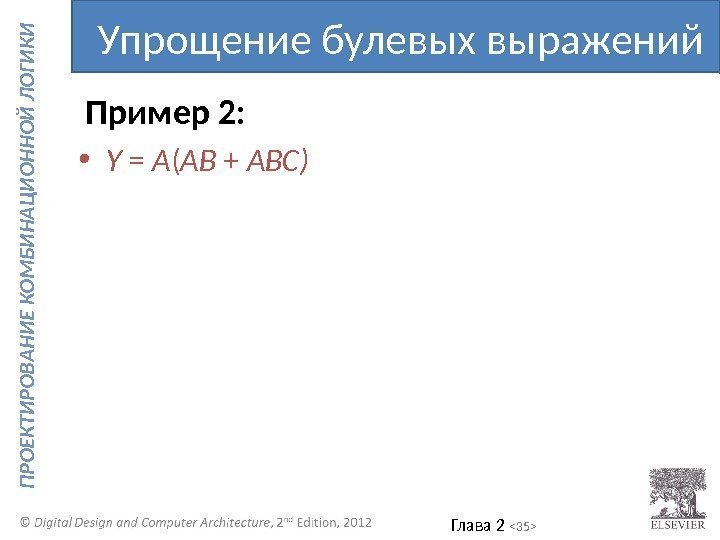

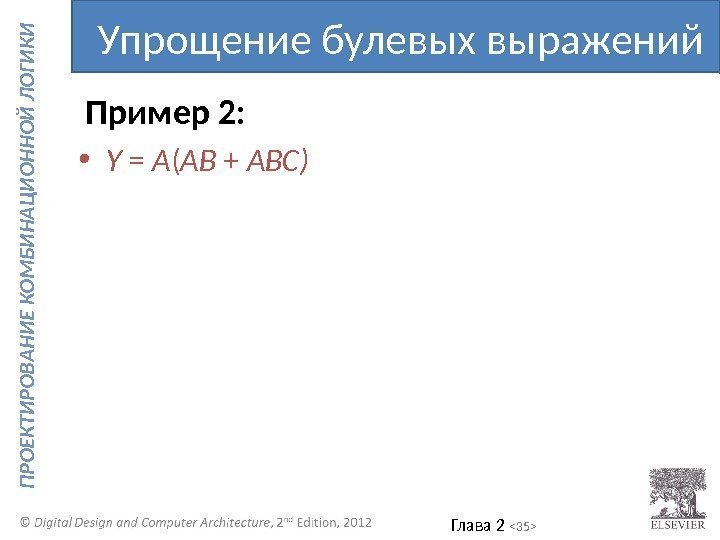

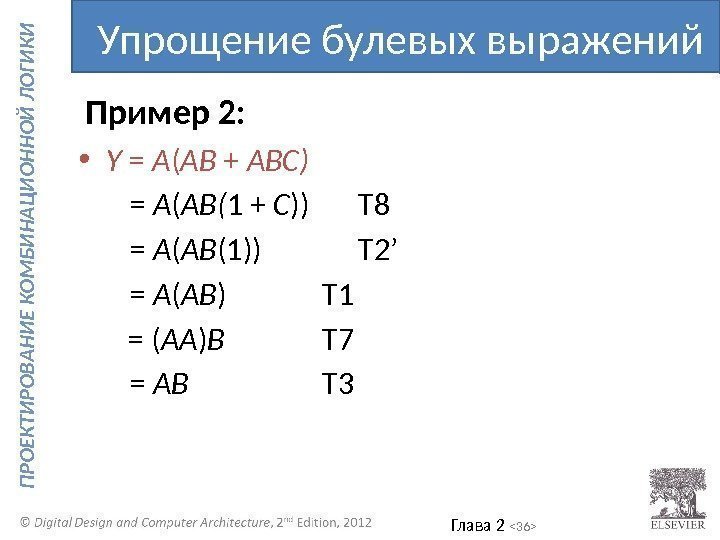

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Y = A ( AB + ABC) Пример 2: Упрощение булевых выражений

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Y = A ( AB + ABC) Пример 2: Упрощение булевых выражений

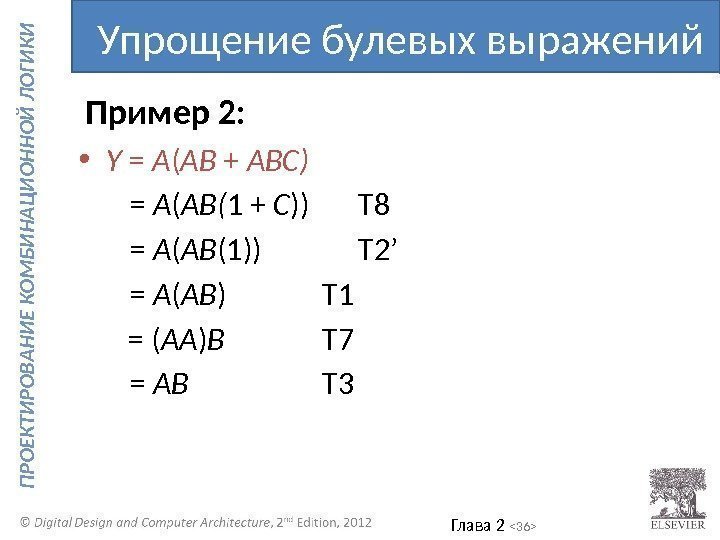

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Y = A ( AB + ABC) = A ( AB( 1 + C )) T 8 = A ( AB (1)) T 2’ = A ( AB ) T 1 = ( AA ) B T 7 = AB T 3 Пример 2: Упрощение булевых выражений

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Y = A ( AB + ABC) = A ( AB( 1 + C )) T 8 = A ( AB (1)) T 2’ = A ( AB ) T 1 = ( AA ) B T 7 = AB T 3 Пример 2: Упрощение булевых выражений

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Y = AB = A + B • Y = A + B = A BТеорема де Моргана A B Y A BY

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Y = AB = A + B • Y = A + B = A BТеорема де Моргана A B Y A BY

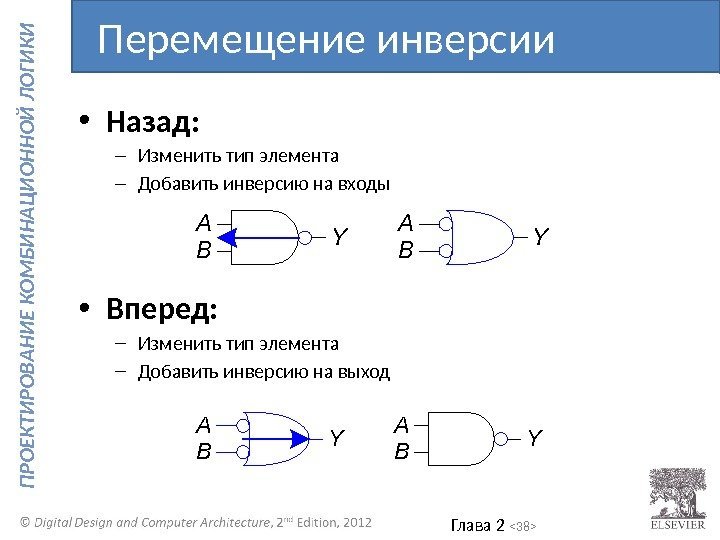

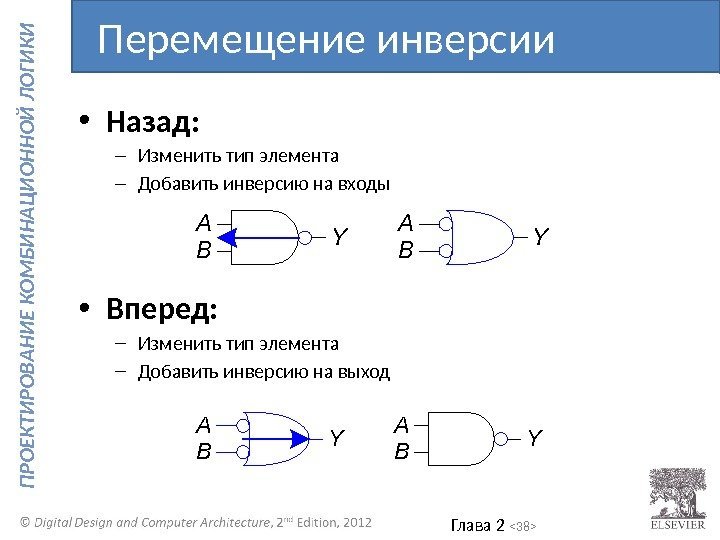

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Назад: – Изменить тип элемента – Добавить инверсию на входы • Вперед: – Изменить тип элемента – Добавить инверсию на выход. Перемещение инверсии A B Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Назад: – Изменить тип элемента – Добавить инверсию на входы • Вперед: – Изменить тип элемента – Добавить инверсию на выход. Перемещение инверсии A B Y

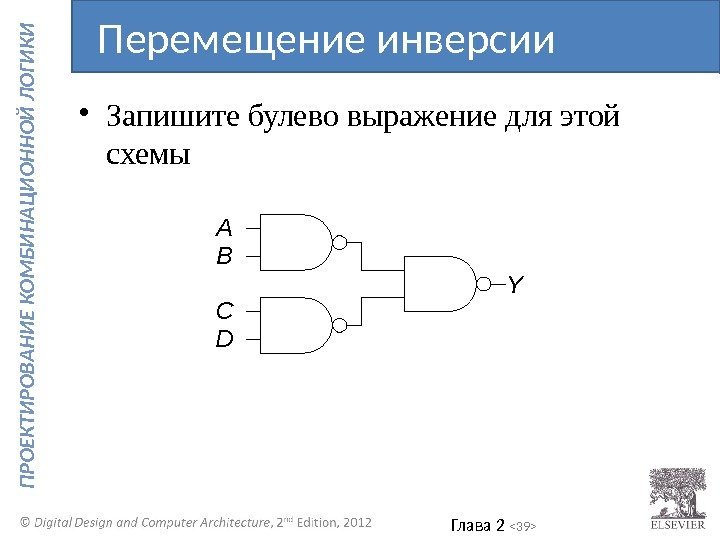

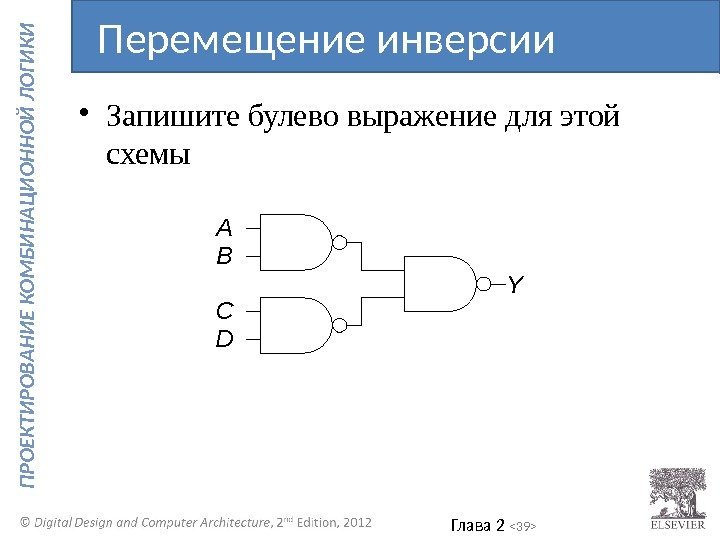

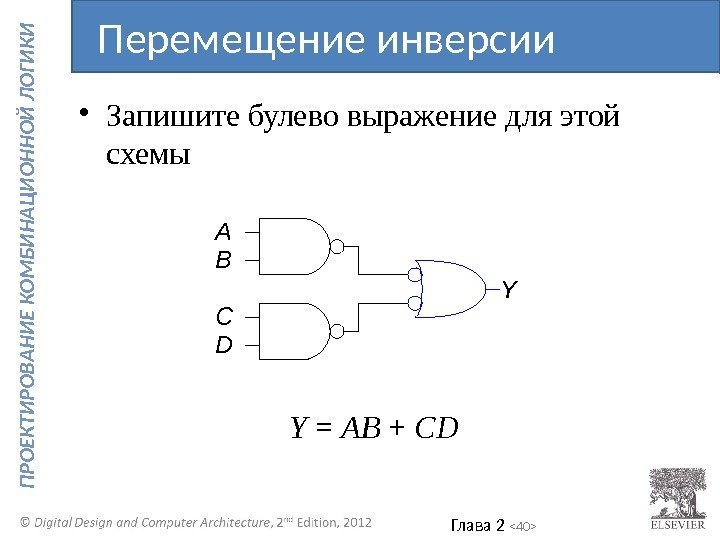

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Запишите булево выражение для этой схемы. Перемещение инверсии A B Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Запишите булево выражение для этой схемы. Перемещение инверсии A B Y

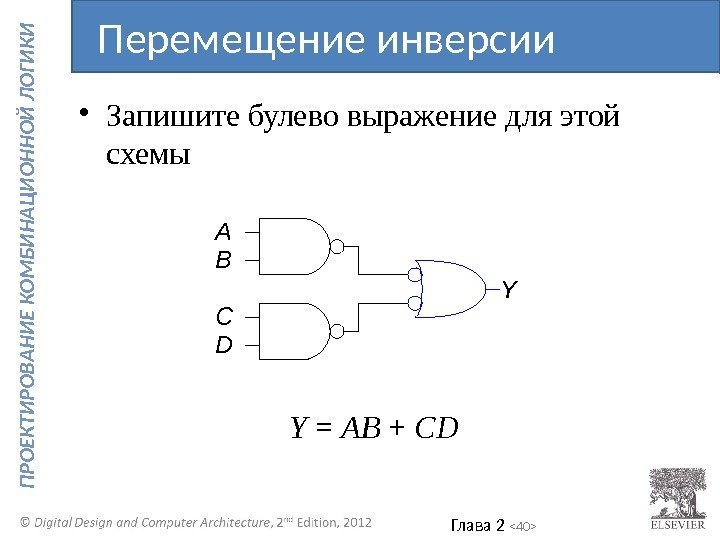

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Запишите булево выражение для этой схемы Y = AB + CDПеремещение инверсии A B Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Запишите булево выражение для этой схемы Y = AB + CDПеремещение инверсии A B Y

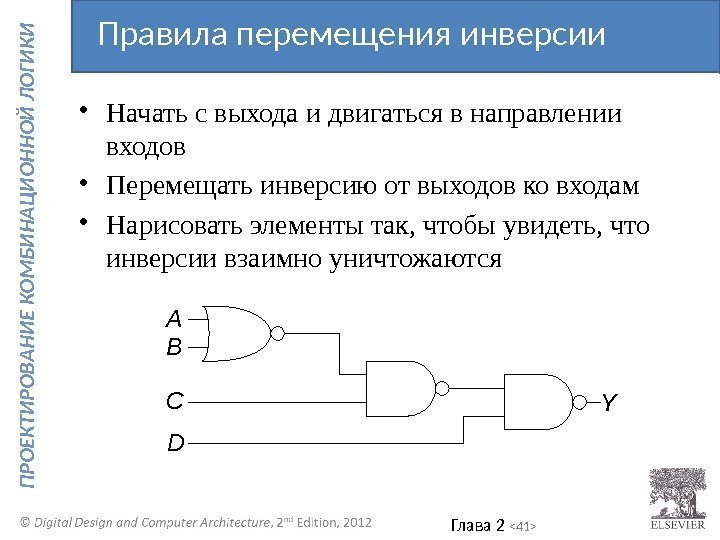

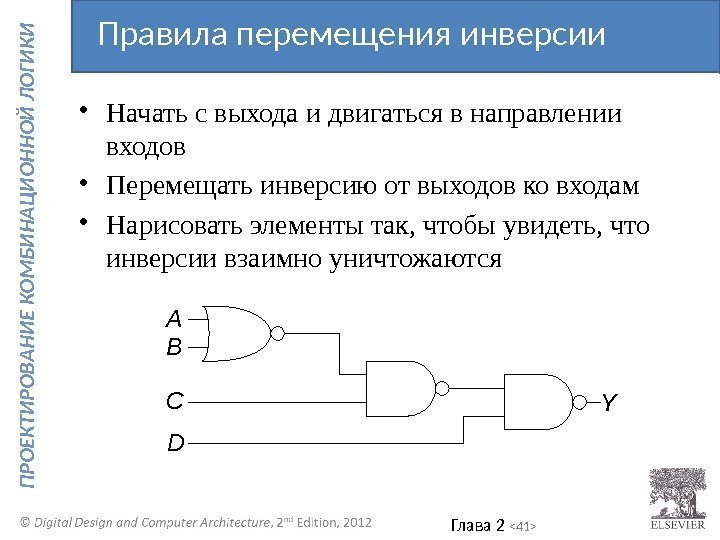

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Начать с выхода и двигаться в направлении входов • Перемещать инверсию от выходов ко входам • Нарисовать элементы так, чтобы увидеть, что инверсии взаимно уничтожаются. Правила перемещения инверсии A B C D Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Начать с выхода и двигаться в направлении входов • Перемещать инверсию от выходов ко входам • Нарисовать элементы так, чтобы увидеть, что инверсии взаимно уничтожаются. Правила перемещения инверсии A B C D Y

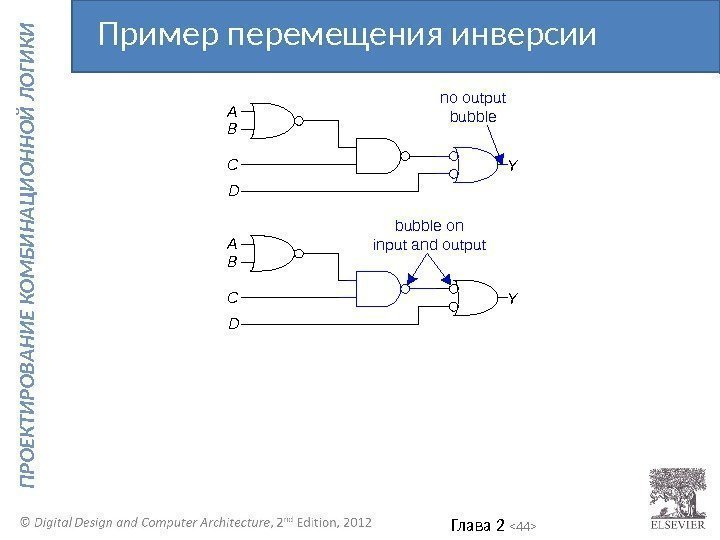

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИПример перемещения инверсии A B CY

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИПример перемещения инверсии A B CY

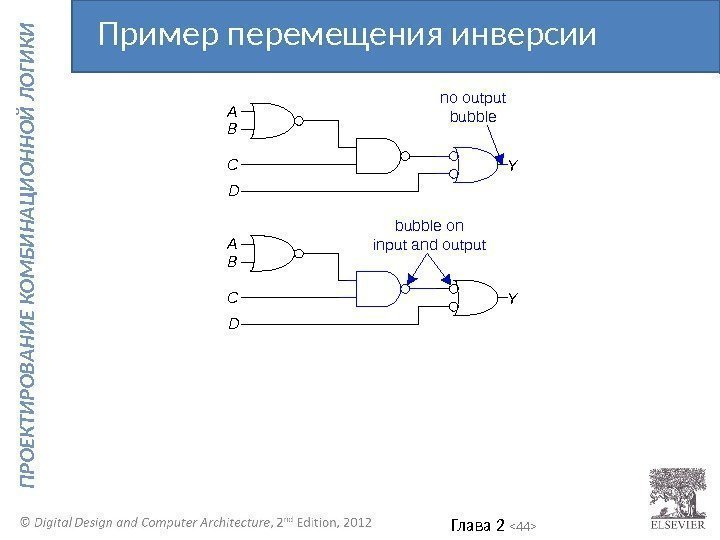

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИПример перемещения инверсии A B CY D no output bubble

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИПример перемещения инверсии A B CY D no output bubble

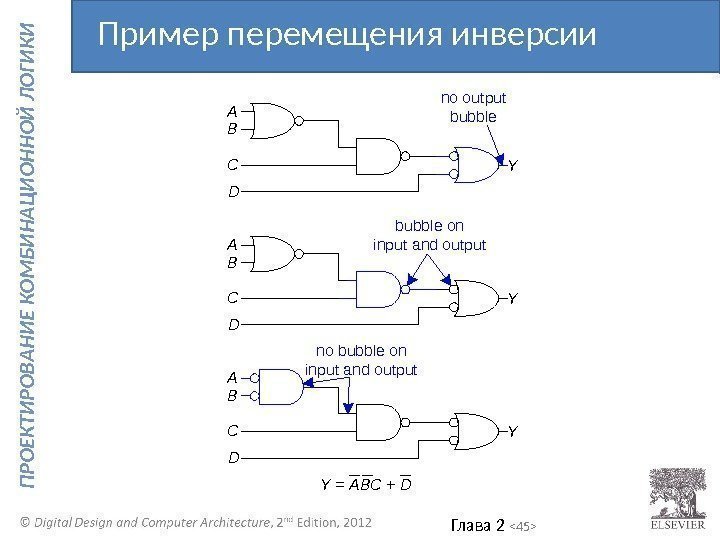

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИПример перемещения инверсии bubble on input and output. A B C D Y A B CY D no output bubble

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИПример перемещения инверсии bubble on input and output. A B C D Y A B CY D no output bubble

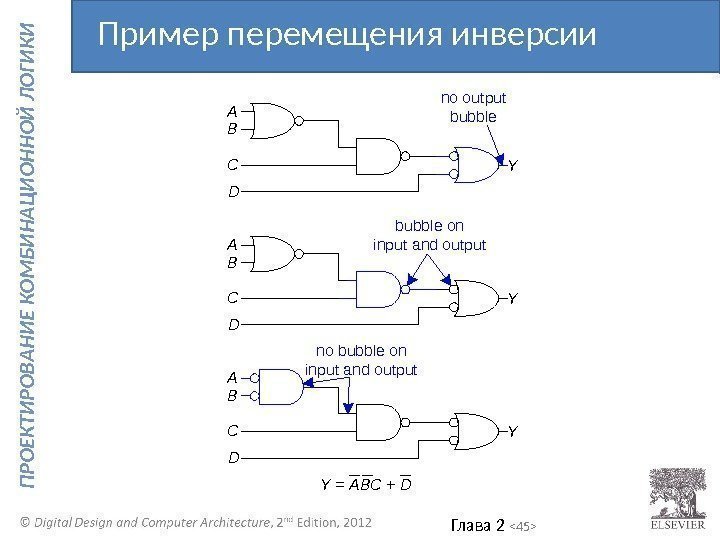

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИПример перемещения инверсии A B C D Y bubble on input and output. A B C D Y A B CY D Y = ABC + D no output bubble no bubble on input and output

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИПример перемещения инверсии A B C D Y bubble on input and output. A B C D Y A B CY D Y = ABC + D no output bubble no bubble on input and output

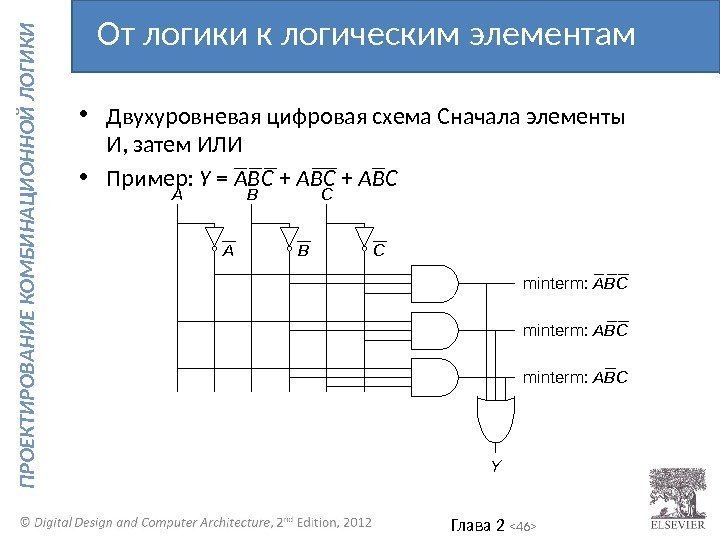

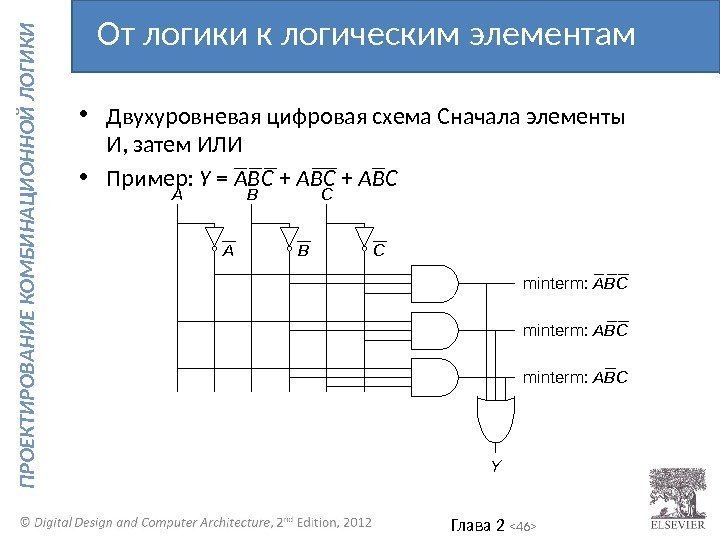

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Двухуровневая цифровая схема Сначала элементы И, затем ИЛИ • Пример: Y = ABC + ABCОт логики к логическим элементам BAC Y minterm:

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Двухуровневая цифровая схема Сначала элементы И, затем ИЛИ • Пример: Y = ABC + ABCОт логики к логическим элементам BAC Y minterm:

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Входы слева (или сверху) • Выходы справа (или внизу) • Информация передается от элементов, расположенных слева, к элементам, расположенным справа • Для проводников стараться использовать прямые линии. Правила изображения принципиальных схем

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Входы слева (или сверху) • Выходы справа (или внизу) • Информация передается от элементов, расположенных слева, к элементам, расположенным справа • Для проводников стараться использовать прямые линии. Правила изображения принципиальных схем

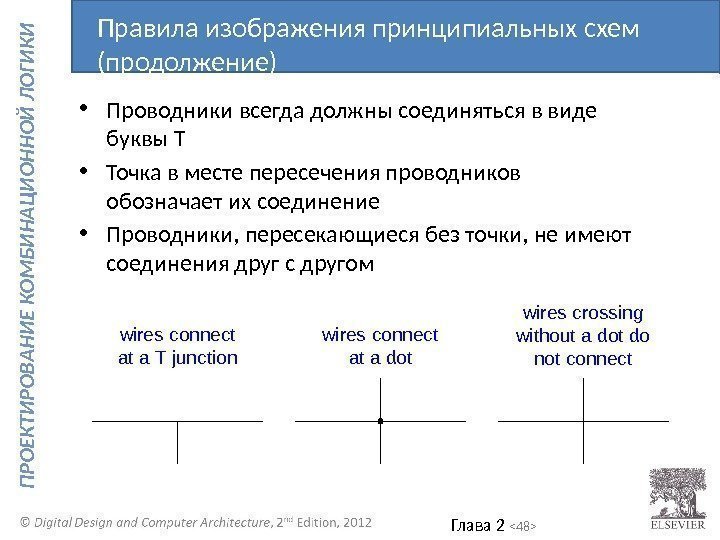

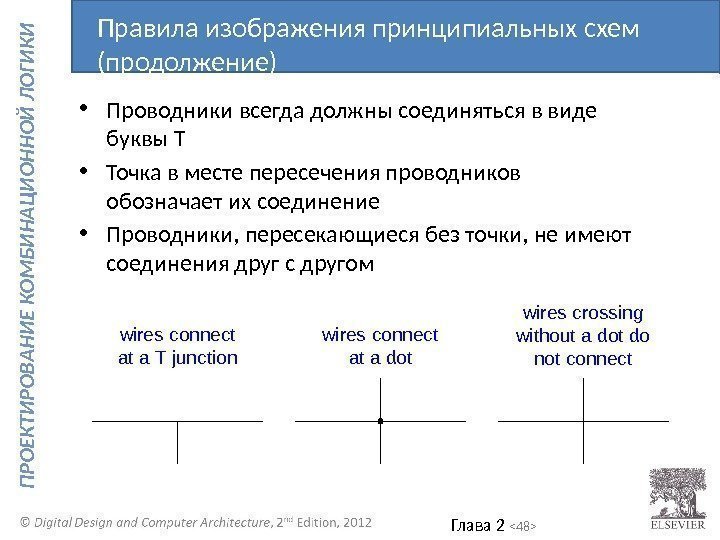

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Проводники всегда должны соединяться в виде буквы Т • Точка в месте пересечения проводников обозначает их соединение • Проводники, пересекающиеся без точки, не имеют соединения друг с другом. Правила изображения принципиальных схем (продолжение) wires connect at a T junction wires connect at a dot wires crossing without a dot do not connect

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Проводники всегда должны соединяться в виде буквы Т • Точка в месте пересечения проводников обозначает их соединение • Проводники, пересекающиеся без точки, не имеют соединения друг с другом. Правила изображения принципиальных схем (продолжение) wires connect at a T junction wires connect at a dot wires crossing without a dot do not connect

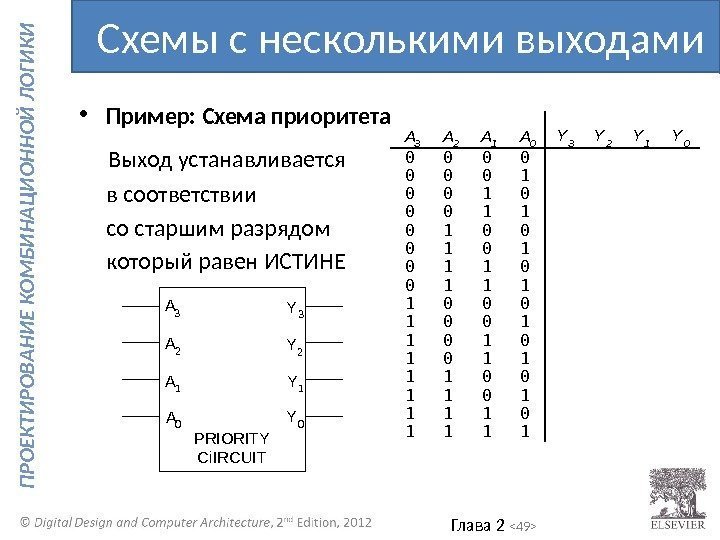

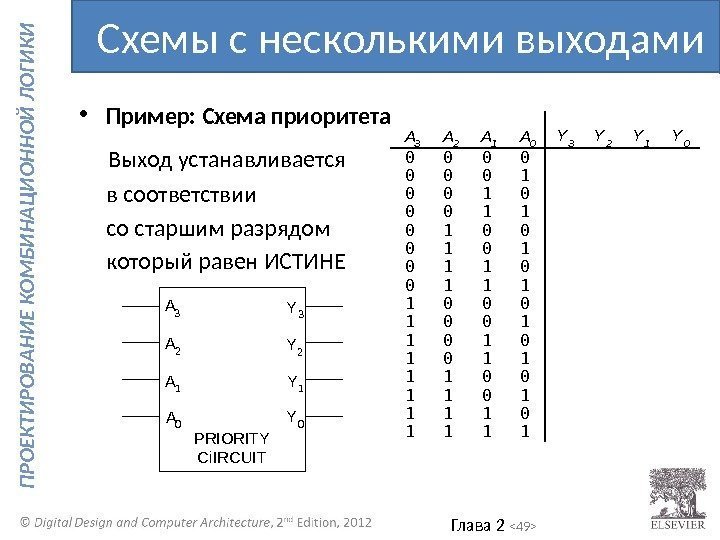

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Пример: Схема приоритета Выход устанавливается в соответствии со старшим разрядом который равен ИСТИНЕСхемы с несколькими выходами A 1 A 0 00 01 10 11 Y 3 Y 2 Y 1 Y 0 A 3 A 2 00 00 0001 01 10 11 00 01 01 01 10 0110 10 11 00 01 10 10 11 11 1011 1111 A 0 A 1 PRIORITY Ci. IRCUIT A 2 A 3 Y 0 Y 1 Y 2 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Пример: Схема приоритета Выход устанавливается в соответствии со старшим разрядом который равен ИСТИНЕСхемы с несколькими выходами A 1 A 0 00 01 10 11 Y 3 Y 2 Y 1 Y 0 A 3 A 2 00 00 0001 01 10 11 00 01 01 01 10 0110 10 11 00 01 10 10 11 11 1011 1111 A 0 A 1 PRIORITY Ci. IRCUIT A 2 A 3 Y 0 Y 1 Y 2 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Пример: Схема приоритета Выход устанавливается в соответствии со старшим входом который равен ИСТИНЕСхемы с несколькими выходами 0 A 1 A 0 00 01 10 11 0 0 0 Y 3 Y 2 Y 1 Y 0 0 0 0 1 1 0 0 A 3 A 2 00 00 0001 01 10 11 00 01 01 01 10 0110 10 11 00 01 10 10 11 11 1011 1111 0 0 0 1 1 0 0 0 0 0 1000 1 1 0 0 0 1000 A 0 A 1 PRIORITY Ci. IRCUIT A 2 A 3 Y 0 Y 1 Y 2 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Пример: Схема приоритета Выход устанавливается в соответствии со старшим входом который равен ИСТИНЕСхемы с несколькими выходами 0 A 1 A 0 00 01 10 11 0 0 0 Y 3 Y 2 Y 1 Y 0 0 0 0 1 1 0 0 A 3 A 2 00 00 0001 01 10 11 00 01 01 01 10 0110 10 11 00 01 10 10 11 11 1011 1111 0 0 0 1 1 0 0 0 0 0 1000 1 1 0 0 0 1000 A 0 A 1 PRIORITY Ci. IRCUIT A 2 A 3 Y 0 Y 1 Y 2 Y

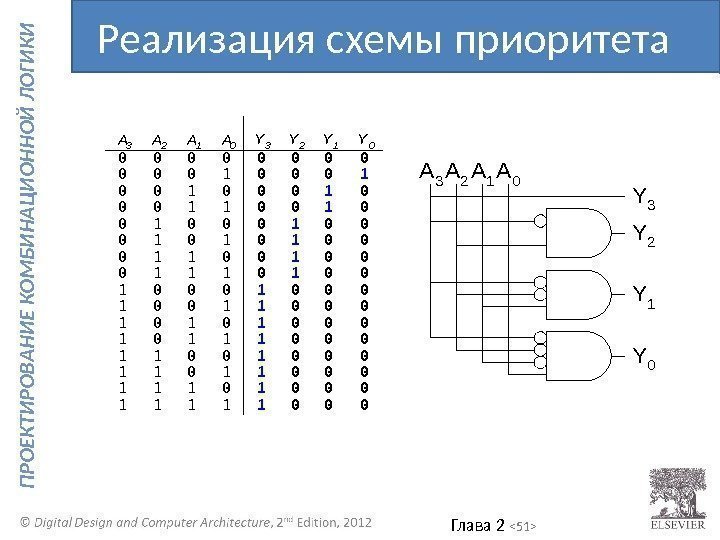

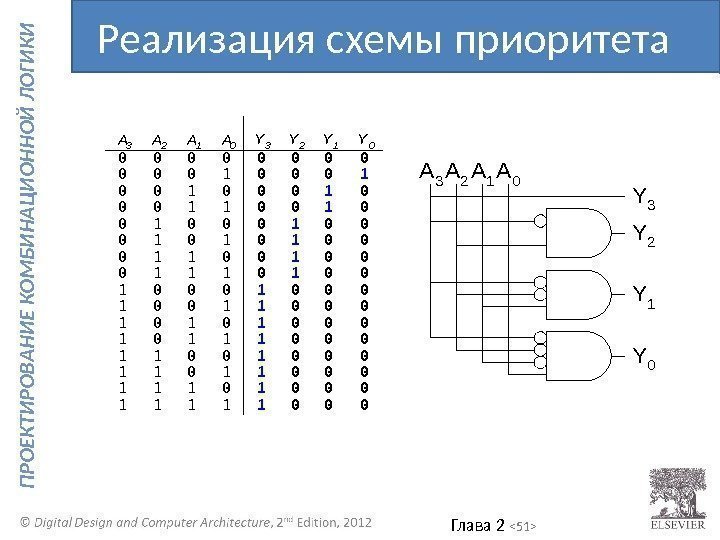

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИРеализация схемы приоритета A 1 A 0 00 01 10 11 0 0 Y 3 Y 2 Y 1 Y 0 0 0 0 1 1 0 0 A 3 A 2 00 00 0001 01 10 11 00 01 01 01 10 0110 10 11 00 01 10 10 11 11 1011 1111 0 0 0 1 1 0 0 0 0 0 1000 1 1 0 0 0 1000 A 3 A 2 A 1 A 0 Y 3 Y 2 Y 1 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИРеализация схемы приоритета A 1 A 0 00 01 10 11 0 0 Y 3 Y 2 Y 1 Y 0 0 0 0 1 1 0 0 A 3 A 2 00 00 0001 01 10 11 00 01 01 01 10 0110 10 11 00 01 10 10 11 11 1011 1111 0 0 0 1 1 0 0 0 0 0 1000 1 1 0 0 0 1000 A 3 A 2 A 1 A 0 Y 3 Y 2 Y 1 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБезразличное значение A 1 A 0 00 01 10 11 0 0 Y 3 Y 2 Y 1 Y 0 0 0 0 1 1 0 0 A 3 A 2 00 00 0001 01 10 11 00 01 01 01 10 0110 10 11 00 01 10 10 11 11 1011 1111 0 0 0 1 1 0 0 0 0 0 1000 1 1 0 0 0 1000 A 1 A 0 00 01 1 X XX 0 0 Y 3 Y 2 Y 1 Y 0 0 1 0 0 A 3 A 2 00 00 00 01 XX 10001 X

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБезразличное значение A 1 A 0 00 01 10 11 0 0 Y 3 Y 2 Y 1 Y 0 0 0 0 1 1 0 0 A 3 A 2 00 00 0001 01 10 11 00 01 01 01 10 0110 10 11 00 01 10 10 11 11 1011 1111 0 0 0 1 1 0 0 0 0 0 1000 1 1 0 0 0 1000 A 1 A 0 00 01 1 X XX 0 0 Y 3 Y 2 Y 1 Y 0 0 1 0 0 A 3 A 2 00 00 00 01 XX 10001 X

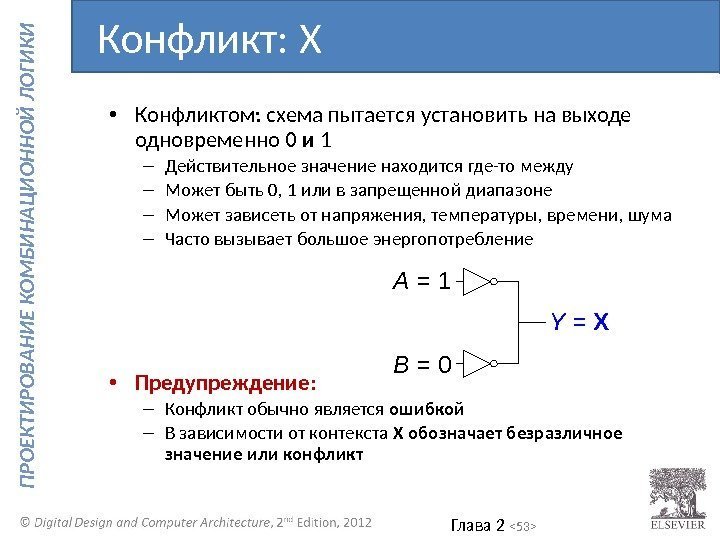

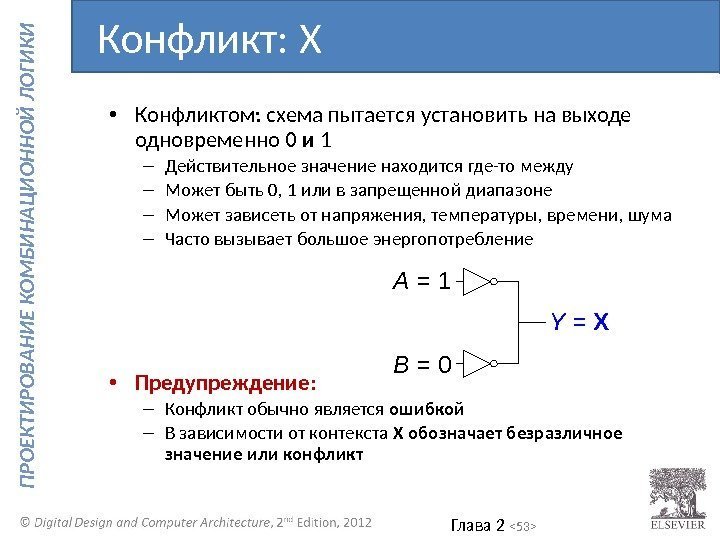

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Конфликтом: схема пытается установить на выходе одновременно 0 и 1 – Действительное значение находится где-то между – Может быть 0, 1 или в запрещенной диапазоне – Может зависеть от напряжения, температуры, времени, шума – Часто вызывает большое энергопотребление • Предупреждение: – Конфликт обычно является ошибкой – В зависимости от контекста X обозначает безразличное значение или конфликт. Конфликт: X A = 1 Y = X B =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Конфликтом: схема пытается установить на выходе одновременно 0 и 1 – Действительное значение находится где-то между – Может быть 0, 1 или в запрещенной диапазоне – Может зависеть от напряжения, температуры, времени, шума – Часто вызывает большое энергопотребление • Предупреждение: – Конфликт обычно является ошибкой – В зависимости от контекста X обозначает безразличное значение или конфликт. Конфликт: X A = 1 Y = X B =

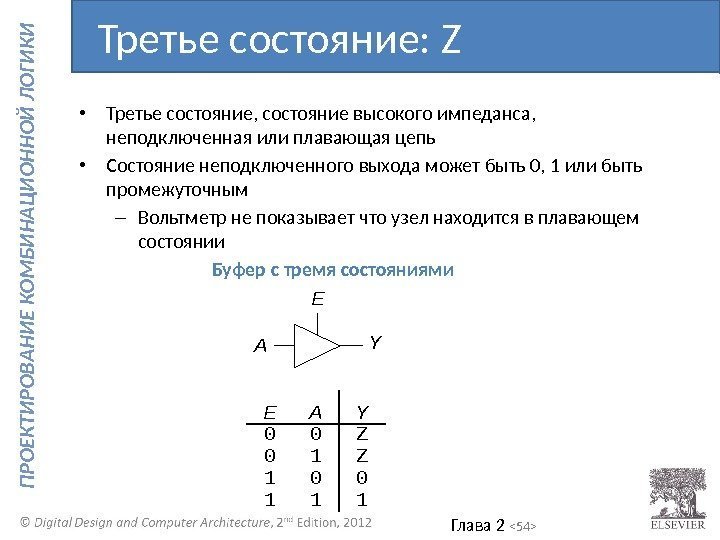

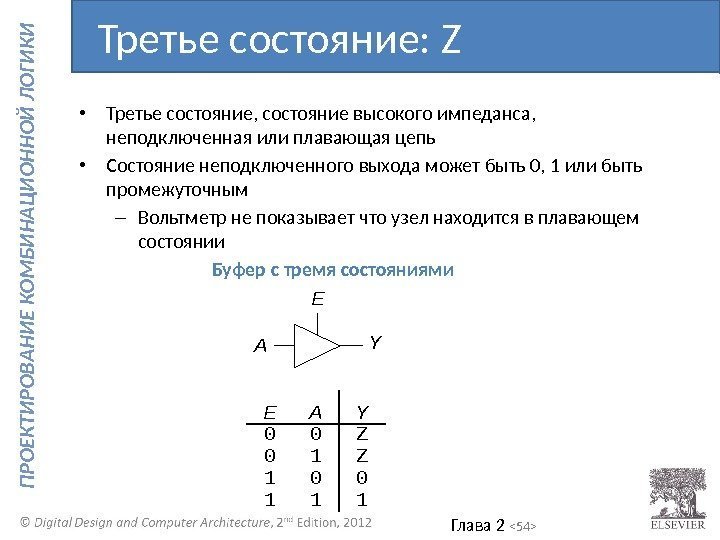

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Третье состояние, состояние высокого импеданса, неподключенная или плавающая цепь • Состояние неподключенного выхода может быть 0, 1 или быть промежуточным – Вольтметр не показывает что узел находится в плавающем состоянии Буфер с тремя состояниями. Третье состояние: Z EAY 00 Z 01 Z 100 111 A E Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Третье состояние, состояние высокого импеданса, неподключенная или плавающая цепь • Состояние неподключенного выхода может быть 0, 1 или быть промежуточным – Вольтметр не показывает что узел находится в плавающем состоянии Буфер с тремя состояниями. Третье состояние: Z EAY 00 Z 01 Z 100 111 A E Y

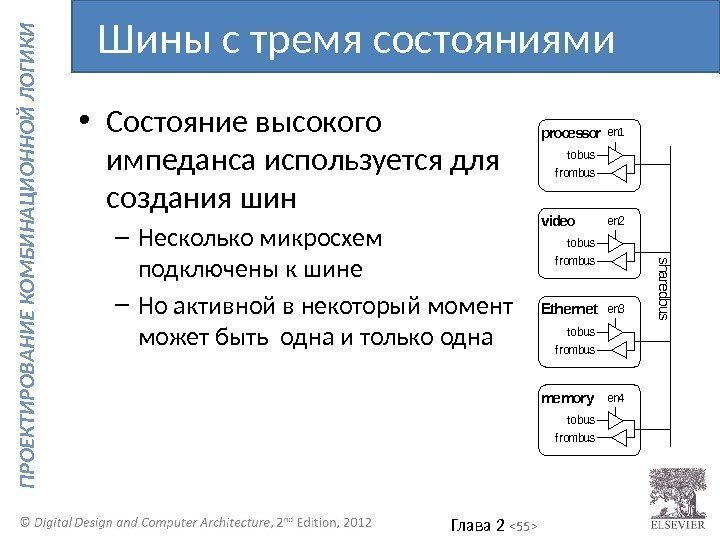

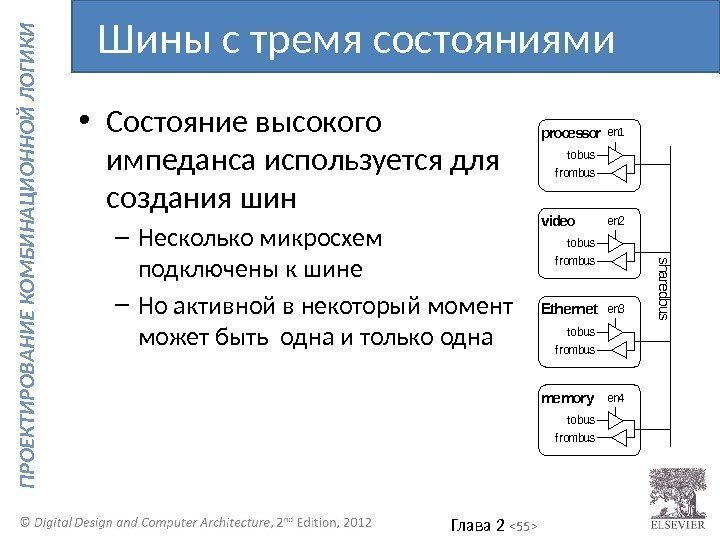

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Состояние высокого импеданса используется для создания шин – Несколько микросхем подключены к шине – Но активной в некоторый момент может быть одна и только одна. Шины с тремя состояниями en 1 to bus from bus en 2 to bus from bus en 3 to bus from bus en 4 to bus from bus shared bus processor video Ethernet memory

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Состояние высокого импеданса используется для создания шин – Несколько микросхем подключены к шине – Но активной в некоторый момент может быть одна и только одна. Шины с тремя состояниями en 1 to bus from bus en 2 to bus from bus en 3 to bus from bus en 4 to bus from bus shared bus processor video Ethernet memory

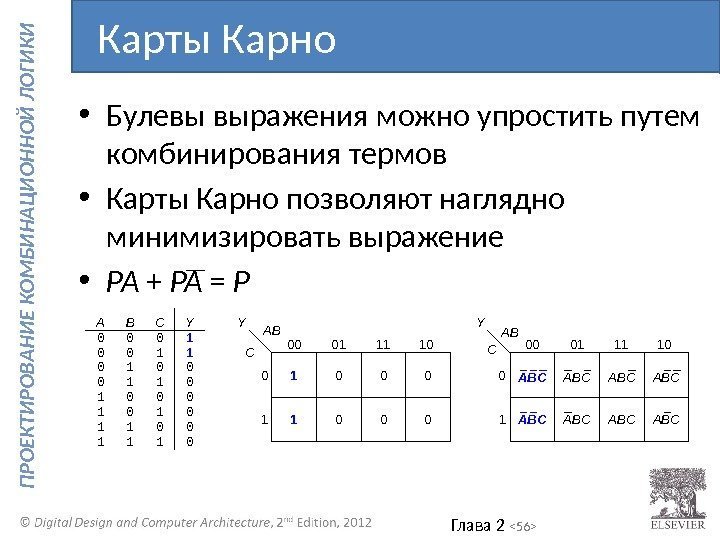

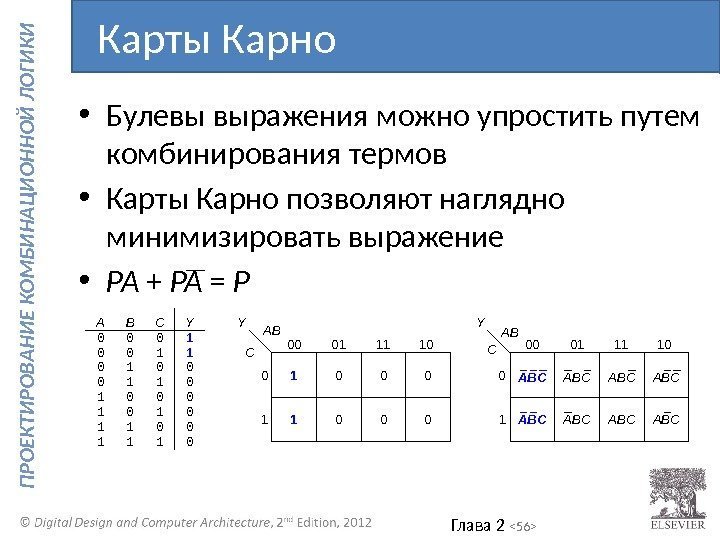

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Булевы выражения можно упростить путем комбинирования термов • Карты Карно позволяют наглядно минимизировать выражение • PA + PA = PКарты Карно C 0001 0 1 Y 1110 AB 1 1 0 0 0 C 0001 0 1 Y 1110 AB ABC ABC BC 00 01 10 11 A 0 0 00 01 10 11 1 1 1 0 0 0 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Булевы выражения можно упростить путем комбинирования термов • Карты Карно позволяют наглядно минимизировать выражение • PA + PA = PКарты Карно C 0001 0 1 Y 1110 AB 1 1 0 0 0 C 0001 0 1 Y 1110 AB ABC ABC BC 00 01 10 11 A 0 0 00 01 10 11 1 1 1 0 0 0 Y

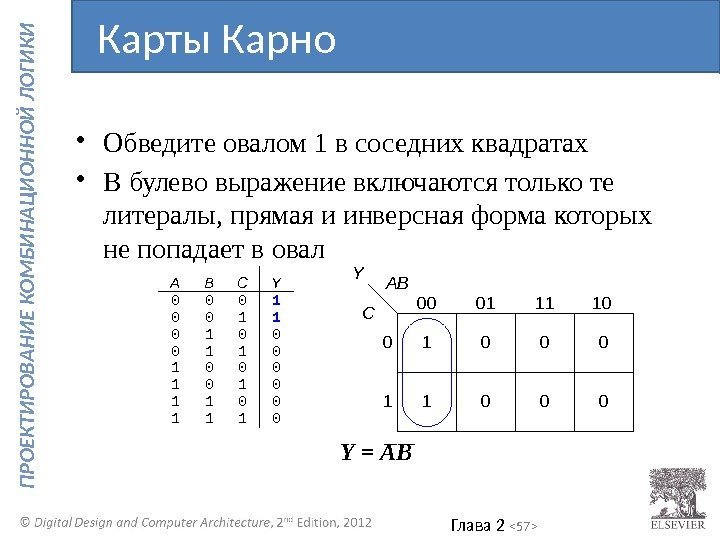

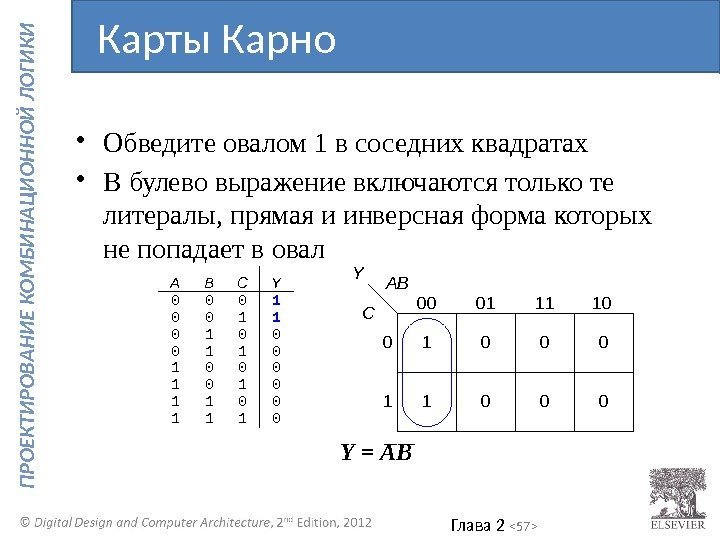

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Обведите овалом 1 в соседних квадратах • В булево выражение включаются только те литералы, прямая и инверсная форма которых не попадает в овал Y = ABКарты Карно C 0001 0 1 Y 1110 AB 1 0 0 0 1 BC 00 01 10 11 A 0 0 00 01 10 11 1 1 1 0 0 0 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Обведите овалом 1 в соседних квадратах • В булево выражение включаются только те литералы, прямая и инверсная форма которых не попадает в овал Y = ABКарты Карно C 0001 0 1 Y 1110 AB 1 0 0 0 1 BC 00 01 10 11 A 0 0 00 01 10 11 1 1 1 0 0 0 Y

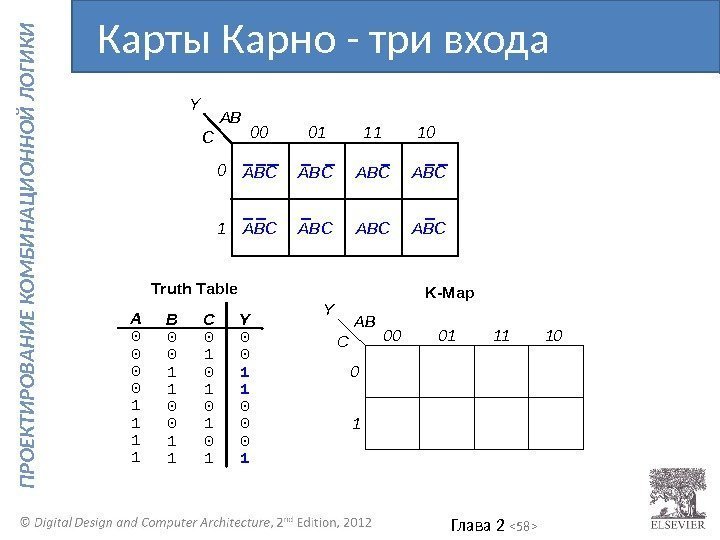

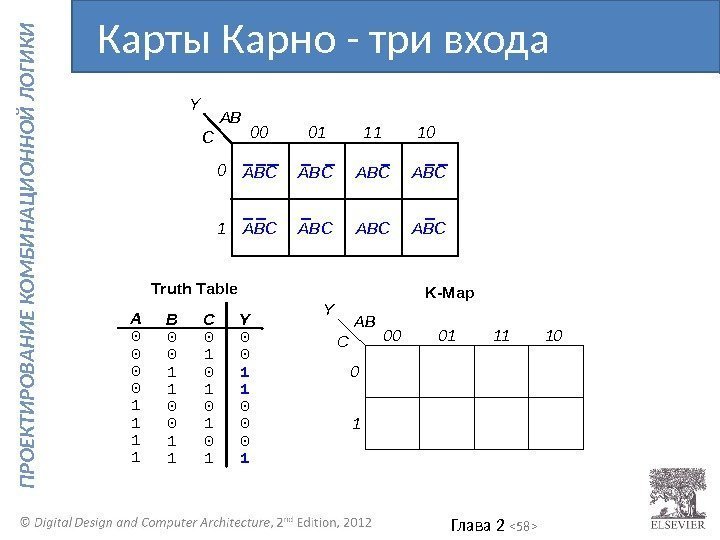

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно — три входа C 0001 0 1 Y 1110 AB ABC ABC 1 BCY 000 010 10 111 Truth Table C 0001 0 1 Y 1110 ABA 0 0 000 010 100 111 1 1 K-Map

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно — три входа C 0001 0 1 Y 1110 AB ABC ABC 1 BCY 000 010 10 111 Truth Table C 0001 0 1 Y 1110 ABA 0 0 000 010 100 111 1 1 K-Map

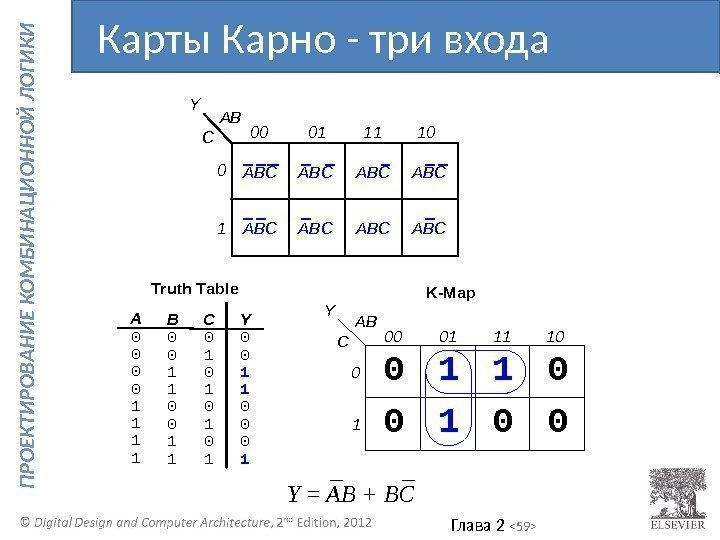

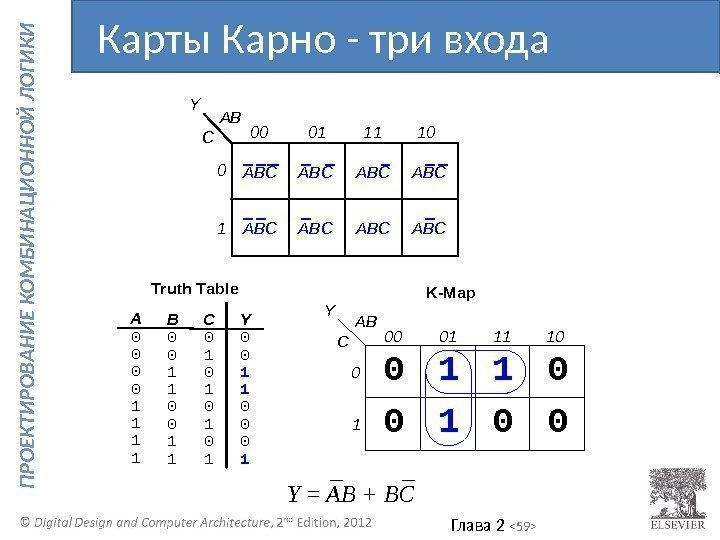

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И Y = AB + BCКарты Карно — три входа C 0001 0 1 Y 1110 AB ABC ABC 10 BCY 000 010 10 111 Truth Table C 0001 0 1 Y 1110 ABA 0 0 000 010 100 111 1 1 0 0 0 K-Map

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И Y = AB + BCКарты Карно — три входа C 0001 0 1 Y 1110 AB ABC ABC 10 BCY 000 010 10 111 Truth Table C 0001 0 1 Y 1110 ABA 0 0 000 010 100 111 1 1 0 0 0 K-Map

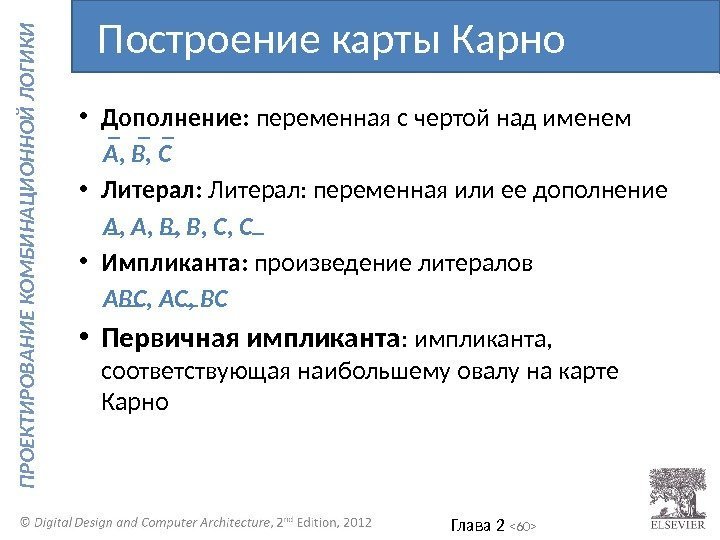

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Дополнение: переменная с чертой над именем A , B , C • Литерал: переменная или ее дополнение A , B , C • Импликанта: произведение литералов ABC , AC , BC • Первичная импликанта : импликанта, соответствующая наибольшему овалу на карте Карно. Построение карты Карно

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Дополнение: переменная с чертой над именем A , B , C • Литерал: переменная или ее дополнение A , B , C • Импликанта: произведение литералов ABC , AC , BC • Первичная импликанта : импликанта, соответствующая наибольшему овалу на карте Карно. Построение карты Карно

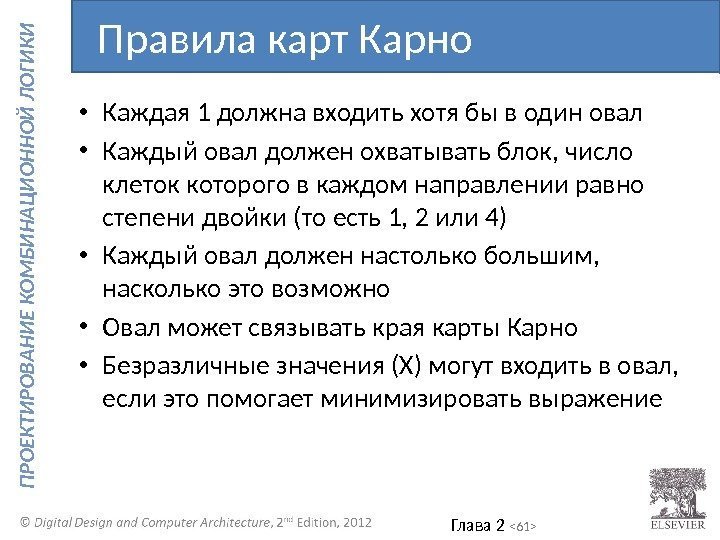

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Каждая 1 должна входить хотя бы в один овал • Каждый овал должен охватывать блок, число клеток которого в каждом направлении равно степени двойки (то есть 1, 2 или 4) • Каждый овал должен настолько большим, насколько это возможно • Овал может связывать края карты Карно • Безразличные значения (X) могут входить в овал, если это помогает минимизировать выражение. Правила карт Карно

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Каждая 1 должна входить хотя бы в один овал • Каждый овал должен охватывать блок, число клеток которого в каждом направлении равно степени двойки (то есть 1, 2 или 4) • Каждый овал должен настолько большим, насколько это возможно • Овал может связывать края карты Карно • Безразличные значения (X) могут входить в овал, если это помогает минимизировать выражение. Правила карт Карно

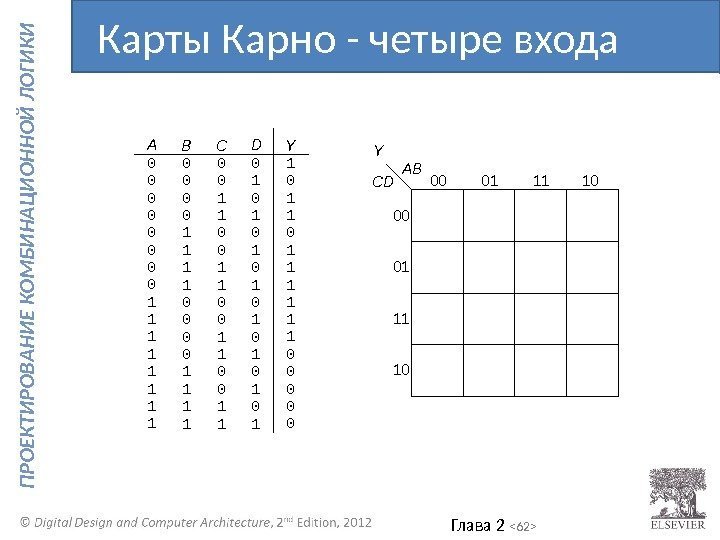

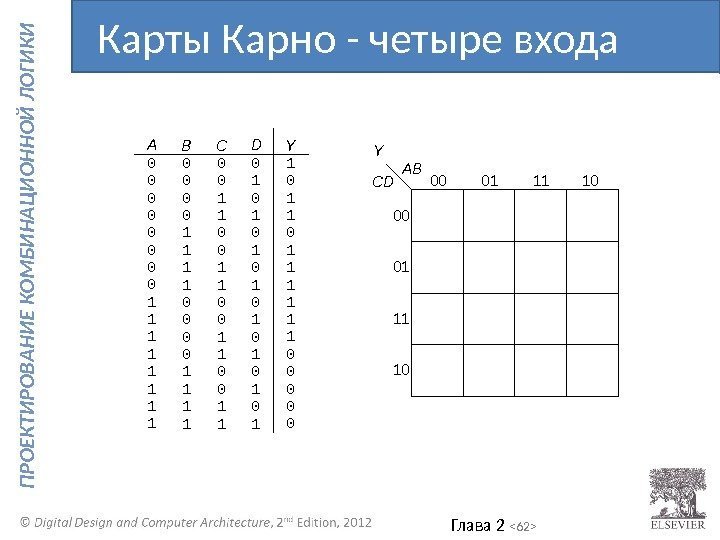

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно — четыре входа 01 11 10 00 00 10 AB CD Y 0 CD 00 01 10 11 B 0 0 00 01 10 11 1 1 1 0 1 1 1 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно — четыре входа 01 11 10 00 00 10 AB CD Y 0 CD 00 01 10 11 B 0 0 00 01 10 11 1 1 1 0 1 1 1 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно — четыре входа 01 11 1 0 0 1 101 1 1 0 0 0 111 10 00 00 10 AB CD Y 0 CD 00 01 10 11 B 0 0 00 01 10 11 1 1 1 0 1 1 1 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно — четыре входа 01 11 1 0 0 1 101 1 1 0 0 0 111 10 00 00 10 AB CD Y 0 CD 00 01 10 11 B 0 0 00 01 10 11 1 1 1 0 1 1 1 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно — четыре входа 01 11 1 0 0 1 101 1 1 0 0 0 111 10 00 00 10 AB CD Y Y = AC + ABD + ABC + BD 0 CD 00 01 10 11 B 0 0 00 01 10 11 1 1 1 0 1 1 1 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно — четыре входа 01 11 1 0 0 1 101 1 1 0 0 0 111 10 00 00 10 AB CD Y Y = AC + ABD + ABC + BD 0 CD 00 01 10 11 B 0 0 00 01 10 11 1 1 1 0 1 1 1 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно и безразличные значения 0 C D 0 0 0 1 1 B 0 0 0 0 1 11 1 1 1 0 X 1 1 YA 0 0 0 1 10 0 0 0 1 11 1 11 X X X 01 11 10 00 00 10 AB CD Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно и безразличные значения 0 C D 0 0 0 1 1 B 0 0 0 0 1 11 1 1 1 0 X 1 1 YA 0 0 0 1 10 0 0 0 1 11 1 11 X X X 01 11 10 00 00 10 AB CD Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно и безразличные значения 0 C D 0 0 0 1 1 B 0 0 0 0 1 11 1 1 1 0 X 1 1 YA 0 0 0 1 10 0 0 0 1 11 1 11 X X X 01 11 1 0 0 X X X 1 101 1 1 X X 11 10 00 00 10 AB CD Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно и безразличные значения 0 C D 0 0 0 1 1 B 0 0 0 0 1 11 1 1 1 0 X 1 1 YA 0 0 0 1 10 0 0 0 1 11 1 11 X X X 01 11 1 0 0 X X X 1 101 1 1 X X 11 10 00 00 10 AB CD Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно и безразличные значения 0 C D 0 0 0 1 1 B 0 0 0 0 1 11 1 1 1 0 X 1 1 YA 0 0 0 1 10 0 0 0 1 11 1 11 X X X 01 11 1 0 0 X X X 1 101 1 1 X X 11 10 00 00 10 AB CD Y Y = A + BD +

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКарты Карно и безразличные значения 0 C D 0 0 0 1 1 B 0 0 0 0 1 11 1 1 1 0 X 1 1 YA 0 0 0 1 10 0 0 0 1 11 1 11 X X X 01 11 1 0 0 X X X 1 101 1 1 X X 11 10 00 00 10 AB CD Y Y = A + BD +

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Мультиплексоры • Дешифраторы. Базовые комбинационные блоки

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Мультиплексоры • Дешифраторы. Базовые комбинационные блоки

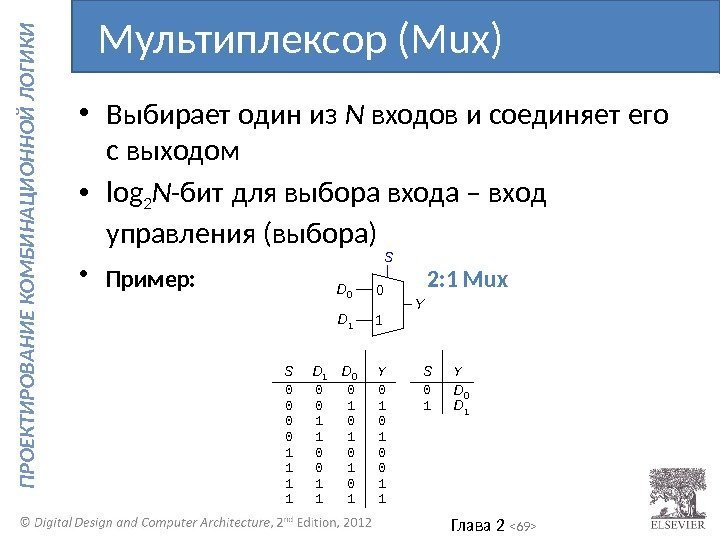

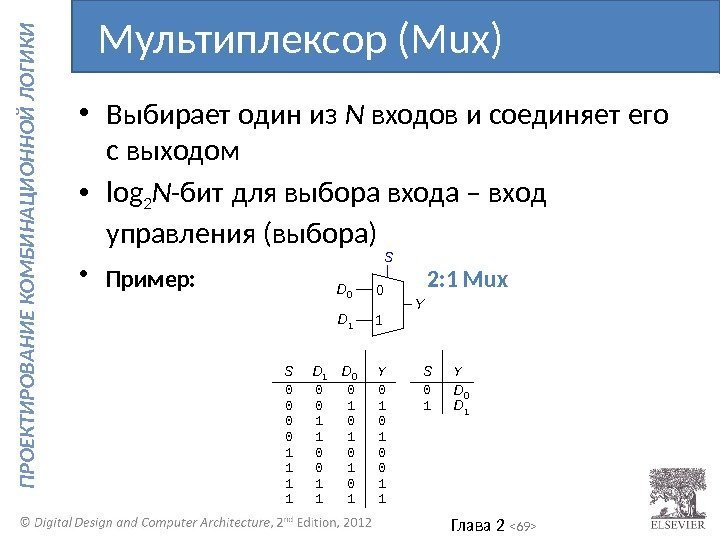

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Выбирает один из N входов и соединяет его с выходом • log 2 N -бит для выбора входа – вход управления (выбора) • Пример: 2: 1 Mux. Мультиплексор (Mux) Y 0 0 0 1 1 0 10 0 0 0 1 11 1 0 0 1 10 1 S D 0 Y D 1 D 0 S Y 0 1 D 1 D 0 S

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Выбирает один из N входов и соединяет его с выходом • log 2 N -бит для выбора входа – вход управления (выбора) • Пример: 2: 1 Mux. Мультиплексор (Mux) Y 0 0 0 1 1 0 10 0 0 0 1 11 1 0 0 1 10 1 S D 0 Y D 1 D 0 S Y 0 1 D 1 D 0 S

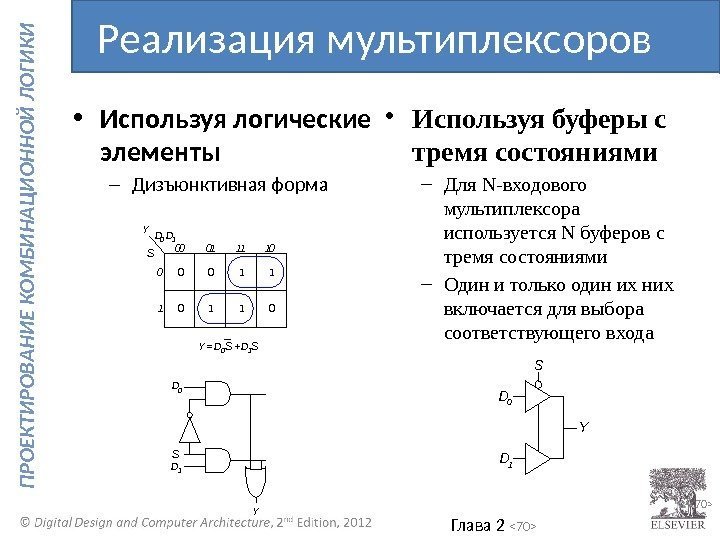

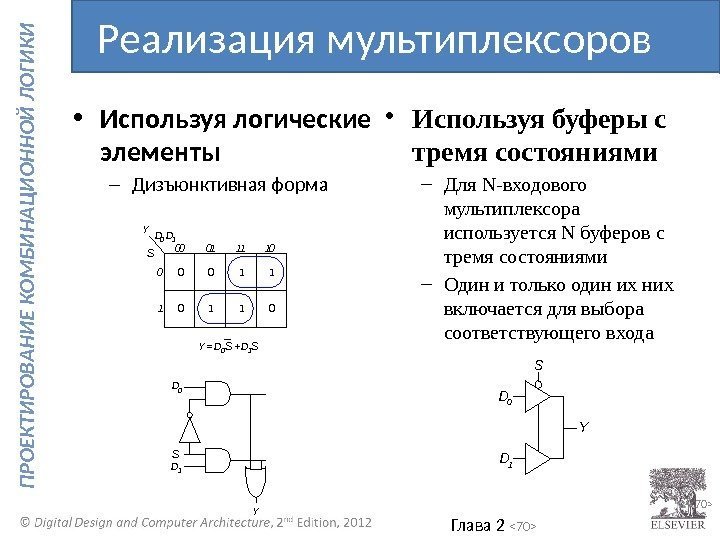

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И 2 — • Используя логические элементы – Дизъюнктивная форма • Используя буферы с тремя состояниями – Для N-входового мультиплексора используется N буферов с тремя состояниями – Один и только один их них включается для выбора соответствующего входа. Реализация мультиплексоров Y D 0 S D 1 YD 0 SS 00 01 0 1 Y 11 10 D 0 D 1 0 0 0 1 1 0 Y = D 0 S + D 1 S

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И 2 — • Используя логические элементы – Дизъюнктивная форма • Используя буферы с тремя состояниями – Для N-входового мультиплексора используется N буферов с тремя состояниями – Один и только один их них включается для выбора соответствующего входа. Реализация мультиплексоров Y D 0 S D 1 YD 0 SS 00 01 0 1 Y 11 10 D 0 D 1 0 0 0 1 1 0 Y = D 0 S + D 1 S

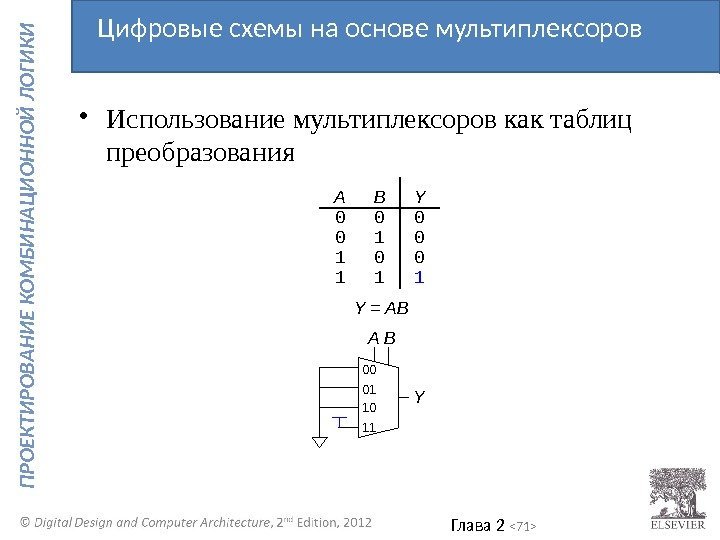

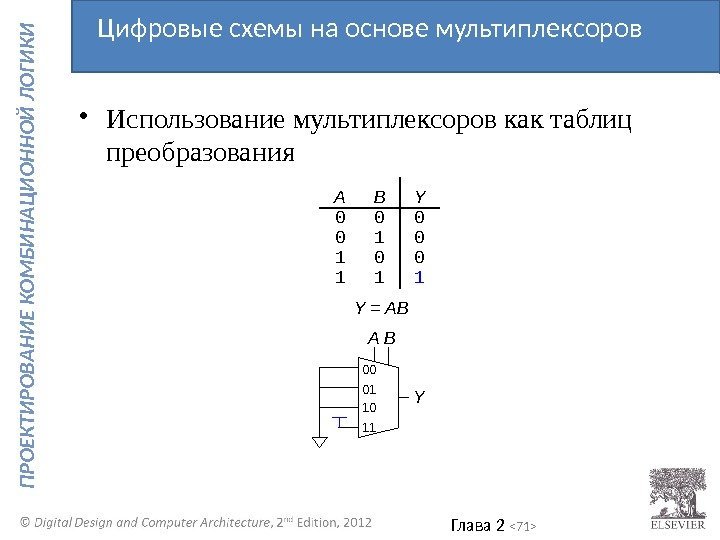

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Использование мультиплексоров как таблиц преобразования. Цифровые схемы на основе мультиплексоров ABY 000 010 100 111 Y = AB 00 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Использование мультиплексоров как таблиц преобразования. Цифровые схемы на основе мультиплексоров ABY 000 010 100 111 Y = AB 00 Y

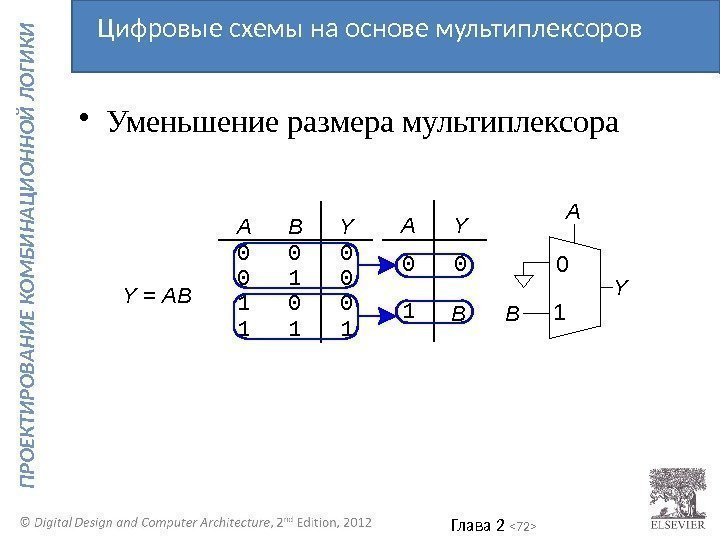

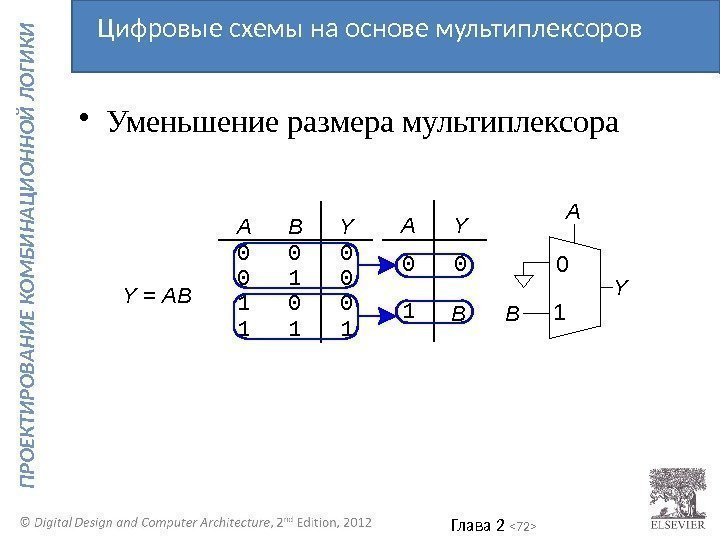

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Уменьшение размера мультиплексора. Цифровые схемы на основе мультиплексоров ABY 000 010 100 111 Y = AB AY 0 1 00 1 A B Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Уменьшение размера мультиплексора. Цифровые схемы на основе мультиплексоров ABY 000 010 100 111 Y = AB AY 0 1 00 1 A B Y

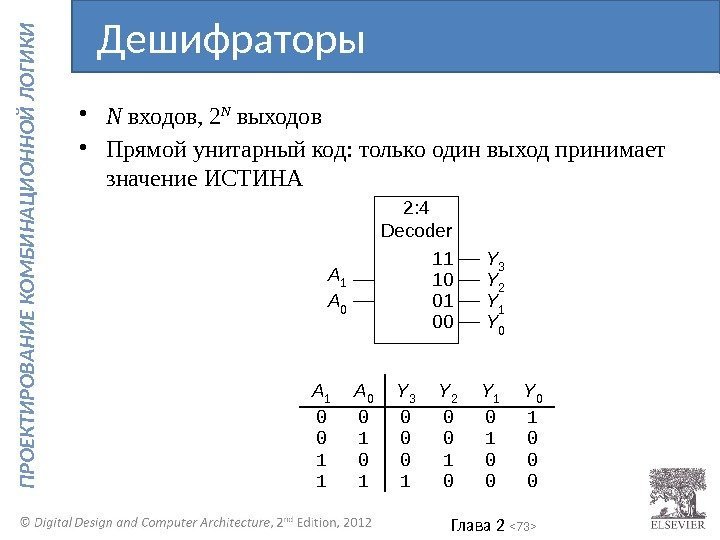

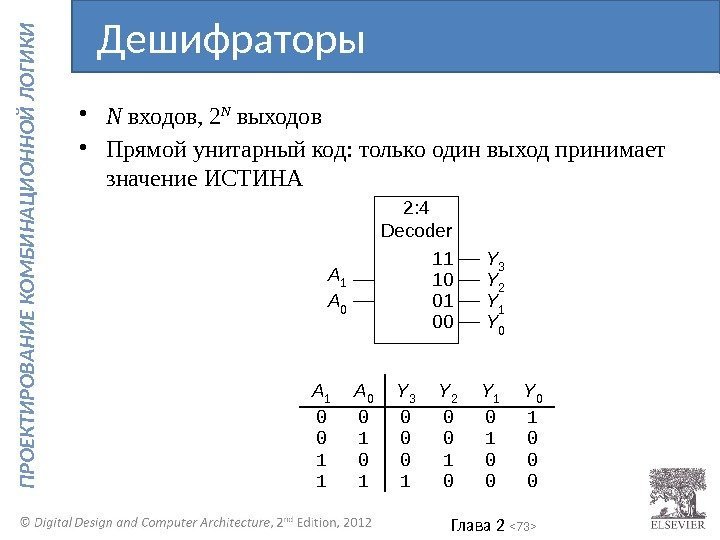

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • N входов, 2 N выходов • Прямой унитарный код: только один выход принимает значение ИСТИНАДешифраторы 2: 4 Decoder A 1 A 0 Y 3 Y 2 Y 1 Y 000 01 10 11 0 0 0 1 Y 3 Y 2 Y 1 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • N входов, 2 N выходов • Прямой унитарный код: только один выход принимает значение ИСТИНАДешифраторы 2: 4 Decoder A 1 A 0 Y 3 Y 2 Y 1 Y 000 01 10 11 0 0 0 1 Y 3 Y 2 Y 1 Y

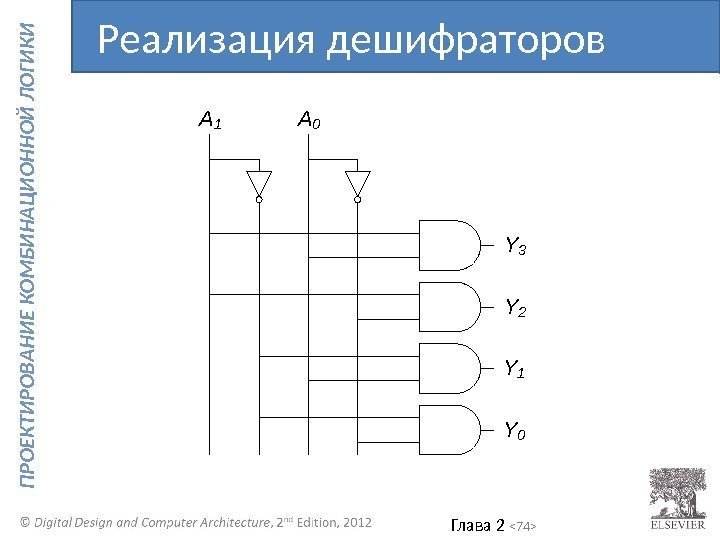

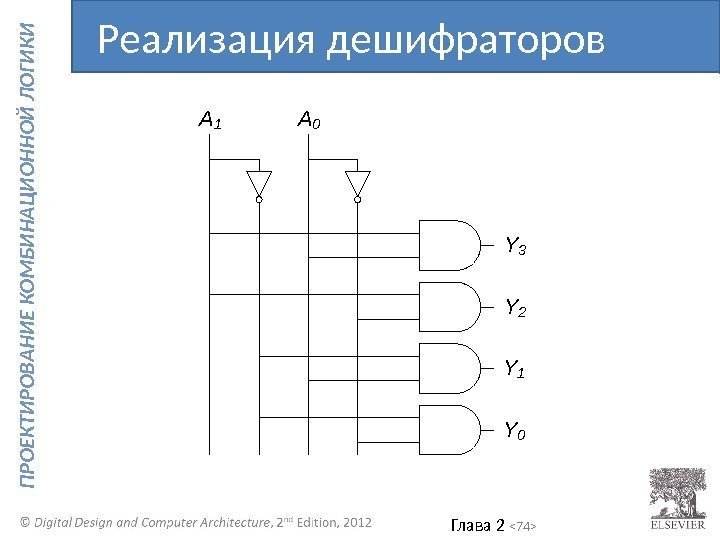

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИРеализация дешифраторов Y 3 Y 2 Y 1 Y

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИРеализация дешифраторов Y 3 Y 2 Y 1 Y

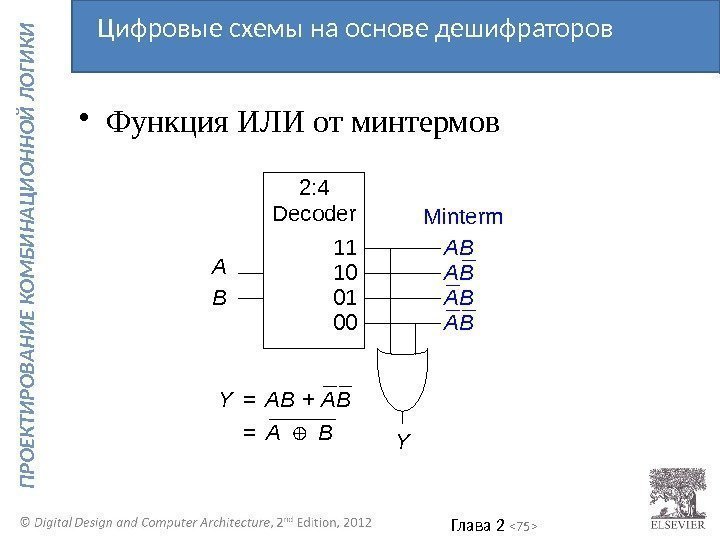

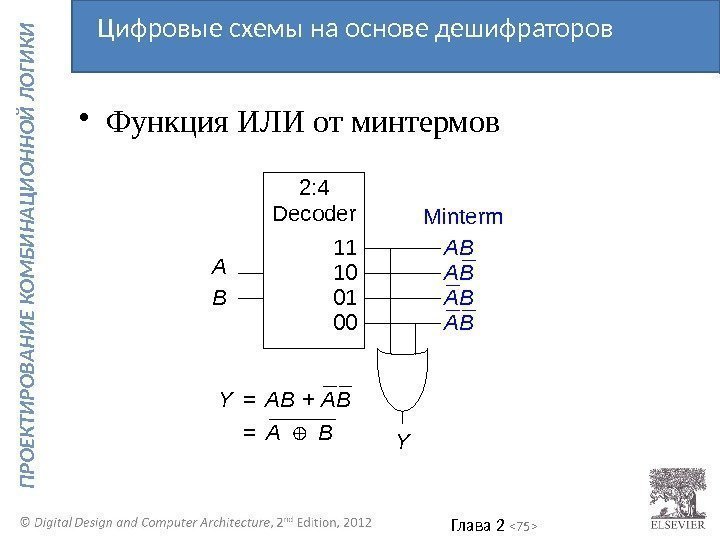

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Функция ИЛИ от минтермов. Цифровые схемы на основе дешифраторов 2: 4 Decoder A B 00 01 10 11 Y=AB + AB Y AB AB Minterm =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Функция ИЛИ от минтермов. Цифровые схемы на основе дешифраторов 2: 4 Decoder A B 00 01 10 11 Y=AB + AB Y AB AB Minterm =

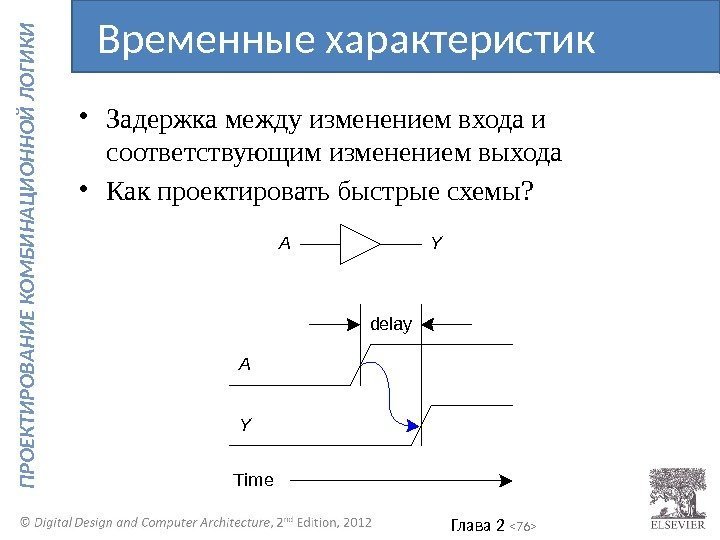

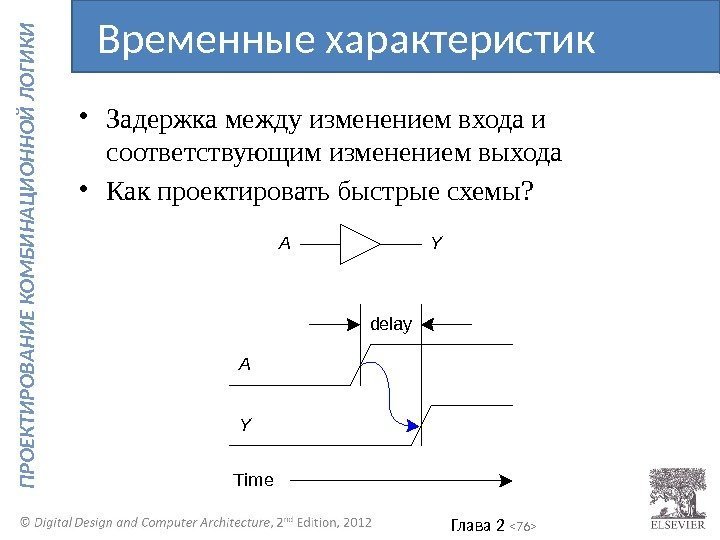

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Задержка между изменением входа и соответствующим изменением выхода • Как проектировать быстрые схемы? Временные характеристик A Y Time delay AY

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Задержка между изменением входа и соответствующим изменением выхода • Как проектировать быстрые схемы? Временные характеристик A Y Time delay AY

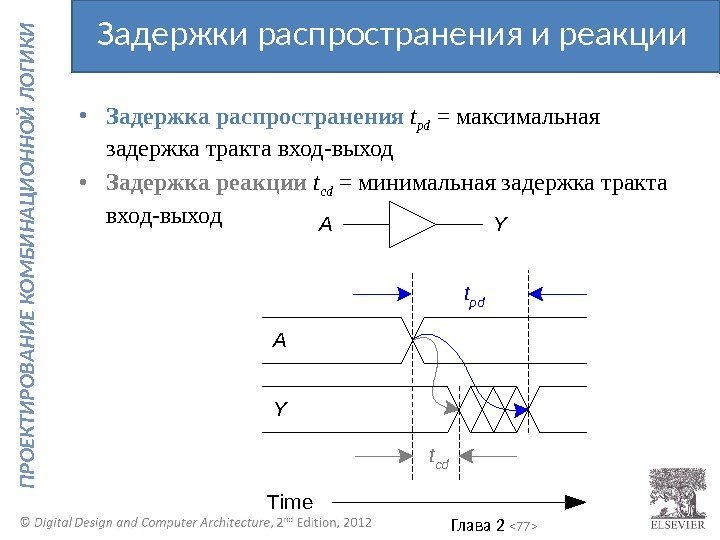

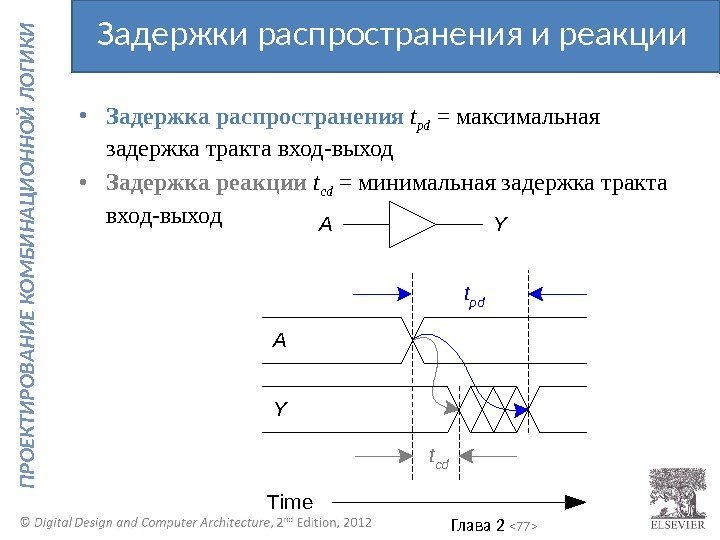

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Задержка распространения t pd = максимальная задержка тракта вход-выход • Задержка реакции t cd = минимальная задержка тракта вход-выход. Задержки распространения и реакции A Y Time AY tpd tcd

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Задержка распространения t pd = максимальная задержка тракта вход-выход • Задержка реакции t cd = минимальная задержка тракта вход-выход. Задержки распространения и реакции A Y Time AY tpd tcd

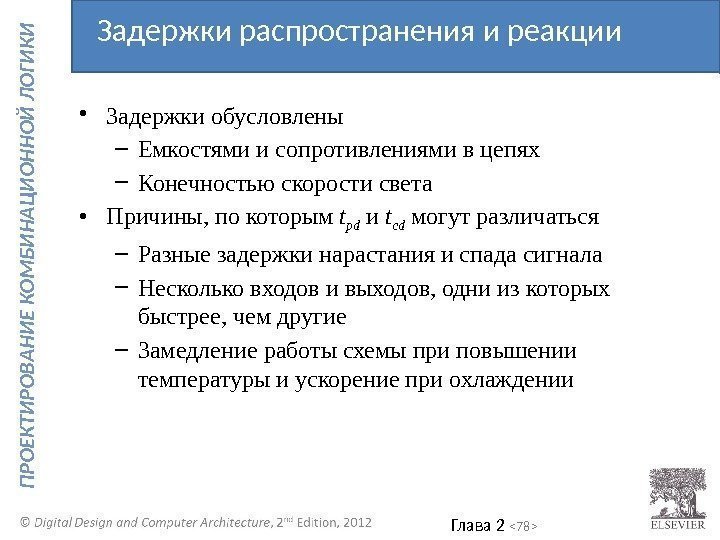

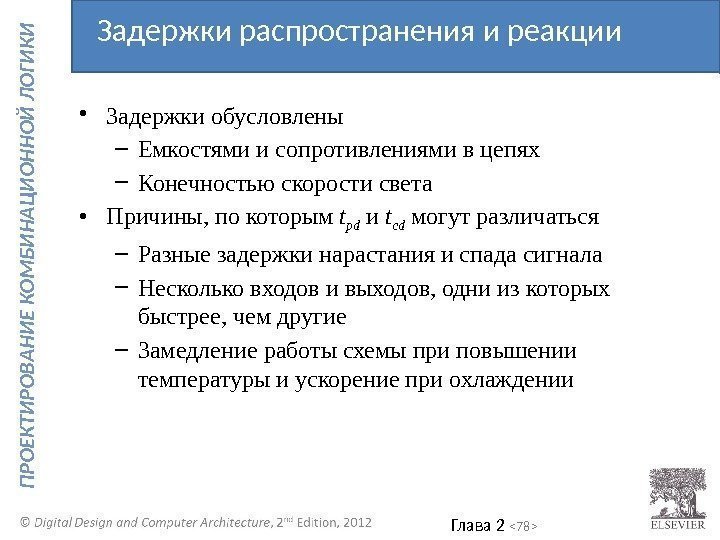

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Задержки обусловлены – Емкостями и сопротивлениями в цепях – Конечностью скорости света • Причины, по которым t pd и t cd могут различаться – Разные задержки нарастания и спада сигнала – Несколько входов и выходов, одни из которых быстрее, чем другие – Замедление работы схемы при повышении температуры и ускорение при охлаждении Задержки распространения и реакции

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Задержки обусловлены – Емкостями и сопротивлениями в цепях – Конечностью скорости света • Причины, по которым t pd и t cd могут различаться – Разные задержки нарастания и спада сигнала – Несколько входов и выходов, одни из которых быстрее, чем другие – Замедление работы схемы при повышении температуры и ускорение при охлаждении Задержки распространения и реакции

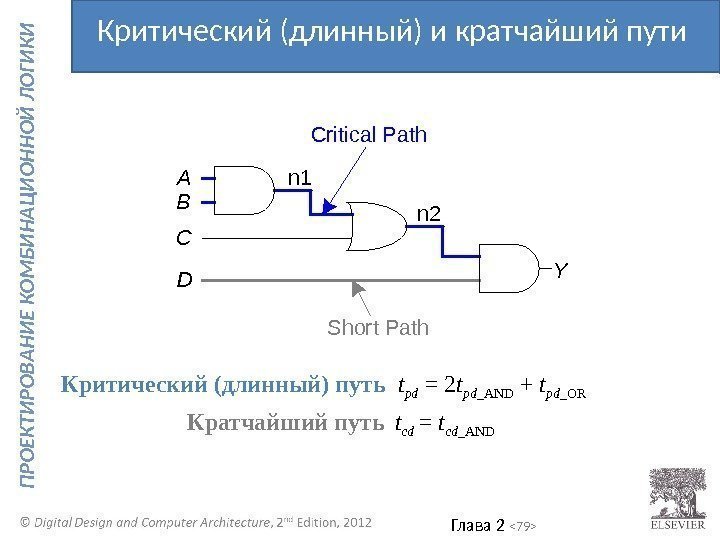

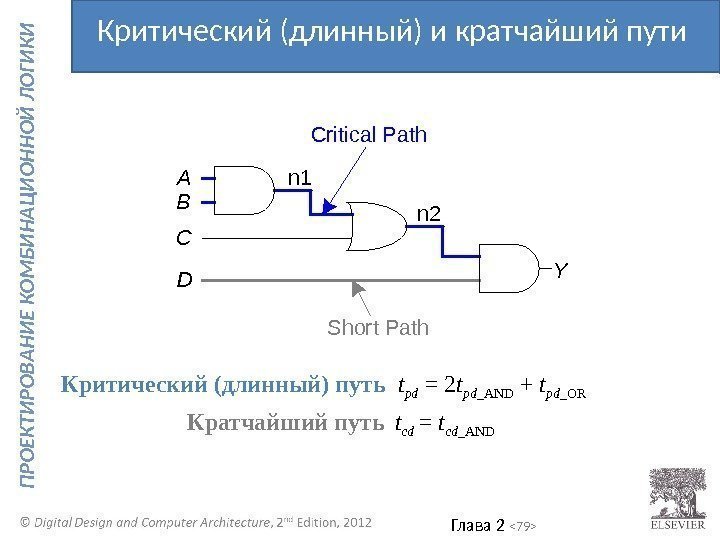

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКритический (длинный) путь t pd = 2 t pd _AND + t pd _OR Кратчайший путь t cd = t cd _ANDКритический (длинный) и кратчайший пути A B C DY Critical Path Short Path n 1 n

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИКритический (длинный) путь t pd = 2 t pd _AND + t pd _OR Кратчайший путь t cd = t cd _ANDКритический (длинный) и кратчайший пути A B C DY Critical Path Short Path n 1 n

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Одиночное изменение на входного сигнала вызывает несколько изменений сигнала на выходе. Импульсные помехи

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Одиночное изменение на входного сигнала вызывает несколько изменений сигнала на выходе. Импульсные помехи

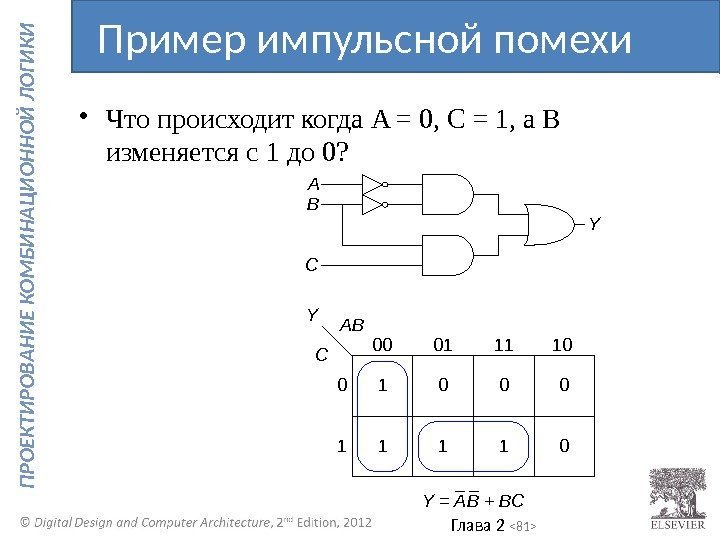

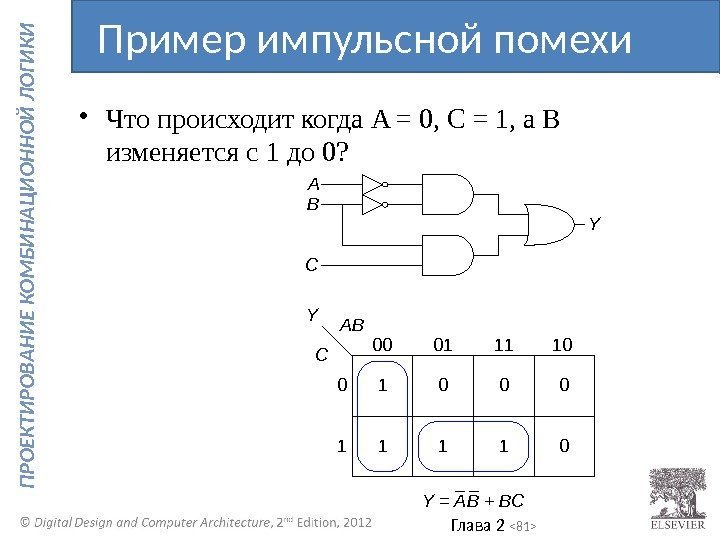

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Что происходит когда A = 0, C = 1, а B изменяется с 1 до 0? Пример импульсной помехи A B C Y 0001 1 Y 1110 AB 1 1 0 1 0 0 C 0 Y = AB +

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Что происходит когда A = 0, C = 1, а B изменяется с 1 до 0? Пример импульсной помехи A B C Y 0001 1 Y 1110 AB 1 1 0 1 0 0 C 0 Y = AB +

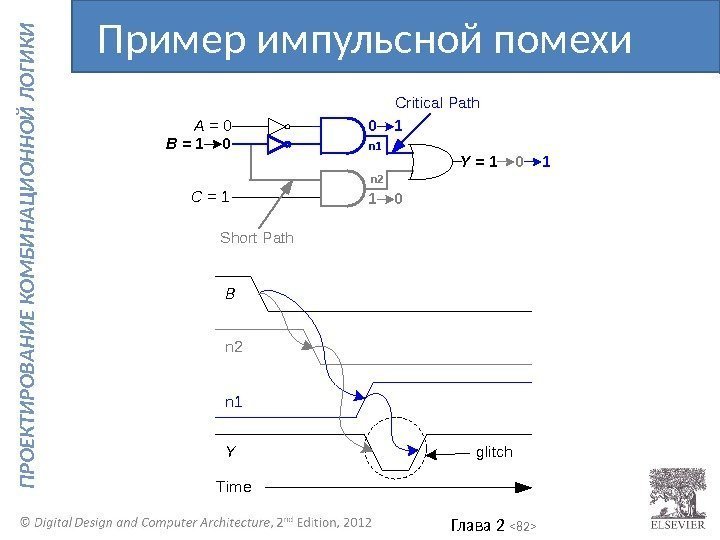

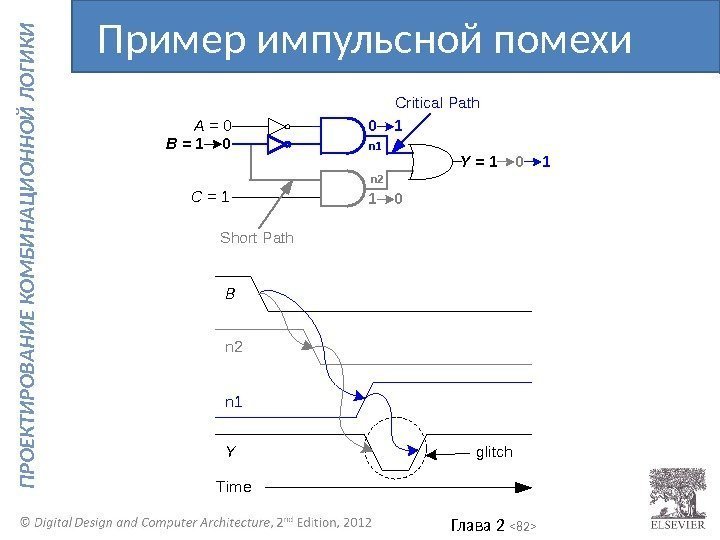

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИПример импульсной помехи (продолжение) A = 0 B = 1 0 C = 1 Y = 1 0 1 Short Path Critical Path B Y Time 1 00 1 glitchn 1 n 2 n

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИПример импульсной помехи (продолжение) A = 0 B = 1 0 C = 1 Y = 1 0 1 Short Path Critical Path B Y Time 1 00 1 glitchn 1 n 2 n

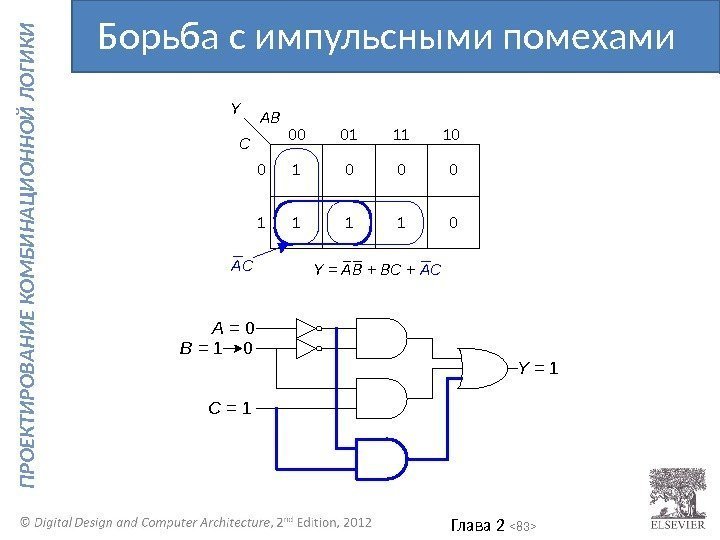

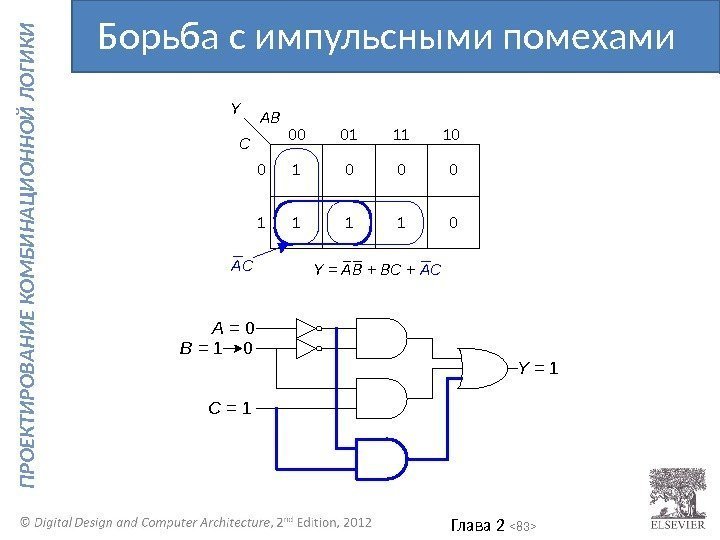

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБорьба с импульсными помехами 00 01 1 Y 11 10 AB 1 1 0 1 0 0 C 0 Y = AB + BC + ACAC B = 1 0 Y = 1 A = 0 C =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К ИБорьба с импульсными помехами 00 01 1 Y 11 10 AB 1 1 0 1 0 0 C 0 Y = AB + BC + ACAC B = 1 0 Y = 1 A = 0 C =

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Импульсные помехи не являются серьезной проблемой при проектировании синхронных схем (глава 3) • Важно уметь распознавать их при моделировании или на экране осциллографа • От всех импульсных помех невозможно избавиться — одновременные изменения нескольких входов могут привести к появлению таких помех. Почему импульсные помехи важны?

Глава 2 П Р О Е К Т И Р О В А Н И Е К О М Б И Н А Ц И О Н Н О Й Л О ГИ К И • Импульсные помехи не являются серьезной проблемой при проектировании синхронных схем (глава 3) • Важно уметь распознавать их при моделировании или на экране осциллографа • От всех импульсных помех невозможно избавиться — одновременные изменения нескольких входов могут привести к появлению таких помех. Почему импульсные помехи важны?