Организация ЭВМ Организация систем ввода-вывода (input-output systems) Организация

9466-io_sys.ppt

- Количество слайдов: 21

Организация ЭВМ Организация систем ввода-вывода (input-output systems)

Организация ЭВМ Организация систем ввода-вывода (input-output systems)

Организация ЭВМ План 1. Назначение системы ввода-вывода 2. Состав системы ввода-вывода 3. Варианты обмена в СВВ 4. Система прерываний 5. Шинно-мостовая организация СВВ 6. Системные шины и стандартные внешние интерфейсы 7. Организация чипсетов

Организация ЭВМ План 1. Назначение системы ввода-вывода 2. Состав системы ввода-вывода 3. Варианты обмена в СВВ 4. Система прерываний 5. Шинно-мостовая организация СВВ 6. Системные шины и стандартные внешние интерфейсы 7. Организация чипсетов

Организация ЭВМ 1 Назначение системы ввода - вывода Система ввода-вывода (СВВ) предназна-чена для выполнения трех из пяти основных функций ВМ: - ввода информации, - вывода информации, - долговременного хранения информации

Организация ЭВМ 1 Назначение системы ввода - вывода Система ввода-вывода (СВВ) предназна-чена для выполнения трех из пяти основных функций ВМ: - ввода информации, - вывода информации, - долговременного хранения информации

Организация ЭВМ 2 Состав системы ввода - вывода 1. Периферийные устройства - устройства ввода (включая HID); - устройства вывода (включая HID); - устройства долговременного хранения информации. 2 .Контроллеры (адаптеры) периферийных устройств, отвечающие за управление периферийными устройствами и обмен между ними и ядром ЭВМ. 3. Внешние параллельные и последовательные каналы обмена и соответствующие контроллеры этих каналов. 4. Системные шины и их контроллеры. 5. Контроллеры прерываний и прямого доступа к памяти (ПДП). 6. Подсистемы процессора, отвечающие за ввод/вывод, организацию ПДП и реакцию на прерывания и др.

Организация ЭВМ 2 Состав системы ввода - вывода 1. Периферийные устройства - устройства ввода (включая HID); - устройства вывода (включая HID); - устройства долговременного хранения информации. 2 .Контроллеры (адаптеры) периферийных устройств, отвечающие за управление периферийными устройствами и обмен между ними и ядром ЭВМ. 3. Внешние параллельные и последовательные каналы обмена и соответствующие контроллеры этих каналов. 4. Системные шины и их контроллеры. 5. Контроллеры прерываний и прямого доступа к памяти (ПДП). 6. Подсистемы процессора, отвечающие за ввод/вывод, организацию ПДП и реакцию на прерывания и др.

Организация ЭВМ 3 Варианты обмена в системах ввода - вывода 1. Программный обмен/опрос (поллинг – Program Polling) – ЦП опрашивает готовность ВУ к обмену и при его готовности выполняет сеанс обмена байтом (словом) или блоком слов. 2. Обмен по прерываниям (Interrupt Request) – ВУ формирует сигнал прерывания, когда оно готово к обмену, процессор получает сигнал прерывания и начинает его обработку, реализуя сеанс обмена. 3. Обмен через прямой доступ к памяти (ПДП – Direct Memory Access) – ЦП не участвует в обмене, или почти не участвует – обменом управляет контроллер ПДП, сам обмен происходит в те такты, когда процессор не работает с системной шиной – происходит передача блока данных из ВУ в память или наоборот под управлением контроллера ПДП.

Организация ЭВМ 3 Варианты обмена в системах ввода - вывода 1. Программный обмен/опрос (поллинг – Program Polling) – ЦП опрашивает готовность ВУ к обмену и при его готовности выполняет сеанс обмена байтом (словом) или блоком слов. 2. Обмен по прерываниям (Interrupt Request) – ВУ формирует сигнал прерывания, когда оно готово к обмену, процессор получает сигнал прерывания и начинает его обработку, реализуя сеанс обмена. 3. Обмен через прямой доступ к памяти (ПДП – Direct Memory Access) – ЦП не участвует в обмене, или почти не участвует – обменом управляет контроллер ПДП, сам обмен происходит в те такты, когда процессор не работает с системной шиной – происходит передача блока данных из ВУ в память или наоборот под управлением контроллера ПДП.

Организация ЭВМ 3.1 Программный обмен Обмен реализуется специальными командами типа IN rgX, portY и OUT portY, rgX В устройстве выделяются порты : регистры данных, управления и информационные. В регистры данных записывается и из них считывается информация. Информационные регистры служат в основном для определения состояния устройства. Регистры управления позволяют управлять устройством и ходом обмена. Номер порта выдается на шину адреса ЦП, данные из регистра (или из устройства) выдаются на шину данных

Организация ЭВМ 3.1 Программный обмен Обмен реализуется специальными командами типа IN rgX, portY и OUT portY, rgX В устройстве выделяются порты : регистры данных, управления и информационные. В регистры данных записывается и из них считывается информация. Информационные регистры служат в основном для определения состояния устройства. Регистры управления позволяют управлять устройством и ходом обмена. Номер порта выдается на шину адреса ЦП, данные из регистра (или из устройства) выдаются на шину данных

Организация ЭВМ 3.2 Программный обмен – алгоритм базового сеанса обмена одним словом Запросить готовность ВУ, считав данные из информационного порта или порта управления Проверить бит готовности из слова состояния устройства Если устройство готово, записать очередной байт (слово) в порт данных, или считать слово из порта данных при реализации обмена, либо – записать команду в порт управления при инициализации обмена.

Организация ЭВМ 3.2 Программный обмен – алгоритм базового сеанса обмена одним словом Запросить готовность ВУ, считав данные из информационного порта или порта управления Проверить бит готовности из слова состояния устройства Если устройство готово, записать очередной байт (слово) в порт данных, или считать слово из порта данных при реализации обмена, либо – записать команду в порт управления при инициализации обмена.

Организация ЭВМ 3.3 Программный обмен – схема реализации (см. на доску )

Организация ЭВМ 3.3 Программный обмен – схема реализации (см. на доску )

Организация ЭВМ 4 Прерывания Прерывание – это реакция ЭВМ на некоторое внутреннее или внешнее событие, приводящая к приостановке выполнения текущей программы и инициированию выполнения новой программы, специально предназначенной для данного события. Типы прерываний : Внешнее – инициируется внешним устройством. Программное прерывание – для вызова системных функций Исключение – генерируется в случае ошибок

Организация ЭВМ 4 Прерывания Прерывание – это реакция ЭВМ на некоторое внутреннее или внешнее событие, приводящая к приостановке выполнения текущей программы и инициированию выполнения новой программы, специально предназначенной для данного события. Типы прерываний : Внешнее – инициируется внешним устройством. Программное прерывание – для вызова системных функций Исключение – генерируется в случае ошибок

Организация ЭВМ 4.1 Обработка прерываний Основные этапы выполнения прерываний : Запоминание состояния прерываемой программы. Определение адреса подпрограммы-обработчика прерывания (вектора прерывания). Переход к выполнению подпрограммы обработки прерывания. Восстановление состояния прерванной программы и возврат к ней.

Организация ЭВМ 4.1 Обработка прерываний Основные этапы выполнения прерываний : Запоминание состояния прерываемой программы. Определение адреса подпрограммы-обработчика прерывания (вектора прерывания). Переход к выполнению подпрограммы обработки прерывания. Восстановление состояния прерванной программы и возврат к ней.

Организация ЭВМ 4.2 Характеристики системы прерываний Общее число возможных запросов. Число уровней или классов прерываний. Глубина прерываний – максимальное количество запросов, которые могут прерывать друг друга. Время реакции системы прерываний – время от формирования запроса до начала выполнения подпрограммы обслуживания прерывания. Эффективность системы прерываний – отношение времени выполнения подпрограммы обработчика прерывания к общему времени, затрачиваемому на прерывание

Организация ЭВМ 4.2 Характеристики системы прерываний Общее число возможных запросов. Число уровней или классов прерываний. Глубина прерываний – максимальное количество запросов, которые могут прерывать друг друга. Время реакции системы прерываний – время от формирования запроса до начала выполнения подпрограммы обслуживания прерывания. Эффективность системы прерываний – отношение времени выполнения подпрограммы обработчика прерывания к общему времени, затрачиваемому на прерывание

Организация ЭВМ 5 Интерфейсы, шины и мосты Шина (bus) - многоразрядный интерфейс для обмена информацией. Как правило, включает линии данных, адреса и управления. Интерфейс (interface) – совокупность средств, методов и правил взаимодействия между подсистемами. Мост (bridge) – подсистема для согласования различных интерфейсов (как и адаптер, но там – согласование двух интерфейсов)

Организация ЭВМ 5 Интерфейсы, шины и мосты Шина (bus) - многоразрядный интерфейс для обмена информацией. Как правило, включает линии данных, адреса и управления. Интерфейс (interface) – совокупность средств, методов и правил взаимодействия между подсистемами. Мост (bridge) – подсистема для согласования различных интерфейсов (как и адаптер, но там – согласование двух интерфейсов)

Организация ЭВМ 5 Описание (аппаратного) интерфейса логическое описание (количество и назначение используемых разрядов); физическое описание (количество разрядов, способ физического сопряжения с интерфейсом); электрическое описание (используемые уровни сигналов и др.); протокольное описание (алгоритмическое, описывает динамику выставления, снятия и взаимозависимости сигналов интерфейса).

Организация ЭВМ 5 Описание (аппаратного) интерфейса логическое описание (количество и назначение используемых разрядов); физическое описание (количество разрядов, способ физического сопряжения с интерфейсом); электрическое описание (используемые уровни сигналов и др.); протокольное описание (алгоритмическое, описывает динамику выставления, снятия и взаимозависимости сигналов интерфейса).

Организация ЭВМ 6.1 Системная шина Системообразующий внутренний интерфейс, к которому обычно (по крайней мере - раньше) подключалось ядро ЭВМ и контроллеры внешних интерфейсов. Примеры системных шин IBM PC совместимых ЭВМ: - ISA (Industrial Standart Architecture); - PCI (Peripheral Components Interconnect); - PCI-Express (или PCI-E).

Организация ЭВМ 6.1 Системная шина Системообразующий внутренний интерфейс, к которому обычно (по крайней мере - раньше) подключалось ядро ЭВМ и контроллеры внешних интерфейсов. Примеры системных шин IBM PC совместимых ЭВМ: - ISA (Industrial Standart Architecture); - PCI (Peripheral Components Interconnect); - PCI-Express (или PCI-E).

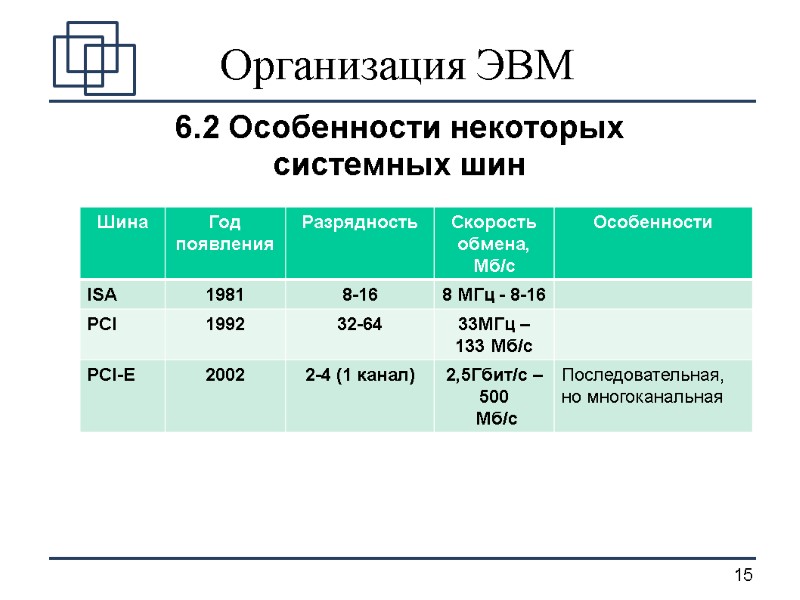

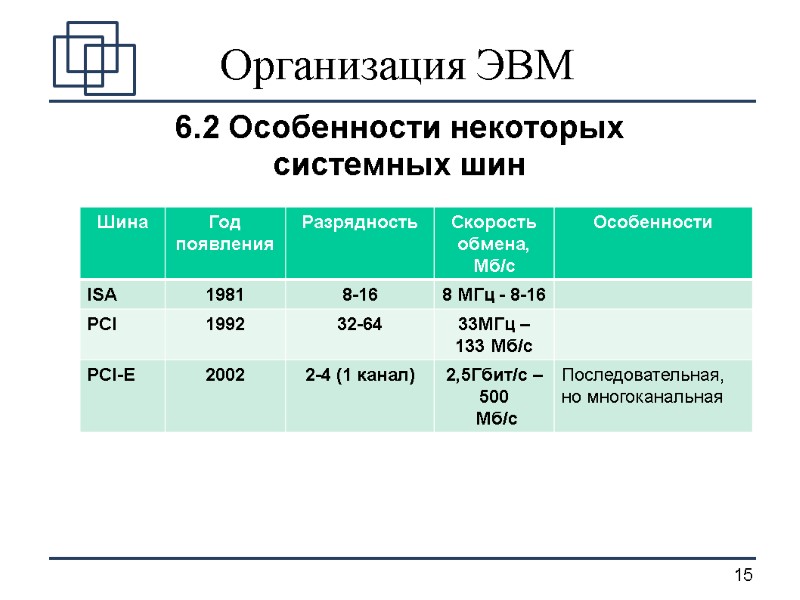

Организация ЭВМ 6.2 Особенности некоторых системных шин

Организация ЭВМ 6.2 Особенности некоторых системных шин

Организация ЭВМ 6.3 Внешние интерфейсы ЭВМ Выделяют последовательные и параллельные интерфейсы. Распространенные последовательные шины : - USB (Universal Serial Bus) : 1.1, 2.0, 3.0; - SATA (Serial ATA); - SAS (Serial Attached SCSI); - RS232 (COM); - PS/2 и др. Распространенные параллельные шины : - IDE (Integrated Device Electronics); - ATA (AT Attachment), UDMA33/66/100/133; - SCSI (Small Computer System Interface); - Centronics (LPT); - PC-Card и др.

Организация ЭВМ 6.3 Внешние интерфейсы ЭВМ Выделяют последовательные и параллельные интерфейсы. Распространенные последовательные шины : - USB (Universal Serial Bus) : 1.1, 2.0, 3.0; - SATA (Serial ATA); - SAS (Serial Attached SCSI); - RS232 (COM); - PS/2 и др. Распространенные параллельные шины : - IDE (Integrated Device Electronics); - ATA (AT Attachment), UDMA33/66/100/133; - SCSI (Small Computer System Interface); - Centronics (LPT); - PC-Card и др.

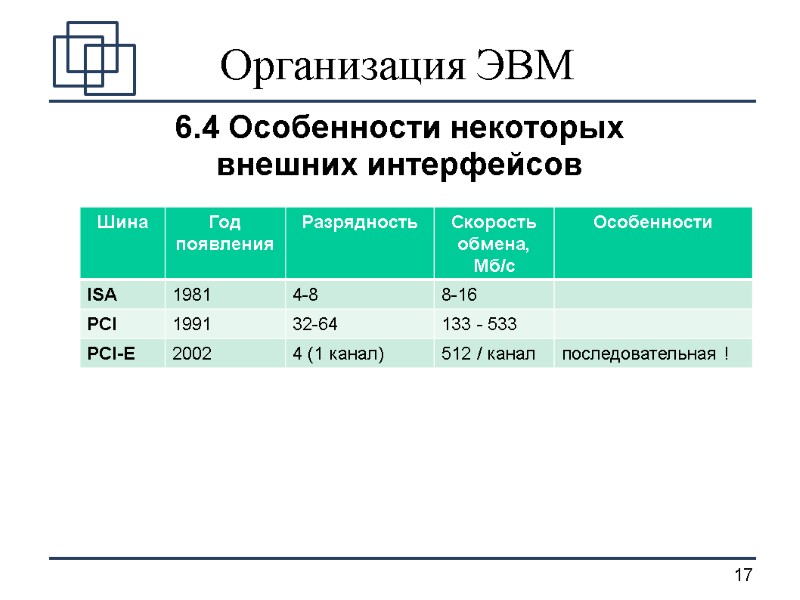

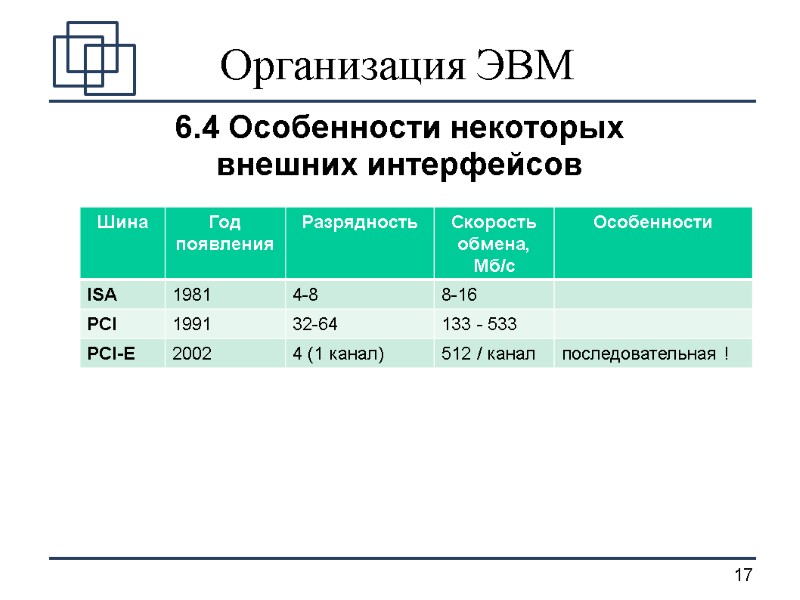

Организация ЭВМ 6.4 Особенности некоторых внешних интерфейсов

Организация ЭВМ 6.4 Особенности некоторых внешних интерфейсов

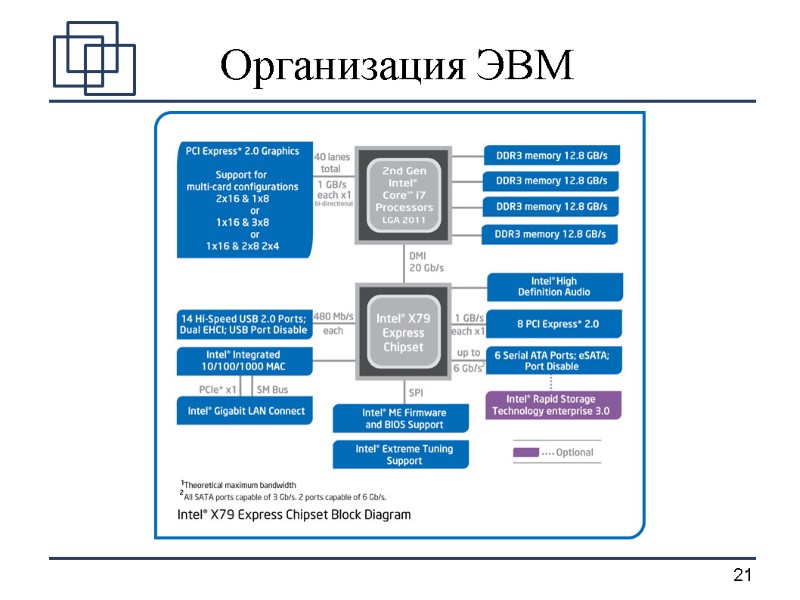

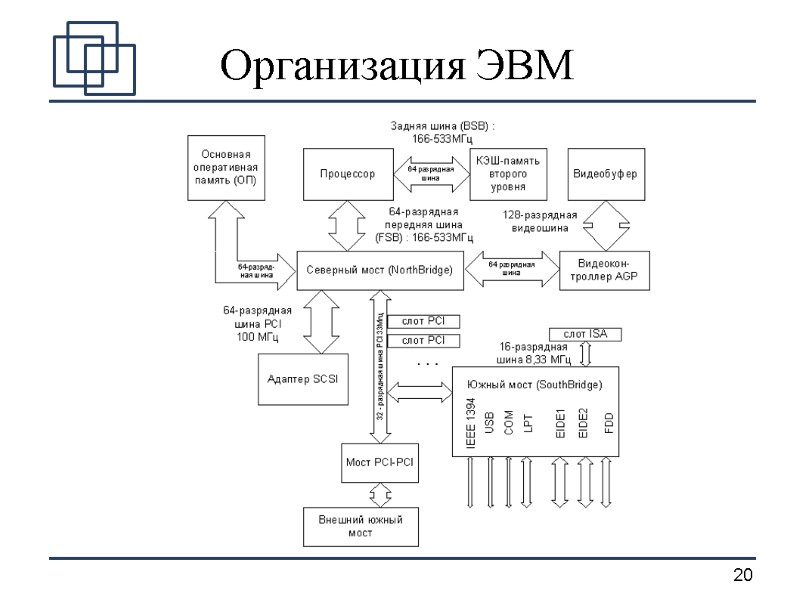

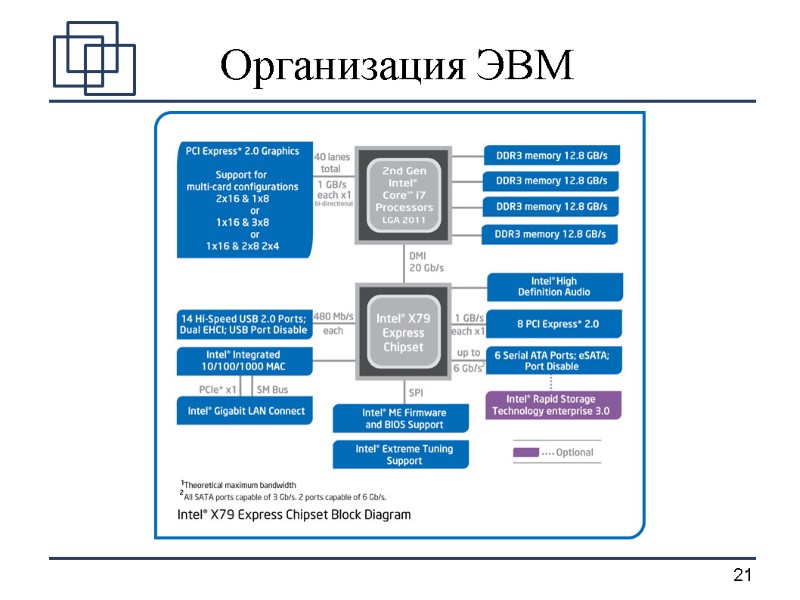

Организация ЭВМ 7 Чипсет Чипсет (от «chip set» – набор микросхем) – набор контроллеров ядра ЭВМ (память, взаимодействие с процессором), системной шины, внешних интерфейсов, физически реализуемый обычно в виде набора микросхем, обычно – в виде двух микросхем, или даже одной микросхемы СБИС. На базе этого набора строятся системные платы (часто называемые «материнскими»).

Организация ЭВМ 7 Чипсет Чипсет (от «chip set» – набор микросхем) – набор контроллеров ядра ЭВМ (память, взаимодействие с процессором), системной шины, внешних интерфейсов, физически реализуемый обычно в виде набора микросхем, обычно – в виде двух микросхем, или даже одной микросхемы СБИС. На базе этого набора строятся системные платы (часто называемые «материнскими»).

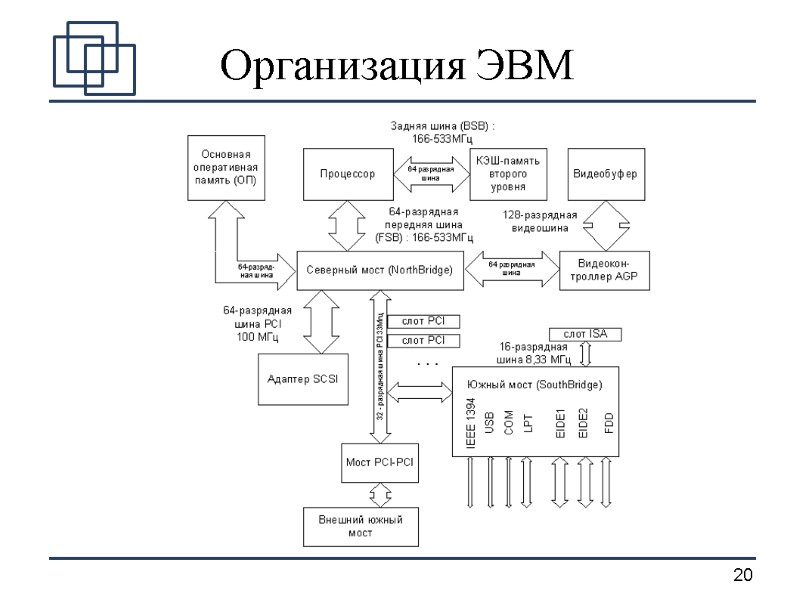

Организация ЭВМ 7.1 Организация чипсетов Чипсеты чаще всего организуются как совокупность северного и южного мостов (Northbridge / SouthBridge), либо – в терминологии Intel – концентраторов памяти (Memory Control Hub – MCH) и ввода-вывода (IO Control Hub - IOCH). Задача северного моста (или MCH) – управление быстродействующим и часто проприетарным ядром. Задача южного моста (или IOCH) – управление внешними стандартными и относительно медленными интерфейсами (к которым сейчас относятся даже PCI и PCI-Е).

Организация ЭВМ 7.1 Организация чипсетов Чипсеты чаще всего организуются как совокупность северного и южного мостов (Northbridge / SouthBridge), либо – в терминологии Intel – концентраторов памяти (Memory Control Hub – MCH) и ввода-вывода (IO Control Hub - IOCH). Задача северного моста (или MCH) – управление быстродействующим и часто проприетарным ядром. Задача южного моста (или IOCH) – управление внешними стандартными и относительно медленными интерфейсами (к которым сейчас относятся даже PCI и PCI-Е).

Организация ЭВМ

Организация ЭВМ

Организация ЭВМ

Организация ЭВМ