Организация ЭВМ и систем Лекция 6 Организация ввода-вывода.

org-evm-6.ppt

- Количество слайдов: 9

Организация ЭВМ и систем Лекция 6 Организация ввода-вывода

Организация ЭВМ и систем Лекция 6 Организация ввода-вывода

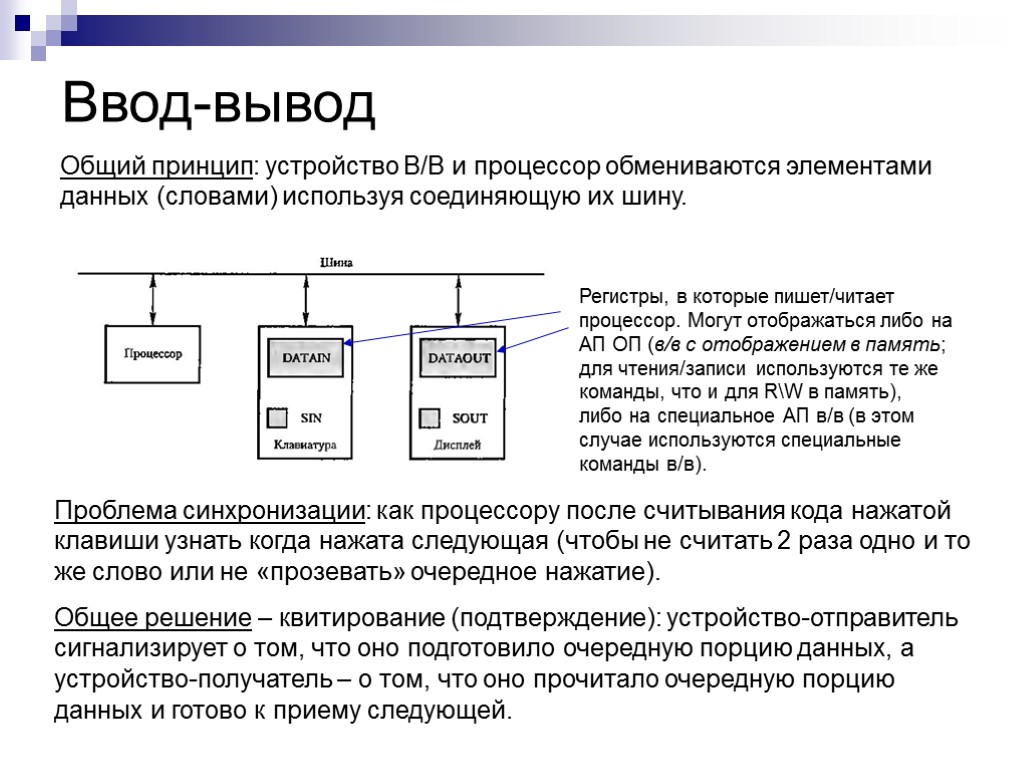

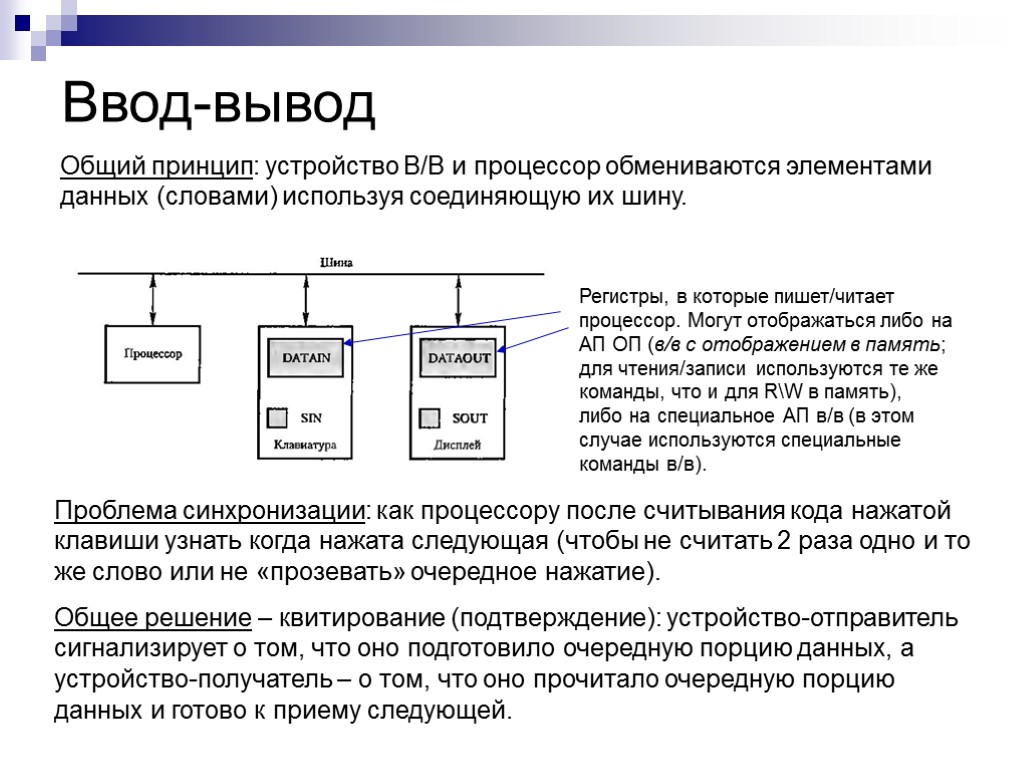

Ввод-вывод Проблема синхронизации: как процессору после считывания кода нажатой клавиши узнать когда нажата следующая (чтобы не считать 2 раза одно и то же слово или не «прозевать» очередное нажатие). Общее решение – квитирование (подтверждение): устройство-отправитель сигнализирует о том, что оно подготовило очередную порцию данных, а устройство-получатель – о том, что оно прочитало очередную порцию данных и готово к приему следующей. Общий принцип: устройство В/В и процессор обмениваются элементами данных (словами) используя соединяющую их шину. Регистры, в которые пишет/читает процессор. Могут отображаться либо на АП ОП (в/в с отображением в память; для чтения/записи используются те же команды, что и для RW в память), либо на специальное АП в/в (в этом случае используются специальные команды в/в).

Ввод-вывод Проблема синхронизации: как процессору после считывания кода нажатой клавиши узнать когда нажата следующая (чтобы не считать 2 раза одно и то же слово или не «прозевать» очередное нажатие). Общее решение – квитирование (подтверждение): устройство-отправитель сигнализирует о том, что оно подготовило очередную порцию данных, а устройство-получатель – о том, что оно прочитало очередную порцию данных и готово к приему следующей. Общий принцип: устройство В/В и процессор обмениваются элементами данных (словами) используя соединяющую их шину. Регистры, в которые пишет/читает процессор. Могут отображаться либо на АП ОП (в/в с отображением в память; для чтения/записи используются те же команды, что и для RW в память), либо на специальное АП в/в (в этом случае используются специальные команды в/в).

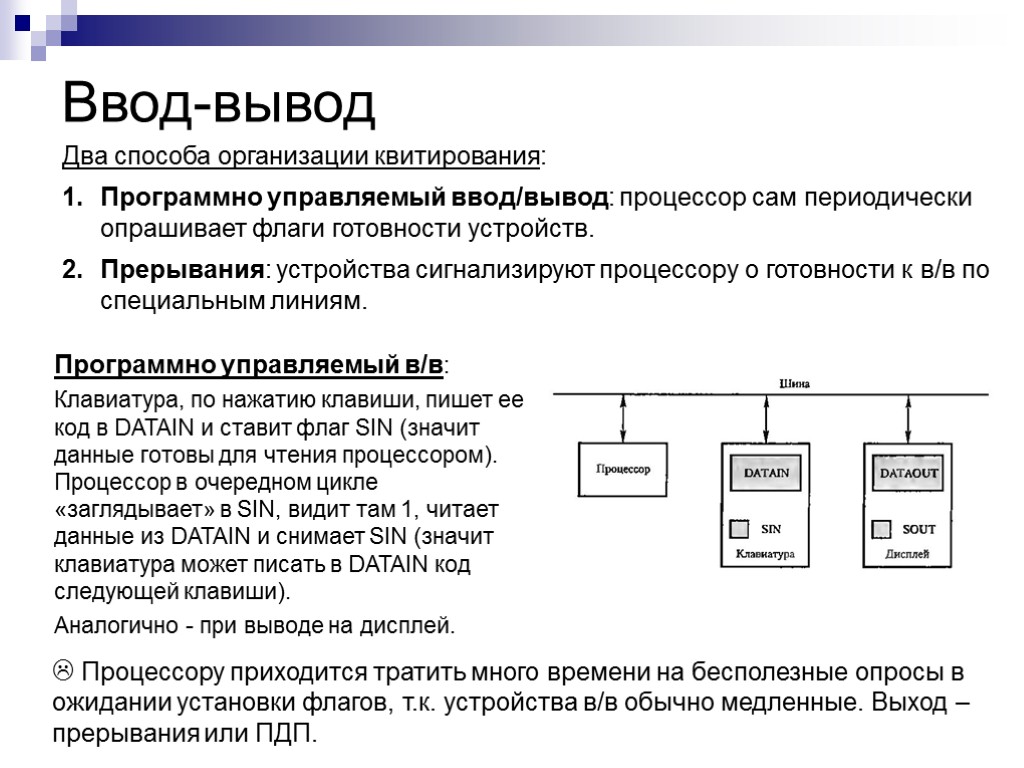

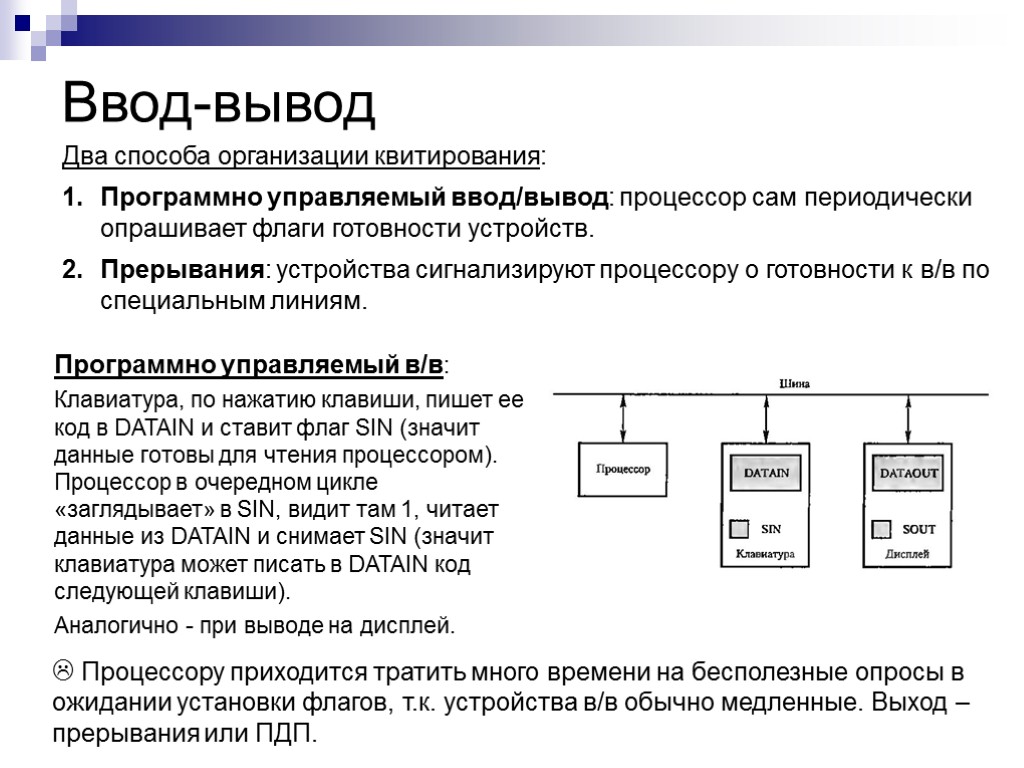

Ввод-вывод Два способа организации квитирования: Программно управляемый ввод/вывод: процессор сам периодически опрашивает флаги готовности устройств. Прерывания: устройства сигнализируют процессору о готовности к в/в по специальным линиям. Программно управляемый в/в: Клавиатура, по нажатию клавиши, пишет ее код в DATAIN и ставит флаг SIN (значит данные готовы для чтения процессором). Процессор в очередном цикле «заглядывает» в SIN, видит там 1, читает данные из DATAIN и снимает SIN (значит клавиатура может писать в DATAIN код следующей клавиши). Аналогично - при выводе на дисплей. Процессору приходится тратить много времени на бесполезные опросы в ожидании установки флагов, т.к. устройства в/в обычно медленные. Выход – прерывания или ПДП.

Ввод-вывод Два способа организации квитирования: Программно управляемый ввод/вывод: процессор сам периодически опрашивает флаги готовности устройств. Прерывания: устройства сигнализируют процессору о готовности к в/в по специальным линиям. Программно управляемый в/в: Клавиатура, по нажатию клавиши, пишет ее код в DATAIN и ставит флаг SIN (значит данные готовы для чтения процессором). Процессор в очередном цикле «заглядывает» в SIN, видит там 1, читает данные из DATAIN и снимает SIN (значит клавиатура может писать в DATAIN код следующей клавиши). Аналогично - при выводе на дисплей. Процессору приходится тратить много времени на бесполезные опросы в ожидании установки флагов, т.к. устройства в/в обычно медленные. Выход – прерывания или ПДП.

Ввод-вывод. Прерывания. Вследствие асинхронности запросов прерывания возникает специфическая проблема: запрос может поступить в любой момент, в т.ч. когда процессор занят выполнением какой-либо программы. Решение: При поступлении запроса прерывания процессор приостанавливает выполнение текущей программы, сохраняет ее состояние и переходит к выполнению программы-обработчика данного запроса. По окончании обработки прерывания восстанавливается процесс выполнения прерванной программы. Устройства сигнализируют процессору о готовности к в/в посылая ему сигнал (запрос прерывания) по специальным линиям (линиям запроса прерывания).

Ввод-вывод. Прерывания. Вследствие асинхронности запросов прерывания возникает специфическая проблема: запрос может поступить в любой момент, в т.ч. когда процессор занят выполнением какой-либо программы. Решение: При поступлении запроса прерывания процессор приостанавливает выполнение текущей программы, сохраняет ее состояние и переходит к выполнению программы-обработчика данного запроса. По окончании обработки прерывания восстанавливается процесс выполнения прерванной программы. Устройства сигнализируют процессору о готовности к в/в посылая ему сигнал (запрос прерывания) по специальным линиям (линиям запроса прерывания).

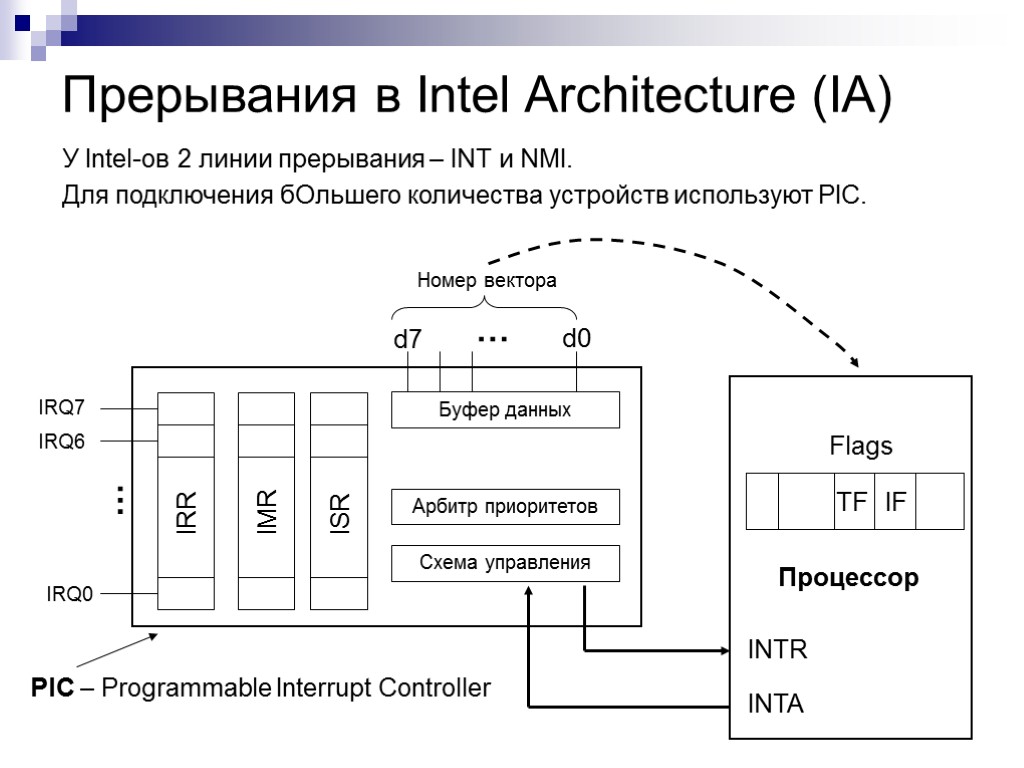

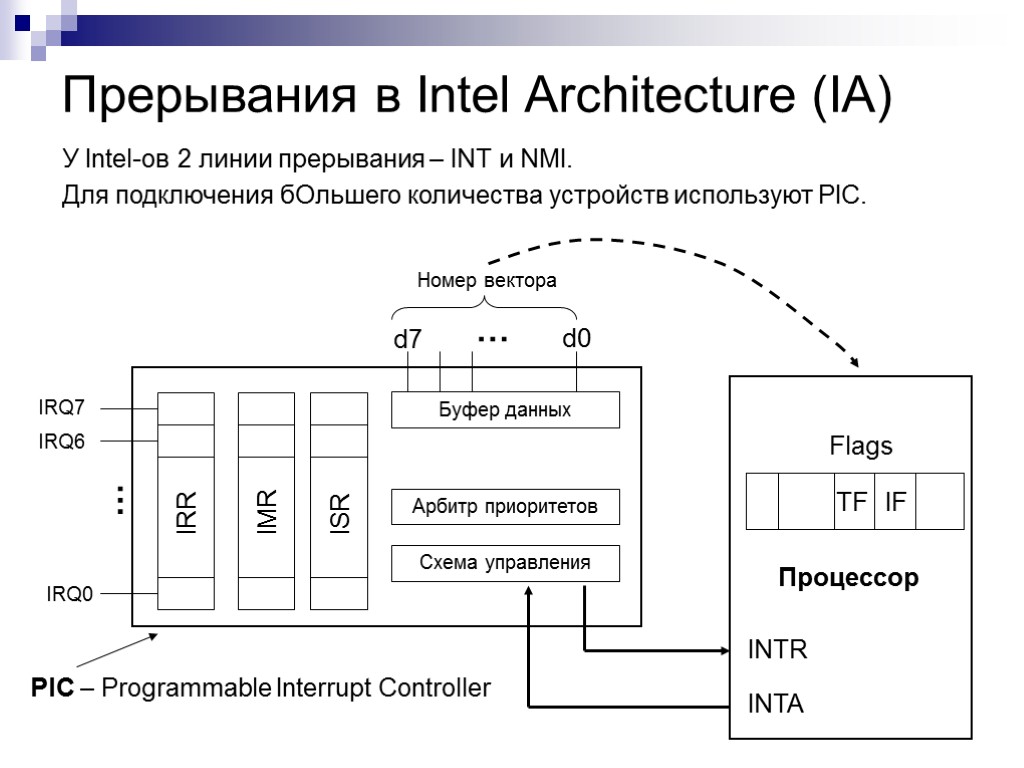

Прерывания в Intel Architecture (IA) У Intel-ов 2 линии прерывания – INT и NMI. Для подключения бОльшего количества устройств используют PIC. Буфер данных Арбитр приоритетов Схема управления IRQ7 IRQ6 IRQ0 … PIC – Programmable Interrupt Controller d0 d7 … Номер вектора

Прерывания в Intel Architecture (IA) У Intel-ов 2 линии прерывания – INT и NMI. Для подключения бОльшего количества устройств используют PIC. Буфер данных Арбитр приоритетов Схема управления IRQ7 IRQ6 IRQ0 … PIC – Programmable Interrupt Controller d0 d7 … Номер вектора

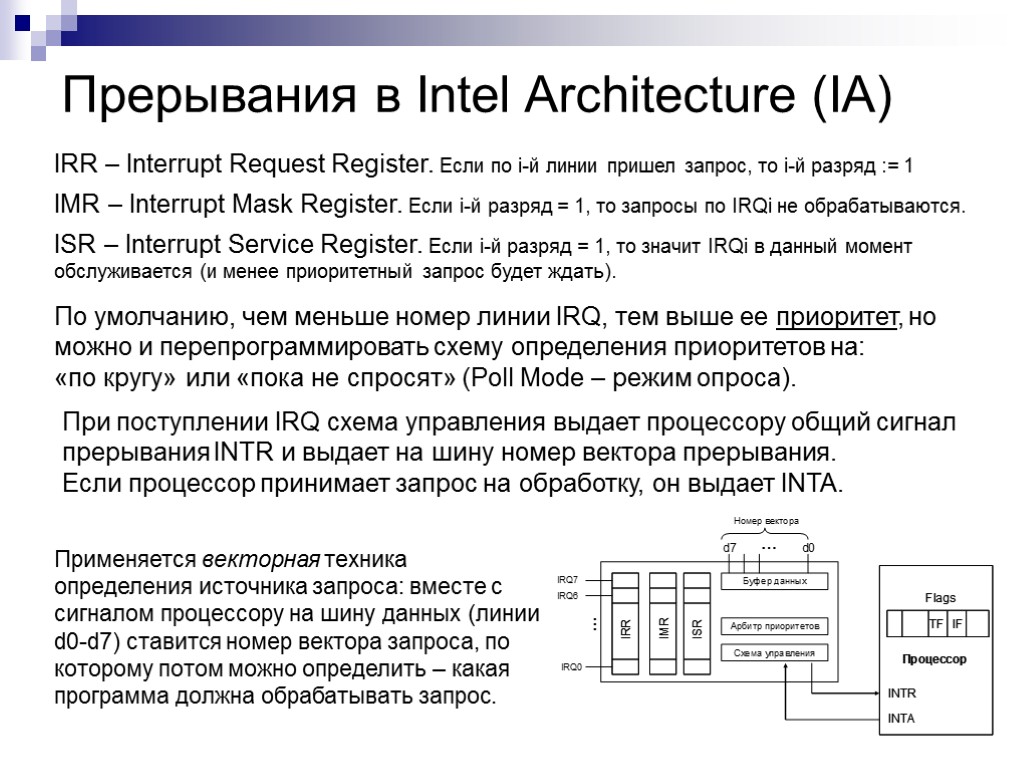

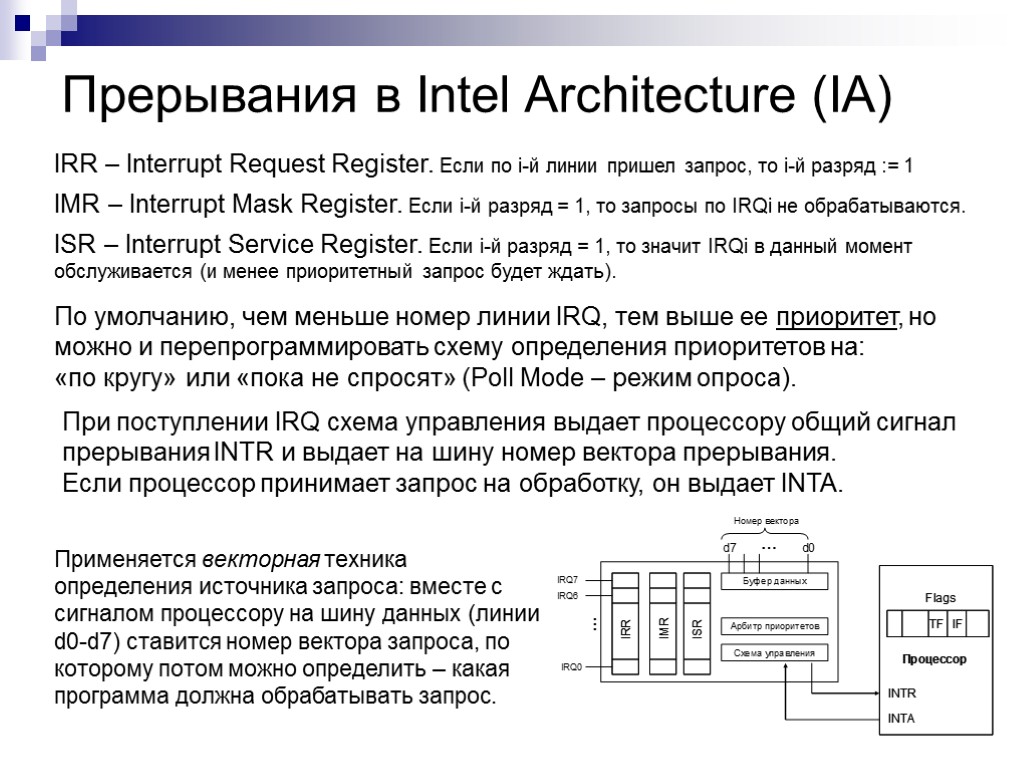

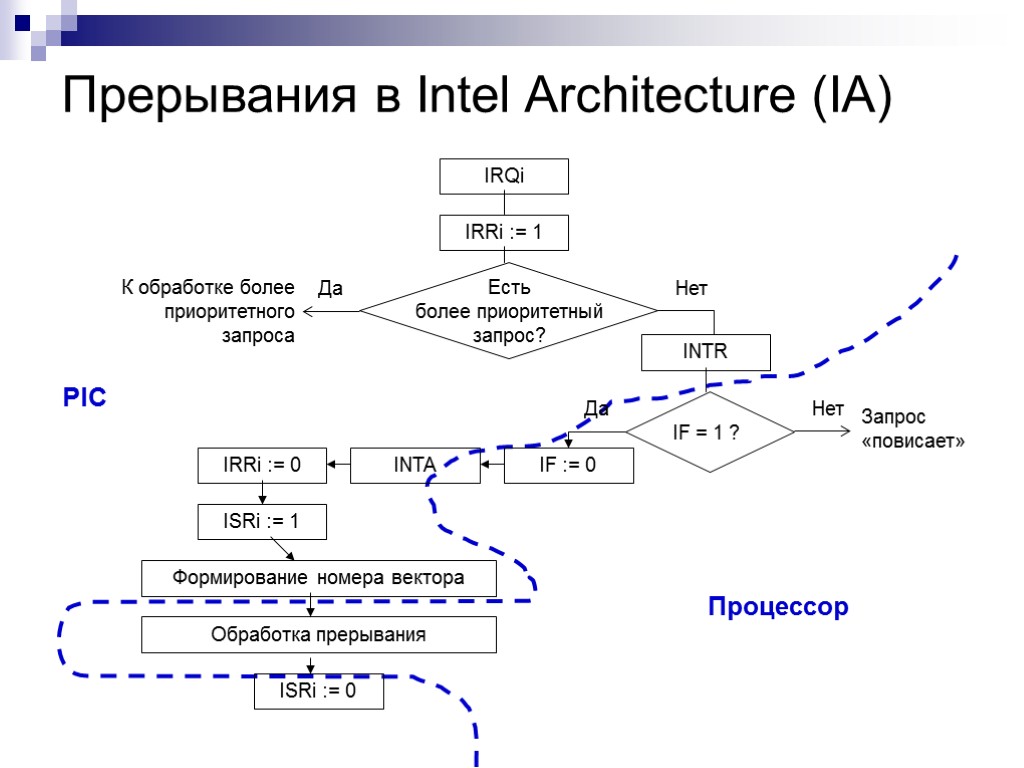

Прерывания в Intel Architecture (IA) IRR – Interrupt Request Register. Если по i-й линии пришел запрос, то i-й разряд := 1 IMR – Interrupt Mask Register. Если i-й разряд = 1, то запросы по IRQi не обрабатываются. ISR – Interrupt Service Register. Если i-й разряд = 1, то значит IRQi в данный момент обслуживается (и менее приоритетный запрос будет ждать). Применяется векторная техника определения источника запроса: вместе с сигналом процессору на шину данных (линии d0-d7) ставится номер вектора запроса, по которому потом можно определить – какая программа должна обрабатывать запрос. По умолчанию, чем меньше номер линии IRQ, тем выше ее приоритет, но можно и перепрограммировать схему определения приоритетов на: «по кругу» или «пока не спросят» (Poll Mode – режим опроса). При поступлении IRQ cхема управления выдает процессору общий сигнал прерывания INTR и выдает на шину номер вектора прерывания. Если процессор принимает запрос на обработку, он выдает INTA.

Прерывания в Intel Architecture (IA) IRR – Interrupt Request Register. Если по i-й линии пришел запрос, то i-й разряд := 1 IMR – Interrupt Mask Register. Если i-й разряд = 1, то запросы по IRQi не обрабатываются. ISR – Interrupt Service Register. Если i-й разряд = 1, то значит IRQi в данный момент обслуживается (и менее приоритетный запрос будет ждать). Применяется векторная техника определения источника запроса: вместе с сигналом процессору на шину данных (линии d0-d7) ставится номер вектора запроса, по которому потом можно определить – какая программа должна обрабатывать запрос. По умолчанию, чем меньше номер линии IRQ, тем выше ее приоритет, но можно и перепрограммировать схему определения приоритетов на: «по кругу» или «пока не спросят» (Poll Mode – режим опроса). При поступлении IRQ cхема управления выдает процессору общий сигнал прерывания INTR и выдает на шину номер вектора прерывания. Если процессор принимает запрос на обработку, он выдает INTA.

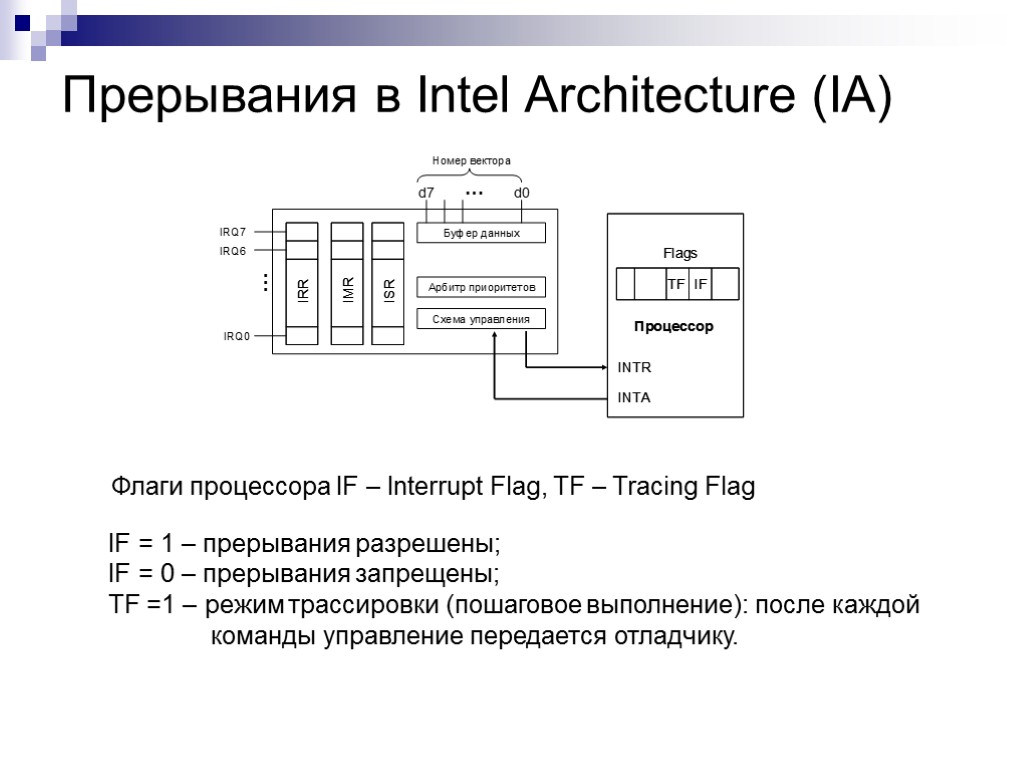

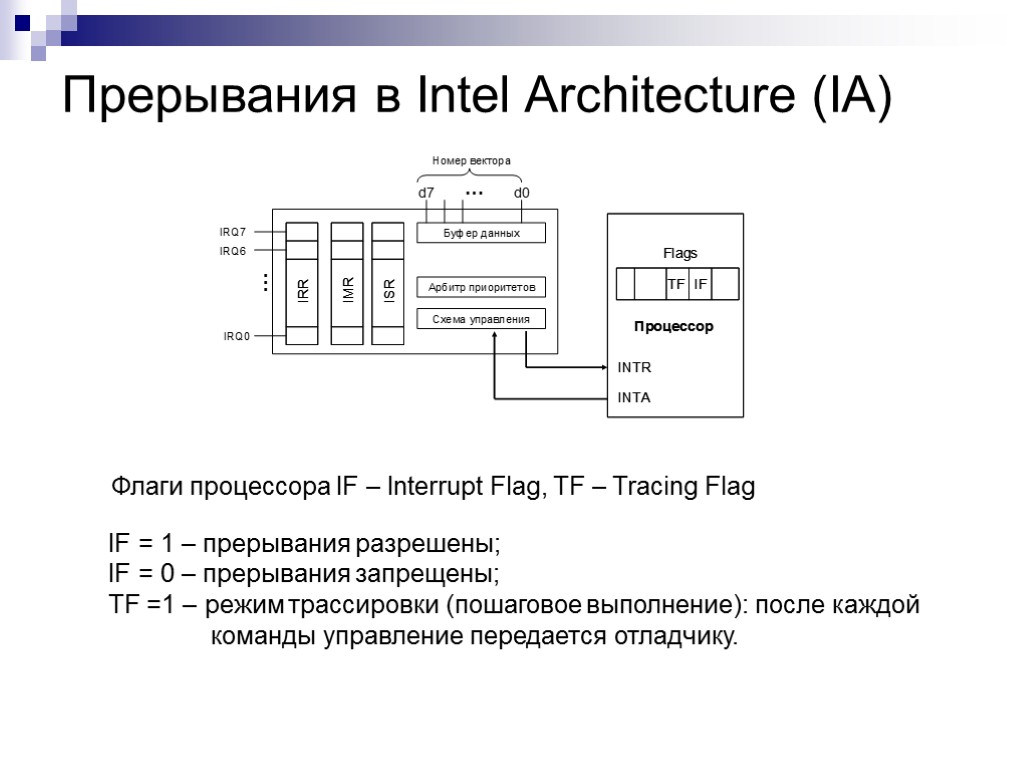

Прерывания в Intel Architecture (IA) IF = 1 – прерывания разрешены; IF = 0 – прерывания запрещены; TF =1 – режим трассировки (пошаговое выполнение): после каждой команды управление передается отладчику. Флаги процессора IF – Interrupt Flag, TF – Tracing Flag

Прерывания в Intel Architecture (IA) IF = 1 – прерывания разрешены; IF = 0 – прерывания запрещены; TF =1 – режим трассировки (пошаговое выполнение): после каждой команды управление передается отладчику. Флаги процессора IF – Interrupt Flag, TF – Tracing Flag

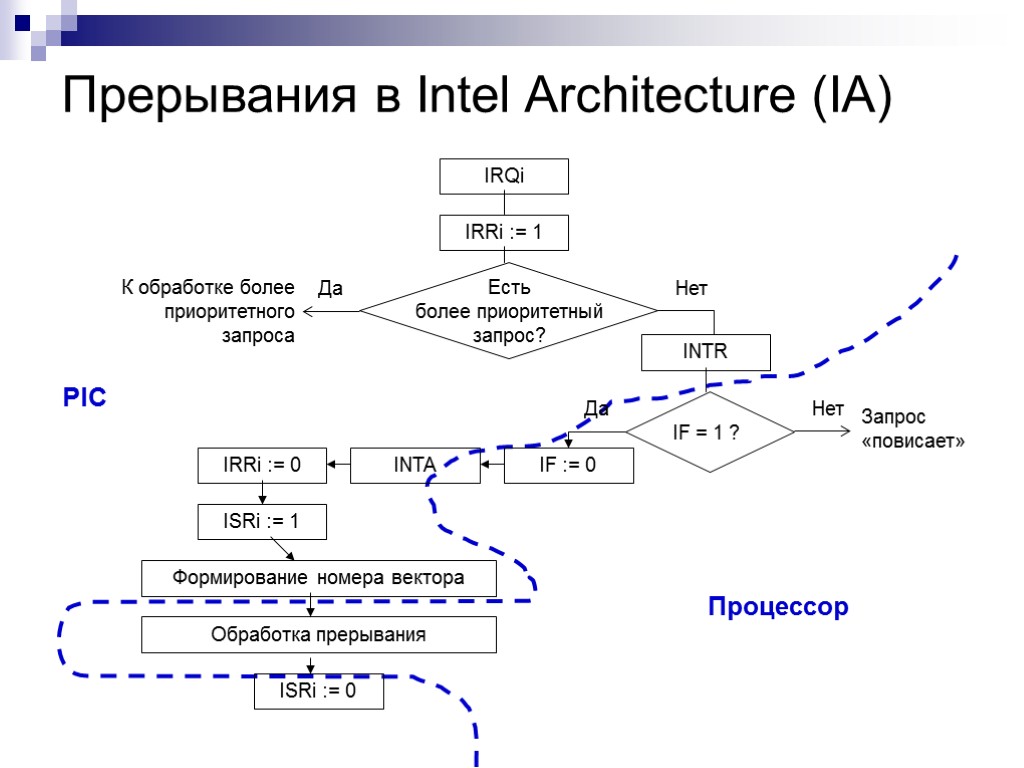

Прерывания в Intel Architecture (IA) PIC Процессор

Прерывания в Intel Architecture (IA) PIC Процессор

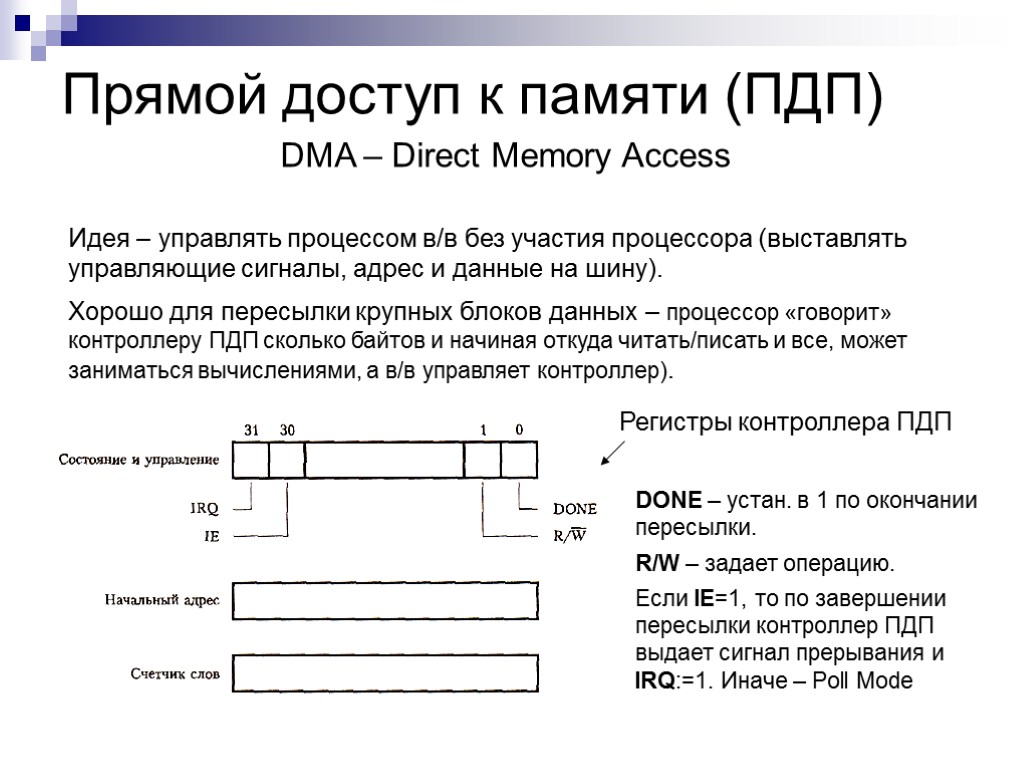

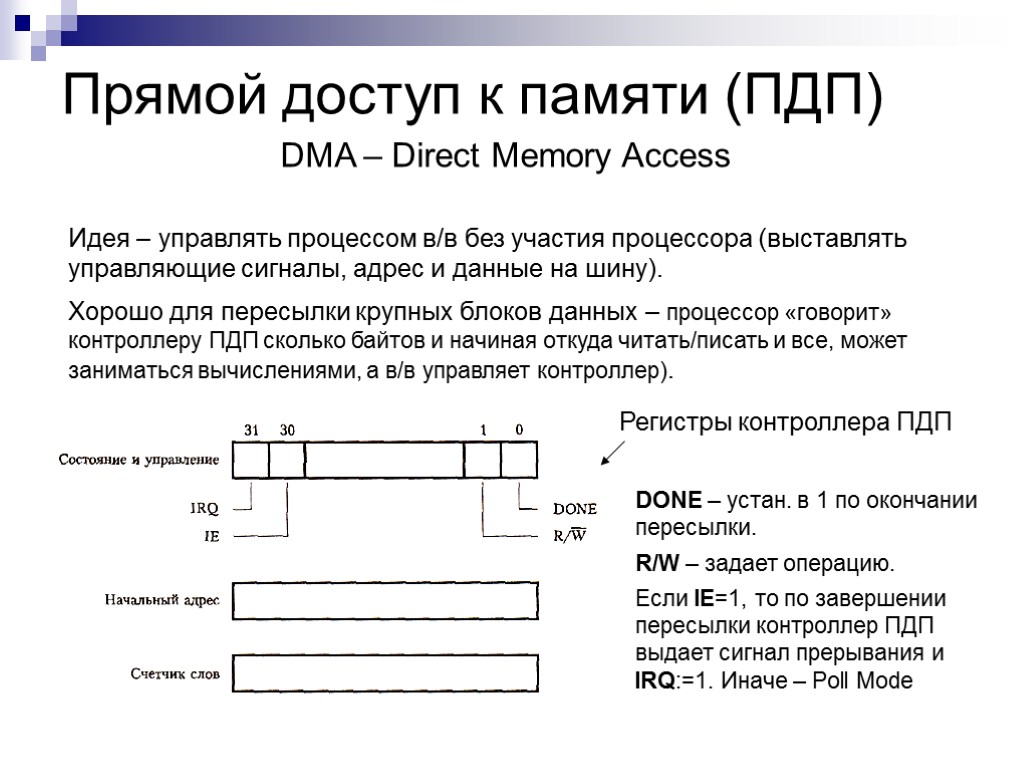

Прямой доступ к памяти (ПДП) DMA – Direct Memory Access Идея – управлять процессом в/в без участия процессора (выставлять управляющие сигналы, адрес и данные на шину). Хорошо для пересылки крупных блоков данных – процессор «говорит» контроллеру ПДП сколько байтов и начиная откуда читать/писать и все, может заниматься вычислениями, а в/в управляет контроллер). DONE – устан. в 1 по окончании пересылки. R/W – задает операцию. Если IE=1, то по завершении пересылки контроллер ПДП выдает сигнал прерывания и IRQ:=1. Иначе – Poll Mode Регистры контроллера ПДП

Прямой доступ к памяти (ПДП) DMA – Direct Memory Access Идея – управлять процессом в/в без участия процессора (выставлять управляющие сигналы, адрес и данные на шину). Хорошо для пересылки крупных блоков данных – процессор «говорит» контроллеру ПДП сколько байтов и начиная откуда читать/писать и все, может заниматься вычислениями, а в/в управляет контроллер). DONE – устан. в 1 по окончании пересылки. R/W – задает операцию. Если IE=1, то по завершении пересылки контроллер ПДП выдает сигнал прерывания и IRQ:=1. Иначе – Poll Mode Регистры контроллера ПДП