ЛК_2.pptx

- Количество слайдов: 19

ЛЕКЦІЯ 2 АРХІТЕКТУРА МІКРОПРОЦЕСОРІВ

ЛЕКЦІЯ 2 АРХІТЕКТУРА МІКРОПРОЦЕСОРІВ

Архітектура мікропроцесорів Архітектура МП містить: 1) структурну схему МП; 2) програмну модель МП (опис функцій регістрів); 3) організацію пам’яті (ємність пам’яті та способи її адресації); 4) опис організації процедур введення-виведення.

Архітектура мікропроцесорів Архітектура МП містить: 1) структурну схему МП; 2) програмну модель МП (опис функцій регістрів); 3) організацію пам’яті (ємність пам’яті та способи її адресації); 4) опис організації процедур введення-виведення.

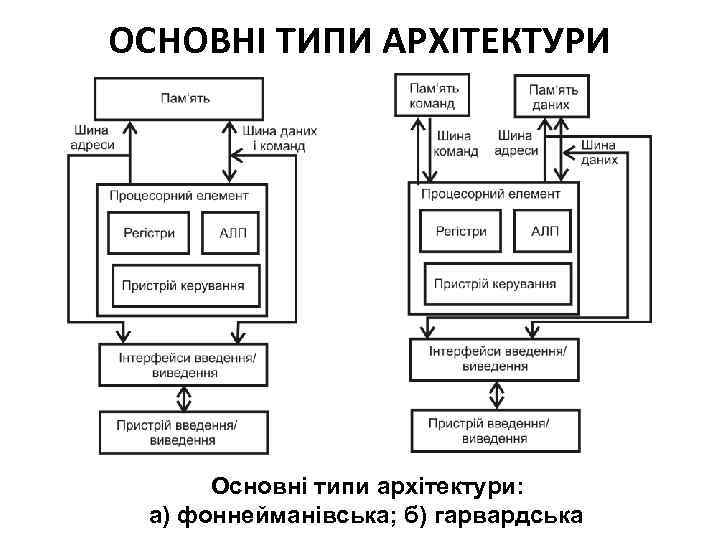

ОСНОВНІ ТИПИ АРХІТЕКТУРИ Основні типи архітектури: а) фоннейманівська; б) гарвардська

ОСНОВНІ ТИПИ АРХІТЕКТУРИ Основні типи архітектури: а) фоннейманівська; б) гарвардська

Структурна схема з процесором фоннейманівської архітектури

Структурна схема з процесором фоннейманівської архітектури

Процесорний елемент містить регістри, арифметико - логічний пристрій (АЛП), пристрій керування і виконує функції обробки даних та керування процесами обміну інформацією.

Процесорний елемент містить регістри, арифметико - логічний пристрій (АЛП), пристрій керування і виконує функції обробки даних та керування процесами обміну інформацією.

Архітектура МП Пам'ять забезпечує зберігання кодів команд програми і даних. Інтерфейси ІВВ призначені для зв'язку з ПВВ (наприклад, з клавіатурою, дисплеєм, друкувальними пристроями, датчиками інформації). Пристрій керування відповідно до кодів команд та зовнішніх сигналів керування і сигналів синхронізації виробляє сигнали керування для всіх блоків структурної схеми МП, а також керує обміном інформацією між МП, пам'яттю і ПВВ.

Архітектура МП Пам'ять забезпечує зберігання кодів команд програми і даних. Інтерфейси ІВВ призначені для зв'язку з ПВВ (наприклад, з клавіатурою, дисплеєм, друкувальними пристроями, датчиками інформації). Пристрій керування відповідно до кодів команд та зовнішніх сигналів керування і сигналів синхронізації виробляє сигнали керування для всіх блоків структурної схеми МП, а також керує обміном інформацією між МП, пам'яттю і ПВВ.

Пристрій керування реалізує наступні функції: 1. Функція початкового встановлення МП (Зовнішній сигнал початкового встановлення процесора RESET). 2. Функція переривань. 3. Функція узгодження швидкодії модулів мікропроцесорної системи.

Пристрій керування реалізує наступні функції: 1. Функція початкового встановлення МП (Зовнішній сигнал початкового встановлення процесора RESET). 2. Функція переривань. 3. Функція узгодження швидкодії модулів мікропроцесорної системи.

Операнд – це об'єкт у вигляді значення даних, вмісту регістрів або вмісту комірки пам'яті, з яким оперує команда, наприклад, у команді додавання операндами є доданки. Регістри призначені для зберігання n - розрядного двійкового числа. Вони являють собою n тригерів зі схемами керування читанням/записом та вибірки. Регістри створюють внутрішню пам'ять МП і використовуються для зберігання проміжних результатів обчислень.

Операнд – це об'єкт у вигляді значення даних, вмісту регістрів або вмісту комірки пам'яті, з яким оперує команда, наприклад, у команді додавання операндами є доданки. Регістри призначені для зберігання n - розрядного двійкового числа. Вони являють собою n тригерів зі схемами керування читанням/записом та вибірки. Регістри створюють внутрішню пам'ять МП і використовуються для зберігання проміжних результатів обчислень.

Акумулятор – це регістр, у якому зберігається один з операндів. Після виконання команди в акумуляторі замість операнда розміщується результат операції. Вказівник команд, або програмний лічильник, призначений для зберігання адреси комірки пам'яті, яка містить код наступної команди. Вказівник стека – це регістр, який зберігає адресу останньої зайнятої комірки стека. Стеком або стековою пам'яттю називається область пам'яті, організованої за принципом "останній прийшов – перший пішов“ (англ. FIFO).

Акумулятор – це регістр, у якому зберігається один з операндів. Після виконання команди в акумуляторі замість операнда розміщується результат операції. Вказівник команд, або програмний лічильник, призначений для зберігання адреси комірки пам'яті, яка містить код наступної команди. Вказівник стека – це регістр, який зберігає адресу останньої зайнятої комірки стека. Стеком або стековою пам'яттю називається область пам'яті, організованої за принципом "останній прийшов – перший пішов“ (англ. FIFO).

Арифметико-логічний пристрій представляє собою комбінаційну схему на основі суматора, який сигналами з виходів пристрою керування налагоджується на виконання певної арифметичної або логічної операції: додавання, віднімання, "ЛОГІЧНЕ І", ЛОГІЧНЕ АБО, ЛОГІЧНЕ НІ, ВИКЛЮЧНЕ АБО, зсуву, порівняння, десяткової корекції. Отже, АЛП виконує арифметичні або логічні операції над операндами, які пересилаються з пам'яті і (або) регістрів МП.

Арифметико-логічний пристрій представляє собою комбінаційну схему на основі суматора, який сигналами з виходів пристрою керування налагоджується на виконання певної арифметичної або логічної операції: додавання, віднімання, "ЛОГІЧНЕ І", ЛОГІЧНЕ АБО, ЛОГІЧНЕ НІ, ВИКЛЮЧНЕ АБО, зсуву, порівняння, десяткової корекції. Отже, АЛП виконує арифметичні або логічні операції над операндами, які пересилаються з пам'яті і (або) регістрів МП.

• Регістр команд зберігає код команди протягом усього часу виконання команди. • Регістр адреси і регістри даних призначені для зберігання адрес і даних, використовуваних під час виконання поточної команди у МП. • Регістр стану або регістр прапорців (ознак) призначений для зберігання інформації про результат операції в АЛП і представляє собою декілька тригерів, які набувають одиничних або нульових значень. Наприклад, прапорець нуля встановлюється в одиницю при нульовому результаті операції.

• Регістр команд зберігає код команди протягом усього часу виконання команди. • Регістр адреси і регістри даних призначені для зберігання адрес і даних, використовуваних під час виконання поточної команди у МП. • Регістр стану або регістр прапорців (ознак) призначений для зберігання інформації про результат операції в АЛП і представляє собою декілька тригерів, які набувають одиничних або нульових значень. Наприклад, прапорець нуля встановлюється в одиницю при нульовому результаті операції.

Типова послідовність роботи МП при виконанні будь - якої команди в ЕОМ Етапи: • вибірка чергової команди і даних, необхідних для її виконання, з оперативної пам'яті ЕОМ; • декодування команди; • власне її виконання; • запис отриманого результату в оперативну пам'ять.

Типова послідовність роботи МП при виконанні будь - якої команди в ЕОМ Етапи: • вибірка чергової команди і даних, необхідних для її виконання, з оперативної пам'яті ЕОМ; • декодування команди; • власне її виконання; • запис отриманого результату в оперативну пам'ять.

Етапи розвитку архітектури універсальних мікропроцесорів 1. МП Intel , 1971 рік - І-4004 -Тед Хофф (англ. Ted Hoff), Стен Мейзор (англ. Stan Mazor) і Федеріко Феджин (англ. Federico Faggin). 2. i 8008 - 1972 рік. 3. 8080 - 1974 рік. Гарі Килделл (англ. Gary Kildall) з Digital Research створив для процесора 8080 операційну систему СР/М. 4. i 8086 - 1978 рік. 16 -розрядний МП. 5. і 80286 - 1980 рік. 16 -розрядний МП. Реалізовано 2 режими роботи: захищений і реальний. 6. і 386 -1985 рік, архітектура ІА-32 (Intel Architecture 32).

Етапи розвитку архітектури універсальних мікропроцесорів 1. МП Intel , 1971 рік - І-4004 -Тед Хофф (англ. Ted Hoff), Стен Мейзор (англ. Stan Mazor) і Федеріко Феджин (англ. Federico Faggin). 2. i 8008 - 1972 рік. 3. 8080 - 1974 рік. Гарі Килделл (англ. Gary Kildall) з Digital Research створив для процесора 8080 операційну систему СР/М. 4. i 8086 - 1978 рік. 16 -розрядний МП. 5. і 80286 - 1980 рік. 16 -розрядний МП. Реалізовано 2 режими роботи: захищений і реальний. 6. і 386 -1985 рік, архітектура ІА-32 (Intel Architecture 32).

Етапи розвитку архітектури універсальних мікропроцесорів 10. Pentium III - 1999 рік. З’явився спеціальний блок SSE (англ. Streaming SIMD Extensions, потокове SIMD – розширення процесора). розміщення на кристалі кеш-пам’яті другого рівня (починаючи з ядра Coppermine), працюючого на частоті ядра. 11. Pentium 4 -2000 рік. більше збільшення глибини конвеєра – до 31 стадії, що дозволило значно наростити частоту процесора. Кількість конвеєрів зросла до 9. Підтримки інструкцій MMX (англ. Multimedia Extensions – мультимедійні розширення), які виконують характерні для процесів кодування/декодування потокових аудіо/відео даних дії за одну машину інструкцію) i SSE, що стали традиційними, в Pentium 4 додали ще 144 команди SSE, а потім SSE 3, які орієнтовані в першу чергу на роботу з потоковими даними. 12. Itanium-2001 рік. 64 -розрядна архітектура.

Етапи розвитку архітектури універсальних мікропроцесорів 10. Pentium III - 1999 рік. З’явився спеціальний блок SSE (англ. Streaming SIMD Extensions, потокове SIMD – розширення процесора). розміщення на кристалі кеш-пам’яті другого рівня (починаючи з ядра Coppermine), працюючого на частоті ядра. 11. Pentium 4 -2000 рік. більше збільшення глибини конвеєра – до 31 стадії, що дозволило значно наростити частоту процесора. Кількість конвеєрів зросла до 9. Підтримки інструкцій MMX (англ. Multimedia Extensions – мультимедійні розширення), які виконують характерні для процесів кодування/декодування потокових аудіо/відео даних дії за одну машину інструкцію) i SSE, що стали традиційними, в Pentium 4 додали ще 144 команди SSE, а потім SSE 3, які орієнтовані в першу чергу на роботу з потоковими даними. 12. Itanium-2001 рік. 64 -розрядна архітектура.

Основні характеристики універсальних мікропроцесорів - розрядність МП; - розрядність шини даних МП; - розрядність шини адреси (ША); - розрядність арифметико-логічного пристрою (АЛП); - види і формати даних, які обробляються; - система команд, режими адресації операндів.

Основні характеристики універсальних мікропроцесорів - розрядність МП; - розрядність шини даних МП; - розрядність шини адреси (ША); - розрядність арифметико-логічного пристрою (АЛП); - види і формати даних, які обробляються; - система команд, режими адресації операндів.

- ємність оперативної пам’яті, яка прямо адресується; - частота зовнішньої синхронізації. - швидкодія (продуктивність). Швидкість виконання цілочисленних операцій над числами з фіксованою комою виміряється в MІPS (англ. Мega Instruction Per Second – "мільйон операцій з фіксованою комою за секунду"). Швидкість виконання операцій із плаваючою комою – у MFLOPS (англ. Мega Floating Point Operations Per Second – "мільйон операцій з плаваючою комою за секунду").

- ємність оперативної пам’яті, яка прямо адресується; - частота зовнішньої синхронізації. - швидкодія (продуктивність). Швидкість виконання цілочисленних операцій над числами з фіксованою комою виміряється в MІPS (англ. Мega Instruction Per Second – "мільйон операцій з фіксованою комою за секунду"). Швидкість виконання операцій із плаваючою комою – у MFLOPS (англ. Мega Floating Point Operations Per Second – "мільйон операцій з плаваючою комою за секунду").

Типова структура мікропроцесорної системи Три принципи побудови МПС систем: 1. Принцип магістральності. 2. Принцип модульності. 3. Принцип мікропрограмного керування.

Типова структура мікропроцесорної системи Три принципи побудови МПС систем: 1. Принцип магістральності. 2. Принцип модульності. 3. Принцип мікропрограмного керування.

Типова структура мікропроцесорної системи

Типова структура мікропроцесорної системи

Типи магістралей а б а) з немультиплексованими шинами адреси й даних; б) з мультиплексованими шинами адреси й даних

Типи магістралей а б а) з немультиплексованими шинами адреси й даних; б) з мультиплексованими шинами адреси й даних