Конвейер.ppt

- Количество слайдов: 25

КОНВЕЙЕРНАЯ АРХИТЕКТУРА ПРОЦЕССОРА

КОНВЕЙЕРНАЯ АРХИТЕКТУРА ПРОЦЕССОРА

КОНВЕЙЕР ФОРДА

КОНВЕЙЕР ФОРДА

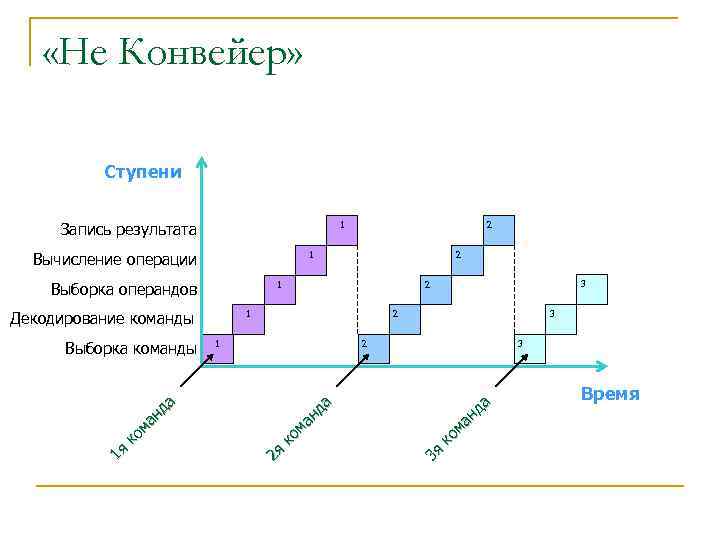

«Не Конвейер» Ступени Запись результата 1 Вычисление операции 1 1 1 3 2 ко ма нд а 1 2 я ко ма нд а 3 2 ко ма нд а Декодирование команды 1 я 2 3 я Выборка операндов Выборка команды 2 Время

«Не Конвейер» Ступени Запись результата 1 Вычисление операции 1 1 1 3 2 ко ма нд а 1 2 я ко ма нд а 3 2 ко ма нд а Декодирование команды 1 я 2 3 я Выборка операндов Выборка команды 2 Время

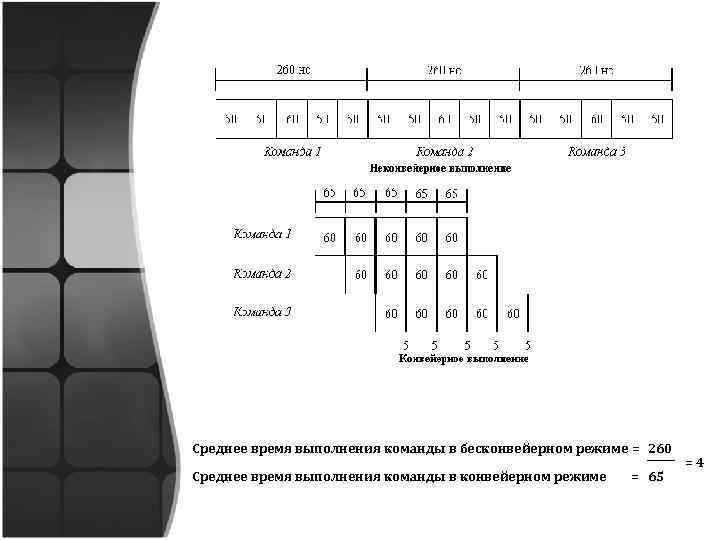

Среднее время выполнения команды в бесконвейерном режиме = 260 Среднее время выполнения команды в конвейерном режиме = 65 =4

Среднее время выполнения команды в бесконвейерном режиме = 260 Среднее время выполнения команды в конвейерном режиме = 65 =4

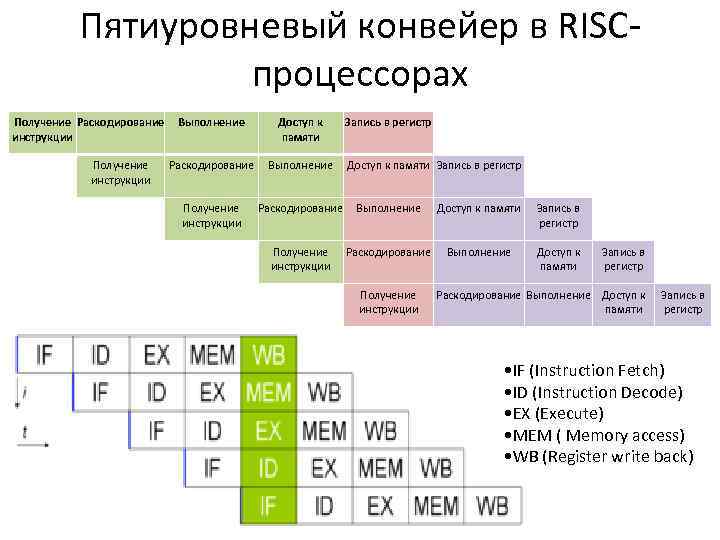

Пятиуровневый конвейер в RISCпроцессорах Получение Раскодирование инструкции Получение инструкции Выполнение Доступ к памяти Запись в регистр Раскодирование Выполнение Получение инструкции Раскодирование Выполнение Доступ к памяти Запись в регистр Получение инструкции Запись в регистр Раскодирование Выполнение Доступ к памяти Запись в регистр • IF (Instruction Fetch) • ID (Instruction Decode) • EX (Execute) • MEM ( Memory access) • WB (Register write back)

Пятиуровневый конвейер в RISCпроцессорах Получение Раскодирование инструкции Получение инструкции Выполнение Доступ к памяти Запись в регистр Раскодирование Выполнение Получение инструкции Раскодирование Выполнение Доступ к памяти Запись в регистр Получение инструкции Запись в регистр Раскодирование Выполнение Доступ к памяти Запись в регистр • IF (Instruction Fetch) • ID (Instruction Decode) • EX (Execute) • MEM ( Memory access) • WB (Register write back)

Конвейер команд Ступени Запись результата 1 2 3 4 5 6 3 4 5 6 Вычисление операции 1 Выборка операндов 1 Декодирование команды 1 1 2 ко 2 я ман ко да 3 я ман ко да ма нд а Выборка команды 1 я Все ступени конвейера активны Латентность конвейера 8 8 7 7 7 6 8 8 8 9 9 9 Время

Конвейер команд Ступени Запись результата 1 2 3 4 5 6 3 4 5 6 Вычисление операции 1 Выборка операндов 1 Декодирование команды 1 1 2 ко 2 я ман ко да 3 я ман ко да ма нд а Выборка команды 1 я Все ступени конвейера активны Латентность конвейера 8 8 7 7 7 6 8 8 8 9 9 9 Время

Первопроходцы ILLIAC II IBM Stretch

Первопроходцы ILLIAC II IBM Stretch

MIPS-I • • получение и декодирование инструкции (Fetch), адресация и выборка операнда из ОЗУ (Memory access), выполнение арифметических операций (Arithmetic Operation), сохранение результата операции (Store).

MIPS-I • • получение и декодирование инструкции (Fetch), адресация и выборка операнда из ОЗУ (Memory access), выполнение арифметических операций (Arithmetic Operation), сохранение результата операции (Store).

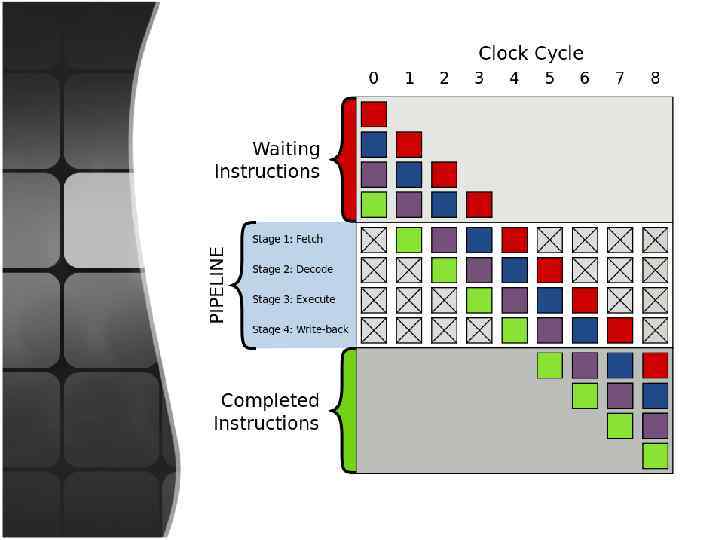

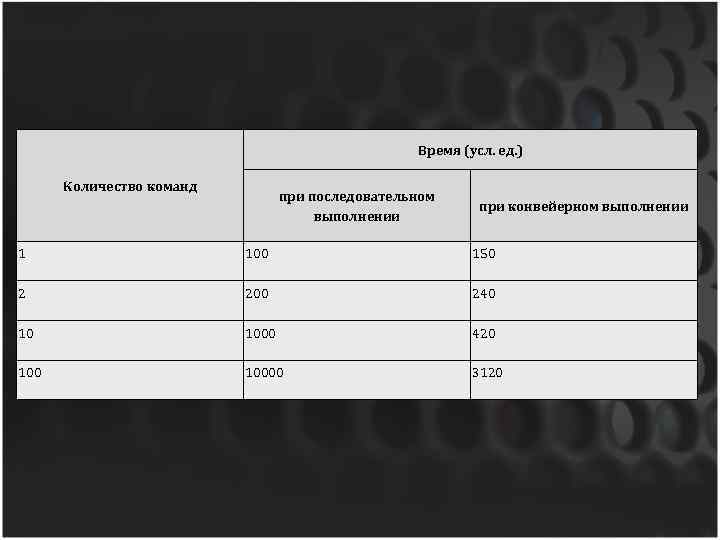

Время (усл. ед. ) Количество команд при последовательном выполнении при конвейерном выполнении 1 100 150 2 200 240 10 1000 420 10000 3120

Время (усл. ед. ) Количество команд при последовательном выполнении при конвейерном выполнении 1 100 150 2 200 240 10 1000 420 10000 3120

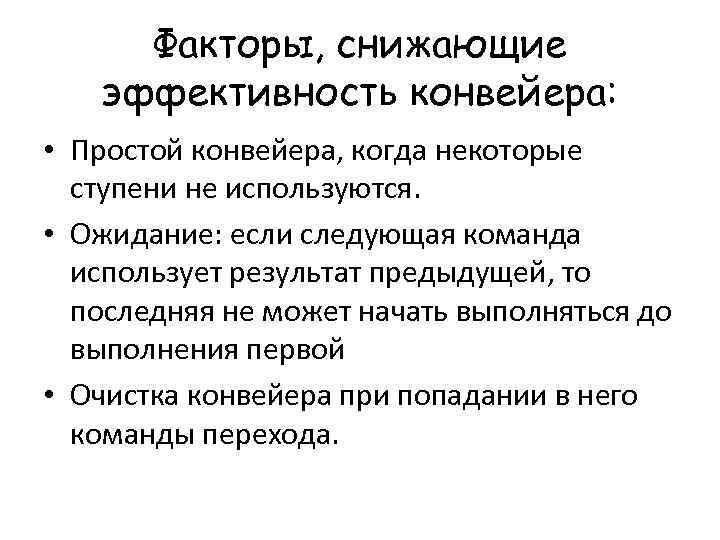

Факторы, снижающие эффективность конвейера: • Простой конвейера, когда некоторые ступени не используются. • Ожидание: если следующая команда использует результат предыдущей, то последняя не может начать выполняться до выполнения первой • Очистка конвейера при попадании в него команды перехода.

Факторы, снижающие эффективность конвейера: • Простой конвейера, когда некоторые ступени не используются. • Ожидание: если следующая команда использует результат предыдущей, то последняя не может начать выполняться до выполнения первой • Очистка конвейера при попадании в него команды перехода.

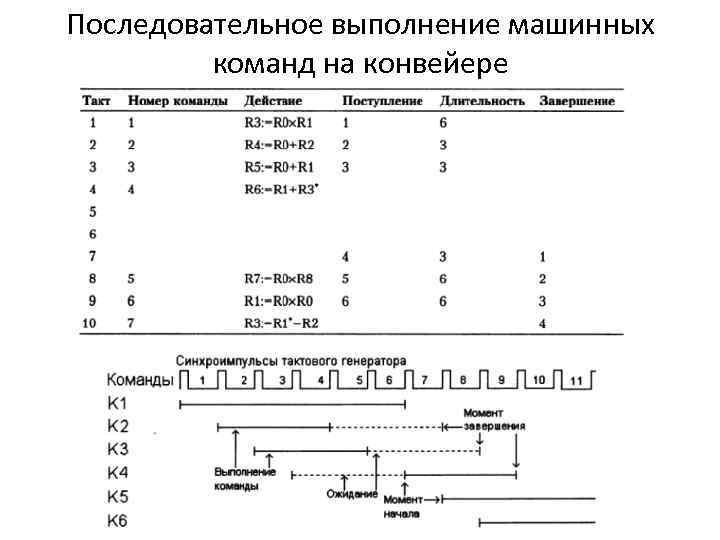

Последовательное выполнение машинных команд на конвейере

Последовательное выполнение машинных команд на конвейере

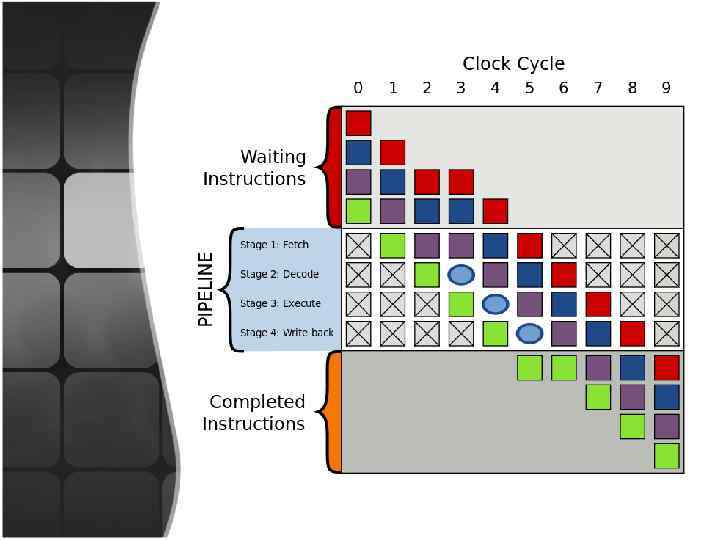

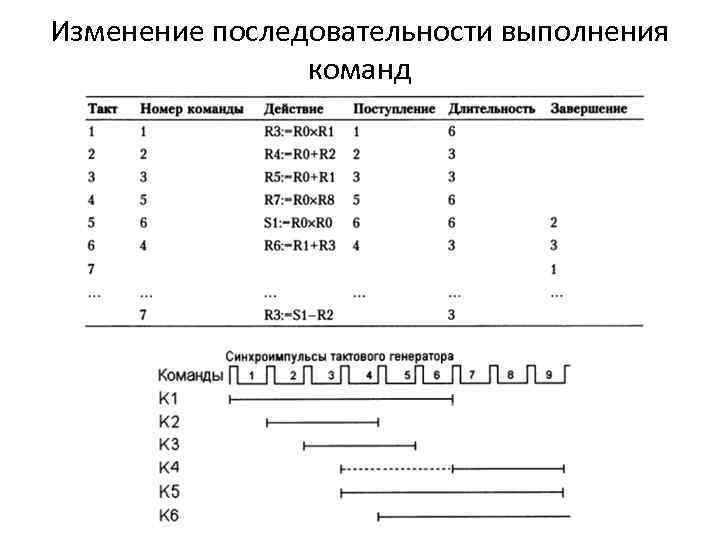

Изменение последовательности выполнения команд

Изменение последовательности выполнения команд

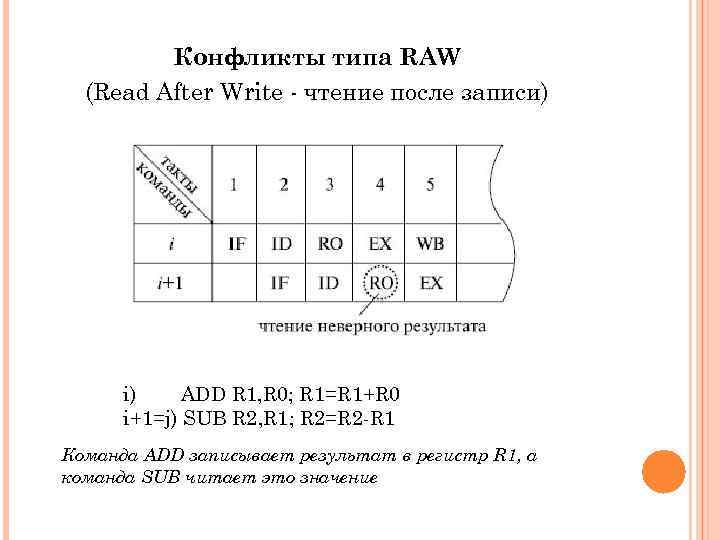

Конфликты типа RAW (Read After Write - чтение после записи) i) ADD R 1, R 0; R 1=R 1+R 0 i+1=j) SUB R 2, R 1; R 2=R 2 -R 1 Команда ADD записывает результат в регистр R 1, а команда SUB читает это значение

Конфликты типа RAW (Read After Write - чтение после записи) i) ADD R 1, R 0; R 1=R 1+R 0 i+1=j) SUB R 2, R 1; R 2=R 2 -R 1 Команда ADD записывает результат в регистр R 1, а команда SUB читает это значение

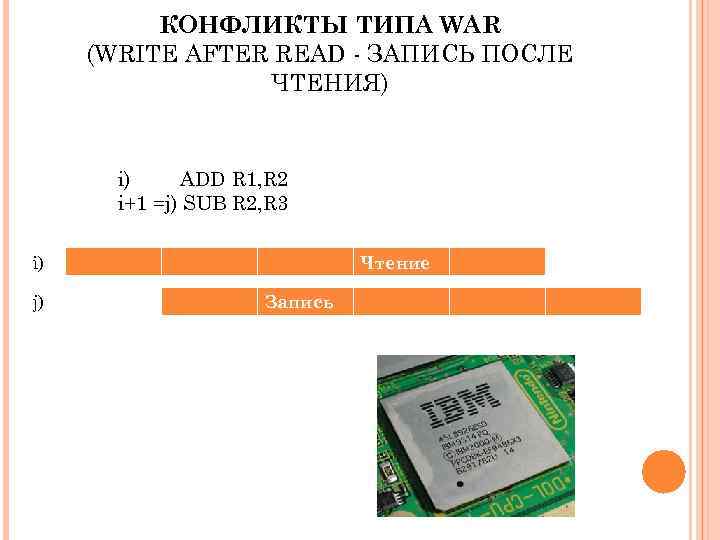

КОНФЛИКТЫ ТИПА WAR (WRITE AFTER READ - ЗАПИСЬ ПОСЛЕ ЧТЕНИЯ) i) ADD R 1, R 2 i+1 =j) SUB R 2, R 3 i) j) Чтение Запись

КОНФЛИКТЫ ТИПА WAR (WRITE AFTER READ - ЗАПИСЬ ПОСЛЕ ЧТЕНИЯ) i) ADD R 1, R 2 i+1 =j) SUB R 2, R 3 i) j) Чтение Запись

КОНФЛИКТЫ ТИПА WAW (WRITE AFTER WRITE - ЗАПИСЬ ПОСЛЕ ЗАПИСИ) i) ADD R 1, R 0; R 1=R 1+R 0. . . j) SUB R 1, R 2; R 1=R 1 -R 2 i) j) Запись

КОНФЛИКТЫ ТИПА WAW (WRITE AFTER WRITE - ЗАПИСЬ ПОСЛЕ ЗАПИСИ) i) ADD R 1, R 0; R 1=R 1+R 0. . . j) SUB R 1, R 2; R 1=R 1 -R 2 i) j) Запись

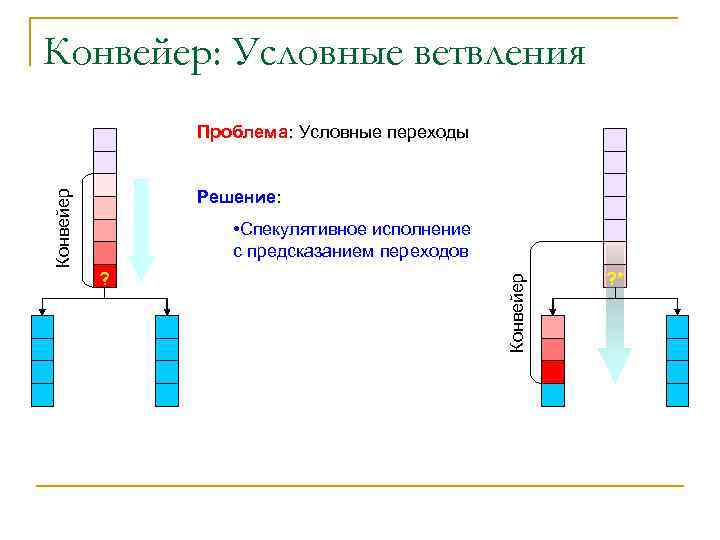

Конвейер: Условные ветвления Проблема: Условные переходы Конвейер Решениe: ? Конвейер • Спекулятивное исполнение с предсказанием переходов ? *

Конвейер: Условные ветвления Проблема: Условные переходы Конвейер Решениe: ? Конвейер • Спекулятивное исполнение с предсказанием переходов ? *

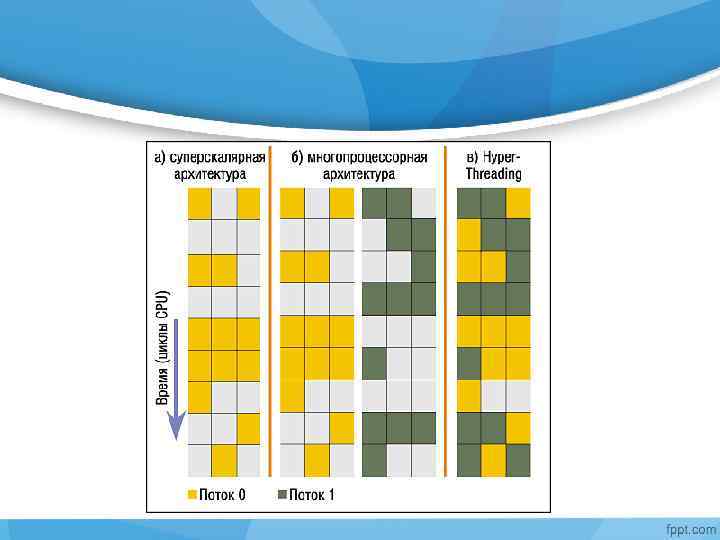

Cуперскалярная архитектура процессора

Cуперскалярная архитектура процессора

Принципы работы

Принципы работы

Представители • Первыми суперскалярными ЭВМ были CDC 6600, CDC 7600, IBM 360/91, Эльбрус-1 • Первым широкодоступным суперскалярным процессором был i 960

Представители • Первыми суперскалярными ЭВМ были CDC 6600, CDC 7600, IBM 360/91, Эльбрус-1 • Первым широкодоступным суперскалярным процессором был i 960

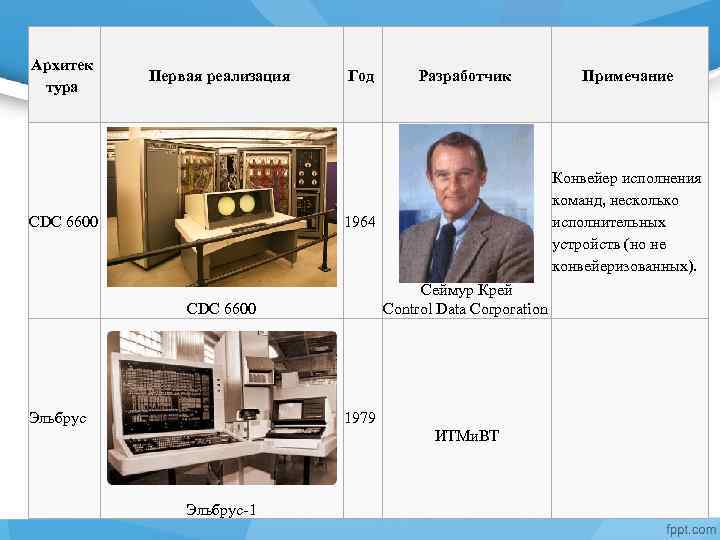

Архитек тура Первая реализация CDC 6600 Год Разработчик Конвейер исполнения команд, несколько исполнительных устройств (но не конвейеризованных). 1964 Сеймур Крей Control Data Corporation CDC 6600 Эльбрус 1979 ИТМи. ВТ Эльбрус-1 Примечание

Архитек тура Первая реализация CDC 6600 Год Разработчик Конвейер исполнения команд, несколько исполнительных устройств (но не конвейеризованных). 1964 Сеймур Крей Control Data Corporation CDC 6600 Эльбрус 1979 ИТМи. ВТ Эльбрус-1 Примечание

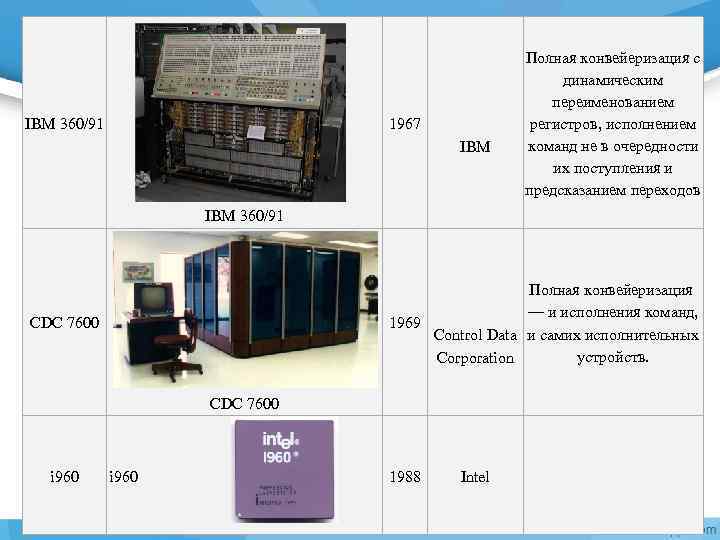

IBM 360/91 1967 IBM Полная конвейеризация с динамическим переименованием регистров, исполнением команд не в очередности их поступления и предсказанием переходов IBM 360/91 Полная конвейеризация — и исполнения команд, 1969 Control Data и самих исполнительных устройств. Corporation CDC 7600 i 960 1988 Intel

IBM 360/91 1967 IBM Полная конвейеризация с динамическим переименованием регистров, исполнением команд не в очередности их поступления и предсказанием переходов IBM 360/91 Полная конвейеризация — и исполнения команд, 1969 Control Data и самих исполнительных устройств. Corporation CDC 7600 i 960 1988 Intel

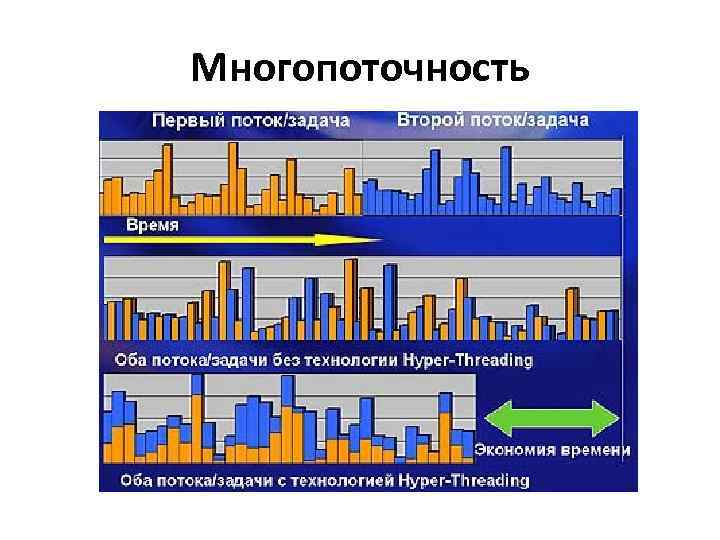

Многопоточность

Многопоточность