Intel Pentium 4.ppt

- Количество слайдов: 74

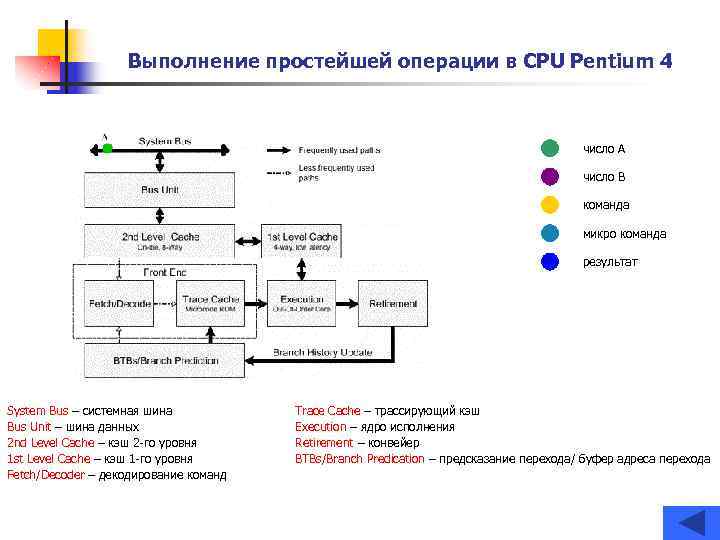

Архитектура процессора Intel Pentium 4 n n n n n Введение Определение понятия “архитектура” Архитектуры CISC и RISC Как работают современные процессоры Наиболее важные сравнительные характеристики процессоров корпорации Intel трех последних поколений Особенности архитектуры Pentium 4 Форматы данных и команды их обработки процессора Intel Pentium 4 Выполнение простейшей операции Заключение Горшенин А. Ю Егоров А. А Москаленко А. С ©

Архитектура процессора Intel Pentium 4 n n n n n Введение Определение понятия “архитектура” Архитектуры CISC и RISC Как работают современные процессоры Наиболее важные сравнительные характеристики процессоров корпорации Intel трех последних поколений Особенности архитектуры Pentium 4 Форматы данных и команды их обработки процессора Intel Pentium 4 Выполнение простейшей операции Заключение Горшенин А. Ю Егоров А. А Москаленко А. С ©

Введение Будучи выпущенным в 1995 году, процессор Intel Pentium Pro стал первым CPU с архитектурой P 6. С тех пор прошло уже достаточно много времени, сменилось несколько поколений процессоров, однако, по сути архитектура не менялась. Семейства Pentium II, Pentium III и Celeron имеют все то же строение ядра, отличаясь по сути только размером и организацией кеша второго уровня и наличием набора команд SSE, появившегося в Pentium III. Естественно, рано или поздно архитектура P 6 должна была устареть. И дело тут вовсе не в невозможности дальнейшего наращивания тактовых частот и даже не в обострившейся в последнее время конкуренцией с AMD. Конечно, нельзя отрицать тот факт, что достигнув частоты в 1 ГГц Intel столкнулся с проблемами в дальнейшем наращивании частоты своих процессоров: Pentium III 1. 13 ГГц даже пришлось отзывать в связи с его нестабильностью. Однако, эту проблему легко можно решить переходом на 0. 13 мкм процесс. Настоящая причина необходимости новой архитектуры кроется глубже. К сожалению, дальнейшее наращивание частоты существующих процессоров приводит все к меньшему росту их производительности. Проблема в том, что латентности, то есть задержки, возникающие при обращении к тем или иным узлам процессора, по нынешним меркам в P 6 уже слишком велики. Именно это явилось основной причиной, по которой Intel затеял разработку Pentium 4, которая выполнена с чистого листа. Таким образом, анонсированный сегодня Pentium 4 - совершенно новый процессор, ничего общего не имеющий со своими предшественниками. В его основе лежит архитектура, названная Intel Net. Burst architecture. Этим названием Intel хотел подчеркнуть, что основная цель нового процессора – ускорить выполнение задач потоковой обработки данных, напрямую связанных с бурно развивающимся Internet. В данной работе мы подробно рассмотрим новейшие технологии и преимущества новой архитектуры Pentium 4. Так же подробно опишем вес арифметические и логические команды используемые в этом процессоре. Попробуем разобраться как работает современный процессор.

Введение Будучи выпущенным в 1995 году, процессор Intel Pentium Pro стал первым CPU с архитектурой P 6. С тех пор прошло уже достаточно много времени, сменилось несколько поколений процессоров, однако, по сути архитектура не менялась. Семейства Pentium II, Pentium III и Celeron имеют все то же строение ядра, отличаясь по сути только размером и организацией кеша второго уровня и наличием набора команд SSE, появившегося в Pentium III. Естественно, рано или поздно архитектура P 6 должна была устареть. И дело тут вовсе не в невозможности дальнейшего наращивания тактовых частот и даже не в обострившейся в последнее время конкуренцией с AMD. Конечно, нельзя отрицать тот факт, что достигнув частоты в 1 ГГц Intel столкнулся с проблемами в дальнейшем наращивании частоты своих процессоров: Pentium III 1. 13 ГГц даже пришлось отзывать в связи с его нестабильностью. Однако, эту проблему легко можно решить переходом на 0. 13 мкм процесс. Настоящая причина необходимости новой архитектуры кроется глубже. К сожалению, дальнейшее наращивание частоты существующих процессоров приводит все к меньшему росту их производительности. Проблема в том, что латентности, то есть задержки, возникающие при обращении к тем или иным узлам процессора, по нынешним меркам в P 6 уже слишком велики. Именно это явилось основной причиной, по которой Intel затеял разработку Pentium 4, которая выполнена с чистого листа. Таким образом, анонсированный сегодня Pentium 4 - совершенно новый процессор, ничего общего не имеющий со своими предшественниками. В его основе лежит архитектура, названная Intel Net. Burst architecture. Этим названием Intel хотел подчеркнуть, что основная цель нового процессора – ускорить выполнение задач потоковой обработки данных, напрямую связанных с бурно развивающимся Internet. В данной работе мы подробно рассмотрим новейшие технологии и преимущества новой архитектуры Pentium 4. Так же подробно опишем вес арифметические и логические команды используемые в этом процессоре. Попробуем разобраться как работает современный процессор.

Определение понятия "архитектура" Термин "архитектура системы" часто употребляется как в узком, так и в широком смысле этого слова. В узком смысле под архитектурой понимается архитектура набора команд. Архитектура набора команд служит границей между аппаратурой и программным обеспечением и представляет ту часть системы, которая видна программисту или разработчику компиляторов. Следует отметить, что это наиболее частое употребление этого термина. В широком смысле архитектура охватывает понятие организации системы, включающее такие высокоуровневые аспекты разработки компьютера как систему памяти, структуру системной шины, организацию ввода/вывода и т. п. Применительно к вычислительным системам термин "архитектура" может быть определен как распределение функций, реализуемых системой, между ее уровнями, точнее как определение границ между этими уровнями. Таким образом, архитектура вычислительной системы предполагает многоуровневую организацию. Архитектура первого уровня определяет, какие функции по обработке данных выполняются системой в целом, а какие возлагаются на внешний мир (пользователей, операторов, администраторов баз данных и т. д. ). Система взаимодействует с внешним миром через набор интерфейсов: языки (язык оператора, языки программирования, языки описания и манипулирования базой данных, язык управления заданиями) и системные программы (программы-утилиты, программы редактирования, сортировки, сохранения и восстановления информации). Интерфейсы следующих уровней могут разграничивать определенные уровни внутри программного обеспечения. Например, уровень управления логическими ресурсами может включать реализацию таких функций, как управление базой данных, файлами, виртуальной памятью, сетевой телеобработкой. К уровню управления физическими ресурсами относятся функции управления внешней и оперативной памятью, управления процессами, выполняющимися в системе. Следующий уровень отражает основную линию разграничения системы, а именно границу между системным программным обеспечением и аппаратурой. Эту идею можно развить и дальше и говорить о распределении функций между отдельными частями физической системы. Например, некоторый интерфейс определяет, какие функции реализуют центральные процессоры, а какие - процессоры ввода/вывода. Архитектура следующего уровня определяет разграничение функций между процессорами ввода/вывода и контроллерами внешних устройств. В свою очередь можно разграничить функции, реализуемые контроллерами и самими устройствами ввода/вывода (терминалами, модемами, накопителями на магнитных дисках и лентах). Архитектура таких уровней часто называется архитектурой физического ввода/вывода.

Определение понятия "архитектура" Термин "архитектура системы" часто употребляется как в узком, так и в широком смысле этого слова. В узком смысле под архитектурой понимается архитектура набора команд. Архитектура набора команд служит границей между аппаратурой и программным обеспечением и представляет ту часть системы, которая видна программисту или разработчику компиляторов. Следует отметить, что это наиболее частое употребление этого термина. В широком смысле архитектура охватывает понятие организации системы, включающее такие высокоуровневые аспекты разработки компьютера как систему памяти, структуру системной шины, организацию ввода/вывода и т. п. Применительно к вычислительным системам термин "архитектура" может быть определен как распределение функций, реализуемых системой, между ее уровнями, точнее как определение границ между этими уровнями. Таким образом, архитектура вычислительной системы предполагает многоуровневую организацию. Архитектура первого уровня определяет, какие функции по обработке данных выполняются системой в целом, а какие возлагаются на внешний мир (пользователей, операторов, администраторов баз данных и т. д. ). Система взаимодействует с внешним миром через набор интерфейсов: языки (язык оператора, языки программирования, языки описания и манипулирования базой данных, язык управления заданиями) и системные программы (программы-утилиты, программы редактирования, сортировки, сохранения и восстановления информации). Интерфейсы следующих уровней могут разграничивать определенные уровни внутри программного обеспечения. Например, уровень управления логическими ресурсами может включать реализацию таких функций, как управление базой данных, файлами, виртуальной памятью, сетевой телеобработкой. К уровню управления физическими ресурсами относятся функции управления внешней и оперативной памятью, управления процессами, выполняющимися в системе. Следующий уровень отражает основную линию разграничения системы, а именно границу между системным программным обеспечением и аппаратурой. Эту идею можно развить и дальше и говорить о распределении функций между отдельными частями физической системы. Например, некоторый интерфейс определяет, какие функции реализуют центральные процессоры, а какие - процессоры ввода/вывода. Архитектура следующего уровня определяет разграничение функций между процессорами ввода/вывода и контроллерами внешних устройств. В свою очередь можно разграничить функции, реализуемые контроллерами и самими устройствами ввода/вывода (терминалами, модемами, накопителями на магнитных дисках и лентах). Архитектура таких уровней часто называется архитектурой физического ввода/вывода.

Архитектуры CISC и RISC Здесь рассматриваются базовые свойства архитектур CISC и RISC, а также особенности интеграции элементов RISC-архитектуры в процессорах x 86. Особое внимание уделяется описанию преимуществ и недостатков этой интеграции. Показано естественность взаимообогащения CISC и RISC-процессоров эффективными аппаратно-программными решениями, а также практичность развития процессоров в этом направлении. Организация первых моделей процессоров - i 8086/8088 - была направлена, в частности, на сокращение объёма программ, критичного для систем того времени, отличавшихся малой оперативной памятью. Расширение спектра операций, реализуемых системой команд, позволило уменьшить размер программ, а также трудоёмкость их написания и отладки. Однако увеличение числа команд повысило трудоёмкость разработки их топологических и микропрограммных реализаций. Последнее проявилось в удлинении сроков разработки CISC-процессоров, а также в проявлении различных ошибок в их работе. Кроме того, нерегулярность потока команд ограничила развитие топологии временным параллелизмом обработки инструкций на конвейере "выборка команды- дешифрация команды- выборка данных- вычисление- запись результата". Эти недостатки обусловили необходимость разработки альтернативной архитектуры, нацеленной, прежде всего, на снижение нерегулярности потока команд уменьшением их общего количества. Это было реализовано в RISC-процессорах, название которых означает "чипы с сокращённой системой команд" (Reduced Instruction Set Computer). Одновременно "классические" процессоры получили обозначение CISC (Complex Instruction Set Computer) - компьютер со сложным набором инструкций. Сокращение нерегулярности потока команд позволило обогатить топологию RISC-процессоров пространственным параллелизмом, специализированными аппаратными АЛУ (ALU - блок логики и арифметики = Arithmetic (and) Logic Unit), независимыми кэш данных и команд, раздельными шинами ввода-вывода. Последние, в частности, увеличили длину конвейеров команд. Всё это повысило и производительность - увеличением числа операций, выполняемых за один такт, и быстродействие - сокращением пути транзактов - RISC-процессоров. При этом срок разработки данных чипов свидетельствует о том, что её трудоёмкость меньше, чем в случае CISCпроцессоров. На мировых рынках CISC-процессоры представлены, в основном, клонами процессоров Intel серии x 86, производимыми AMD, Cyrix, а RISC - чипами Alpha, Power. PC, SPARC. Уступая во многом последним, процессоры x 86 сохранили лидерство на рынке персональных систем лишь благодаря совместимости с программным обеспечением младших моделей, общая стоимость которого - в начале 90 -х годов - составила несколько миллиардов долларов США. В свою очередь, достоинства RISC-процессоров укрепили их позиции на более молодом рынке высокопроизводительных машин.

Архитектуры CISC и RISC Здесь рассматриваются базовые свойства архитектур CISC и RISC, а также особенности интеграции элементов RISC-архитектуры в процессорах x 86. Особое внимание уделяется описанию преимуществ и недостатков этой интеграции. Показано естественность взаимообогащения CISC и RISC-процессоров эффективными аппаратно-программными решениями, а также практичность развития процессоров в этом направлении. Организация первых моделей процессоров - i 8086/8088 - была направлена, в частности, на сокращение объёма программ, критичного для систем того времени, отличавшихся малой оперативной памятью. Расширение спектра операций, реализуемых системой команд, позволило уменьшить размер программ, а также трудоёмкость их написания и отладки. Однако увеличение числа команд повысило трудоёмкость разработки их топологических и микропрограммных реализаций. Последнее проявилось в удлинении сроков разработки CISC-процессоров, а также в проявлении различных ошибок в их работе. Кроме того, нерегулярность потока команд ограничила развитие топологии временным параллелизмом обработки инструкций на конвейере "выборка команды- дешифрация команды- выборка данных- вычисление- запись результата". Эти недостатки обусловили необходимость разработки альтернативной архитектуры, нацеленной, прежде всего, на снижение нерегулярности потока команд уменьшением их общего количества. Это было реализовано в RISC-процессорах, название которых означает "чипы с сокращённой системой команд" (Reduced Instruction Set Computer). Одновременно "классические" процессоры получили обозначение CISC (Complex Instruction Set Computer) - компьютер со сложным набором инструкций. Сокращение нерегулярности потока команд позволило обогатить топологию RISC-процессоров пространственным параллелизмом, специализированными аппаратными АЛУ (ALU - блок логики и арифметики = Arithmetic (and) Logic Unit), независимыми кэш данных и команд, раздельными шинами ввода-вывода. Последние, в частности, увеличили длину конвейеров команд. Всё это повысило и производительность - увеличением числа операций, выполняемых за один такт, и быстродействие - сокращением пути транзактов - RISC-процессоров. При этом срок разработки данных чипов свидетельствует о том, что её трудоёмкость меньше, чем в случае CISCпроцессоров. На мировых рынках CISC-процессоры представлены, в основном, клонами процессоров Intel серии x 86, производимыми AMD, Cyrix, а RISC - чипами Alpha, Power. PC, SPARC. Уступая во многом последним, процессоры x 86 сохранили лидерство на рынке персональных систем лишь благодаря совместимости с программным обеспечением младших моделей, общая стоимость которого - в начале 90 -х годов - составила несколько миллиардов долларов США. В свою очередь, достоинства RISC-процессоров укрепили их позиции на более молодом рынке высокопроизводительных машин.

Архитектуры CISC и RISC Несмотря на формальное разделение "сфер влияния", между представителями этих архитектур в начале 90 -х годов началась острая конкуренция за превентивное улучшение характеристик. В первую очередь, производительности и её отношения к трудоёмкости разработки процессоров. Следуя принципу "бить врага его оружием", создатели и CISC, и RISC-процессоров нередко боролись с конкурентами, заимствуя их удачные решения. Первыми на то решились разработчики Intel, реализовавшие в i 486 пространственный параллелизм вычислений с фиксированной и плавающей запятой. Поддержка каждого АЛУ своей шиной данных/команд и регистровым блоком повысила производительность i 486 одновременным выполнением указанных команд. Кроме того, интеграция кэш и очереди команд позволила поднять частоту ядра процессора в 2 -3 раза в сравнении с системной шиной. Однако совместное размещение данных и команд ограничило эффективность кэш необходимостью его полной перезагрузки после выполнения команд переходов. Для устранения недостатка в Pentium реализованы раздельные кэш для команд и данных, позволяющие после переходов перезагружать лишь команды - такое решение называется Гарвардской архитектурой, а также предсказание переходов, снижающее частоту перезагрузок. Последнее достигается предварительной загрузкой в кэш команд с обоих разветвлений. Введение второго целочисленного тракта, состоящего из АЛУ, адресного блока, шин данных/команд, и работающего на общий блок регистров, повысило производительность поддержкой параллельной обработки целочисленных данных. Развитием данной тенденции стало обогащение Pentium MMX мультимедийным трактом, образованным АЛУ, шинами данных/команд и регистровым файлом. При этом в случае выборки двух целочисленных команд, зависящих по данным, каждая из них выполняется последовательно, что снижает эффективность работы процессора. Частично поправило ситуацию создание оптимизирующих рекомпиляторов, например, Pen_Opt фирмы Intel, разделяющих по возможности такие команды. Реализация описанного управления обработкой команд CISC-формата вызвала дополнительный рост трудоёмкости разработки Pentium в сравнении с i 8086/i 486, что привело не только к увеличению её реального срока на 27% в сравнении с ожидаемым, но и к проявлению ошибок в первых моделях данного процессора. Учтя это, компания Intel реализовала в Pentium Pro RISC-подобную организацию вычислений. Интерпретация команд х86 внутренними - RISC 86 - инструкциями VLIW-формата помимо снижения нерегулярности их потока, обеспечила синхронную загрузку четырёх операционных - по два с плавающей и фиксированной запятой - АЛУ этого чипа. Термин VLIW расшифровывается как "очень длинное командное слово" (Very Long Instruction Word). Инструкции этого формата содержат команды для всех параллельных АЛУ.

Архитектуры CISC и RISC Несмотря на формальное разделение "сфер влияния", между представителями этих архитектур в начале 90 -х годов началась острая конкуренция за превентивное улучшение характеристик. В первую очередь, производительности и её отношения к трудоёмкости разработки процессоров. Следуя принципу "бить врага его оружием", создатели и CISC, и RISC-процессоров нередко боролись с конкурентами, заимствуя их удачные решения. Первыми на то решились разработчики Intel, реализовавшие в i 486 пространственный параллелизм вычислений с фиксированной и плавающей запятой. Поддержка каждого АЛУ своей шиной данных/команд и регистровым блоком повысила производительность i 486 одновременным выполнением указанных команд. Кроме того, интеграция кэш и очереди команд позволила поднять частоту ядра процессора в 2 -3 раза в сравнении с системной шиной. Однако совместное размещение данных и команд ограничило эффективность кэш необходимостью его полной перезагрузки после выполнения команд переходов. Для устранения недостатка в Pentium реализованы раздельные кэш для команд и данных, позволяющие после переходов перезагружать лишь команды - такое решение называется Гарвардской архитектурой, а также предсказание переходов, снижающее частоту перезагрузок. Последнее достигается предварительной загрузкой в кэш команд с обоих разветвлений. Введение второго целочисленного тракта, состоящего из АЛУ, адресного блока, шин данных/команд, и работающего на общий блок регистров, повысило производительность поддержкой параллельной обработки целочисленных данных. Развитием данной тенденции стало обогащение Pentium MMX мультимедийным трактом, образованным АЛУ, шинами данных/команд и регистровым файлом. При этом в случае выборки двух целочисленных команд, зависящих по данным, каждая из них выполняется последовательно, что снижает эффективность работы процессора. Частично поправило ситуацию создание оптимизирующих рекомпиляторов, например, Pen_Opt фирмы Intel, разделяющих по возможности такие команды. Реализация описанного управления обработкой команд CISC-формата вызвала дополнительный рост трудоёмкости разработки Pentium в сравнении с i 8086/i 486, что привело не только к увеличению её реального срока на 27% в сравнении с ожидаемым, но и к проявлению ошибок в первых моделях данного процессора. Учтя это, компания Intel реализовала в Pentium Pro RISC-подобную организацию вычислений. Интерпретация команд х86 внутренними - RISC 86 - инструкциями VLIW-формата помимо снижения нерегулярности их потока, обеспечила синхронную загрузку четырёх операционных - по два с плавающей и фиксированной запятой - АЛУ этого чипа. Термин VLIW расшифровывается как "очень длинное командное слово" (Very Long Instruction Word). Инструкции этого формата содержат команды для всех параллельных АЛУ.

Архитектуры CISC и RISC Обогащение управления обработкой предвыборкой данных и команд, предполагаемых к обработке в ближайшие 20 тактов, повысило регулярность загрузки вычислительных трактов. В свою очередь, осуществление предвыборки из интегрированного на кристалле кэш второго уровня, обслуживаемого раздельными шинами "интерфейс-кэш" и "кэш-АЛУ" и работающего на частоте АЛУ, повысило быстродействие подготовки команд в сравнении с внешними кэш. Дополнительное повышение производительности Pentium Pro обеспечило увеличение длины команд до 11 ступеней введением ступеней трансляции и предвыборки. Кроме того, интеграция кэш второго уровня позволила умножать частоту ядра в 5 -6 раз. В архитектуре Р 6 RISC-решения впервые в семействе х86 перестали быть лишь дополнением исконных CISC-средств повышения производительности - роста разрядности, отложенной записи шины и других. Поэтому частица PRO в названии первого процессора этой серии обозначает "Полноценная RISC-архитектура" (Precision RISC Organization). Топологические новинки Pentium II - интеграция тракта MMX, мультипроцессорный интерфейс Xeon, вынесение кэш второго уровня на кристалл в корпусе чипа, как и полное устранение кэш второго уровня в Celeron, не имеют в данном случае качественной роли и направлены на оптимизацию отношения характеристик этих процессоров, к их цене. При этом сокращение нерегулярности потока RISC 86 -инструкицй ограничило рост требований к развитию управления вычислениями в сравнении с Pentium. Одновременно снижение трудоёмкости разработки аппаратно-программных реализаций алгоритмов работы Pentium Pro, достигнутое развитием САПР, ослабило влияние развития обработки данных, оцениваемого ростом объёма информации, заложенной в реализациях этой обработки, на общую трудоёмкость разработки процессоров, оцениваемую её длительностью. Последнее создало возможность оптимизации соотношения характеристик чипов и их трудоёмкости не снижением последней ограничением внедрения прогрессивных решений в CISC-архитектуру или ограничением функциональных возможностей RISC-процессоров, а ростом характеристик, достигаемым сочетанием преимуществ упомянутых архитектур. Сказанное иллюстрирует и организация современных RISC-процессоров. Их отличает, в данном случае, развитие систем команд с целью сохранения иерархической совместимости и снижения трудоёмкости разработки программ. Это сближает технологии обработки команд процессорами упомянутых архитектур. Например, Super. Sparc взяли от последних моделей х86 предсказание переходов и предварительную интерпретацию кода. Таким образом, развиваясь, каждая из рассмотренных архитектур, "отказавшись" от своих черт - CISC от скалярности вычислений, RISC от "простоты" системы команд, приобрела лучшие черты конкурента, что повысило характеристики её представителей.

Архитектуры CISC и RISC Обогащение управления обработкой предвыборкой данных и команд, предполагаемых к обработке в ближайшие 20 тактов, повысило регулярность загрузки вычислительных трактов. В свою очередь, осуществление предвыборки из интегрированного на кристалле кэш второго уровня, обслуживаемого раздельными шинами "интерфейс-кэш" и "кэш-АЛУ" и работающего на частоте АЛУ, повысило быстродействие подготовки команд в сравнении с внешними кэш. Дополнительное повышение производительности Pentium Pro обеспечило увеличение длины команд до 11 ступеней введением ступеней трансляции и предвыборки. Кроме того, интеграция кэш второго уровня позволила умножать частоту ядра в 5 -6 раз. В архитектуре Р 6 RISC-решения впервые в семействе х86 перестали быть лишь дополнением исконных CISC-средств повышения производительности - роста разрядности, отложенной записи шины и других. Поэтому частица PRO в названии первого процессора этой серии обозначает "Полноценная RISC-архитектура" (Precision RISC Organization). Топологические новинки Pentium II - интеграция тракта MMX, мультипроцессорный интерфейс Xeon, вынесение кэш второго уровня на кристалл в корпусе чипа, как и полное устранение кэш второго уровня в Celeron, не имеют в данном случае качественной роли и направлены на оптимизацию отношения характеристик этих процессоров, к их цене. При этом сокращение нерегулярности потока RISC 86 -инструкицй ограничило рост требований к развитию управления вычислениями в сравнении с Pentium. Одновременно снижение трудоёмкости разработки аппаратно-программных реализаций алгоритмов работы Pentium Pro, достигнутое развитием САПР, ослабило влияние развития обработки данных, оцениваемого ростом объёма информации, заложенной в реализациях этой обработки, на общую трудоёмкость разработки процессоров, оцениваемую её длительностью. Последнее создало возможность оптимизации соотношения характеристик чипов и их трудоёмкости не снижением последней ограничением внедрения прогрессивных решений в CISC-архитектуру или ограничением функциональных возможностей RISC-процессоров, а ростом характеристик, достигаемым сочетанием преимуществ упомянутых архитектур. Сказанное иллюстрирует и организация современных RISC-процессоров. Их отличает, в данном случае, развитие систем команд с целью сохранения иерархической совместимости и снижения трудоёмкости разработки программ. Это сближает технологии обработки команд процессорами упомянутых архитектур. Например, Super. Sparc взяли от последних моделей х86 предсказание переходов и предварительную интерпретацию кода. Таким образом, развиваясь, каждая из рассмотренных архитектур, "отказавшись" от своих черт - CISC от скалярности вычислений, RISC от "простоты" системы команд, приобрела лучшие черты конкурента, что повысило характеристики её представителей.

Архитектуры CISC и RISC Это подтверждает и процессор Merced, разрабатываемый недавними противниками - Intel и Hewlett Packard. Имеющиеся сведения позволяют предположить, что его архитектура продолжит тенденции Pentium Pro по оптимизации обработки внутренних VLIW-подобных команд реализацией эффективных архитектурных решений при одновременной оптимизации преобразования "внешних" инструкций. Особо отмечаются намерения создания двух вариантов этого чипа, различающихся лишь множеством этих инструкций. Первый будет совместим с CISC-семейством x 86, второй - с RISC-процессорами Alpha. Будучи "един в двух лицах", Merced ознаменует прекращение соперничества CISC и RISC, в ходе которого представители данных архитектура улучшили свои характеристики реализацией лучших аппаратнопрограммных решений конкурентов. Это позволяет предположить, что дальнейшее развитие массовых процессоров пройдёт по пути развития топологических и микропрограммных решений вычислительного ядра RISC-организации при одновременном повышении возможностей CISC-подобной "внешней" системы команд.

Архитектуры CISC и RISC Это подтверждает и процессор Merced, разрабатываемый недавними противниками - Intel и Hewlett Packard. Имеющиеся сведения позволяют предположить, что его архитектура продолжит тенденции Pentium Pro по оптимизации обработки внутренних VLIW-подобных команд реализацией эффективных архитектурных решений при одновременной оптимизации преобразования "внешних" инструкций. Особо отмечаются намерения создания двух вариантов этого чипа, различающихся лишь множеством этих инструкций. Первый будет совместим с CISC-семейством x 86, второй - с RISC-процессорами Alpha. Будучи "един в двух лицах", Merced ознаменует прекращение соперничества CISC и RISC, в ходе которого представители данных архитектура улучшили свои характеристики реализацией лучших аппаратнопрограммных решений конкурентов. Это позволяет предположить, что дальнейшее развитие массовых процессоров пройдёт по пути развития топологических и микропрограммных решений вычислительного ядра RISC-организации при одновременном повышении возможностей CISC-подобной "внешней" системы команд.

Как работают современные процессоры Для начала -- небольшая, но совершенно необходимая теоретическая часть. Во-первых, все современные CPU используют конвейерную (pipelined) архитектуру в различных ее вариантах. Это означает, что любая команда выполняется не одним, а несколькими блоками, объединенными в конвейер. Первым процессором, в котором было применено такое решение, стал Intel 486, он имел конвейер из пяти ступеней. Однако это еще не все. Дело в том, что внутри любой современный CPU уже давно "наполовину RISC", т. е. фактически он исполняет совсем другие команды, а не те, что поступают к нему из ОЗУ. Эра процессоров, "напрямую" выполнявших команды x 86 -ассемблера, закончилась еще с приходом Intel Pentium Pro/II и AMD K 5/K 6. Все последующие CPU сначала осуществляют преобразование довольно "емких" x 86 -команд в более простой RISC-подобный код (как правило, при этом одна команда преобразуется в несколько), исполнением которого и занимается непосредственно ядро процессора. Такой, на первый взгляд, сложный путь был избран потому, что ядро, исполняющее простые команды, гораздо легче "переносит" высокие частоты работы. В общем, спор между низкочастотным сложным ядром и высокочастотным простым уже давно и однозначно решен в пользу последнего. При этом появляется еще одна возможность увеличения скорости исполнения команд -- параллелизация обработки. То есть несколько RISC-подобных команд обрабатываются параллельно -- за один такт, но на разных участках конвейера. Ну и кроме того, начиная с Intel Pentium, архитектура современных CPU стала "суперскалярной" (superpipelined), это означает, что конвейеров в них несколько и работают они параллельно

Как работают современные процессоры Для начала -- небольшая, но совершенно необходимая теоретическая часть. Во-первых, все современные CPU используют конвейерную (pipelined) архитектуру в различных ее вариантах. Это означает, что любая команда выполняется не одним, а несколькими блоками, объединенными в конвейер. Первым процессором, в котором было применено такое решение, стал Intel 486, он имел конвейер из пяти ступеней. Однако это еще не все. Дело в том, что внутри любой современный CPU уже давно "наполовину RISC", т. е. фактически он исполняет совсем другие команды, а не те, что поступают к нему из ОЗУ. Эра процессоров, "напрямую" выполнявших команды x 86 -ассемблера, закончилась еще с приходом Intel Pentium Pro/II и AMD K 5/K 6. Все последующие CPU сначала осуществляют преобразование довольно "емких" x 86 -команд в более простой RISC-подобный код (как правило, при этом одна команда преобразуется в несколько), исполнением которого и занимается непосредственно ядро процессора. Такой, на первый взгляд, сложный путь был избран потому, что ядро, исполняющее простые команды, гораздо легче "переносит" высокие частоты работы. В общем, спор между низкочастотным сложным ядром и высокочастотным простым уже давно и однозначно решен в пользу последнего. При этом появляется еще одна возможность увеличения скорости исполнения команд -- параллелизация обработки. То есть несколько RISC-подобных команд обрабатываются параллельно -- за один такт, но на разных участках конвейера. Ну и кроме того, начиная с Intel Pentium, архитектура современных CPU стала "суперскалярной" (superpipelined), это означает, что конвейеров в них несколько и работают они параллельно

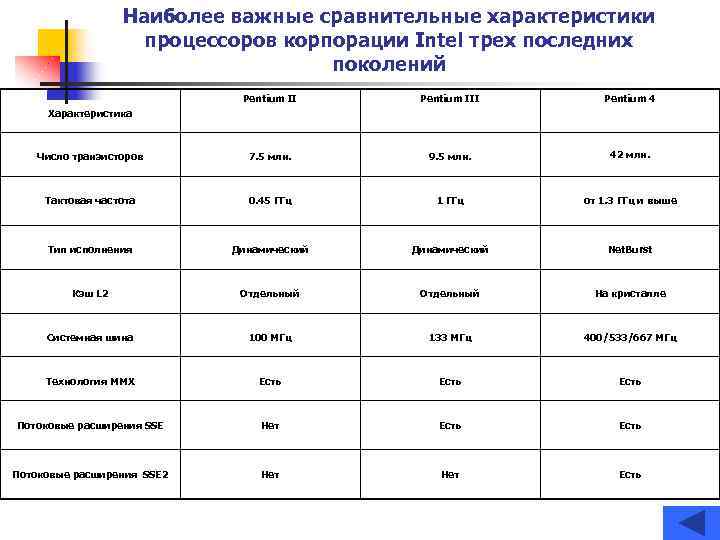

Наиболее важные сравнительные характеристики процессоров корпорации Intel трех последних поколений Pentium III Pentium 4 Число транзисторов 7. 5 млн. 9. 5 млн. 42 млн. Тактовая частота 0. 45 ГГц 1 ГГц от 1. 3 ГГц и выше Тип исполнения Динамический Net. Burst Кэш L 2 Отдельный На кристалле Системная шина 100 МГц 133 МГц 400/533/667 МГц Технология MMX Есть Потоковые расширения SSE Нет Есть Потоковые расширения SSE 2 Нет Есть Характеристика

Наиболее важные сравнительные характеристики процессоров корпорации Intel трех последних поколений Pentium III Pentium 4 Число транзисторов 7. 5 млн. 9. 5 млн. 42 млн. Тактовая частота 0. 45 ГГц 1 ГГц от 1. 3 ГГц и выше Тип исполнения Динамический Net. Burst Кэш L 2 Отдельный На кристалле Системная шина 100 МГц 133 МГц 400/533/667 МГц Технология MMX Есть Потоковые расширения SSE Нет Есть Потоковые расширения SSE 2 Нет Есть Характеристика

Особенности архитектуры n n n n n Архитектура Net. Burst Hyper Pipelined Technology n Принцип работы n Описание ступеней конвейера Advanced Dynamic Execution Trace Cache Rapid Execute Engine SSE 2 L 1 кэш L 2 Advanced Transfer Cache Процессор

Особенности архитектуры n n n n n Архитектура Net. Burst Hyper Pipelined Technology n Принцип работы n Описание ступеней конвейера Advanced Dynamic Execution Trace Cache Rapid Execute Engine SSE 2 L 1 кэш L 2 Advanced Transfer Cache Процессор

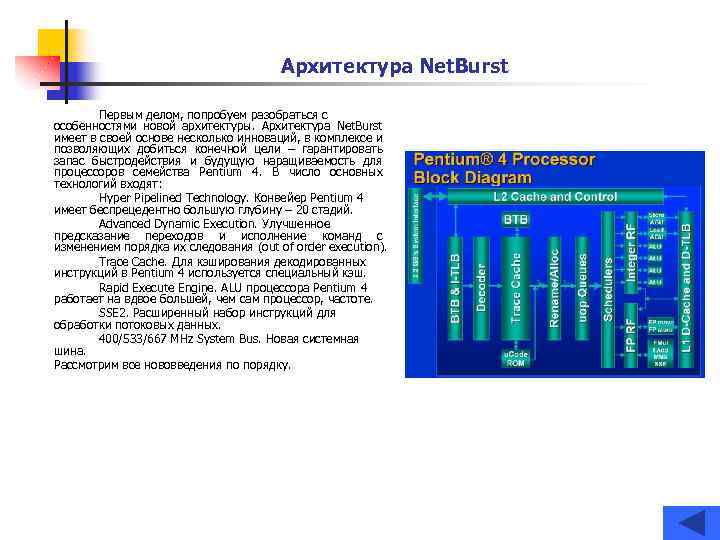

Архитектура Net. Burst Первым делом, попробуем разобраться с особенностями новой архитектуры. Архитектура Net. Burst имеет в своей основе несколько инноваций, в комплексе и позволяющих добиться конечной цели – гарантировать запас быстродействия и будущую наращиваемость для процессоров семейства Pentium 4. В число основных технологий входят: Hyper Pipelined Technology. Конвейер Pentium 4 имеет беспрецедентно большую глубину – 20 стадий. Advanced Dynamic Execution. Улучшенное предсказание переходов и исполнение команд с изменением порядка их следования (out of order execution). Trace Cache. Для кэширования декодированных инструкций в Pentium 4 используется специальный кэш. Rapid Execute Engine. ALU процессора Pentium 4 работает на вдвое большей, чем сам процессор, частоте. SSE 2. Расширенный набор инструкций для обработки потоковых данных. 400/533/667 MHz System Bus. Новая системная шина. Рассмотрим все нововведения по порядку.

Архитектура Net. Burst Первым делом, попробуем разобраться с особенностями новой архитектуры. Архитектура Net. Burst имеет в своей основе несколько инноваций, в комплексе и позволяющих добиться конечной цели – гарантировать запас быстродействия и будущую наращиваемость для процессоров семейства Pentium 4. В число основных технологий входят: Hyper Pipelined Technology. Конвейер Pentium 4 имеет беспрецедентно большую глубину – 20 стадий. Advanced Dynamic Execution. Улучшенное предсказание переходов и исполнение команд с изменением порядка их следования (out of order execution). Trace Cache. Для кэширования декодированных инструкций в Pentium 4 используется специальный кэш. Rapid Execute Engine. ALU процессора Pentium 4 работает на вдвое большей, чем сам процессор, частоте. SSE 2. Расширенный набор инструкций для обработки потоковых данных. 400/533/667 MHz System Bus. Новая системная шина. Рассмотрим все нововведения по порядку.

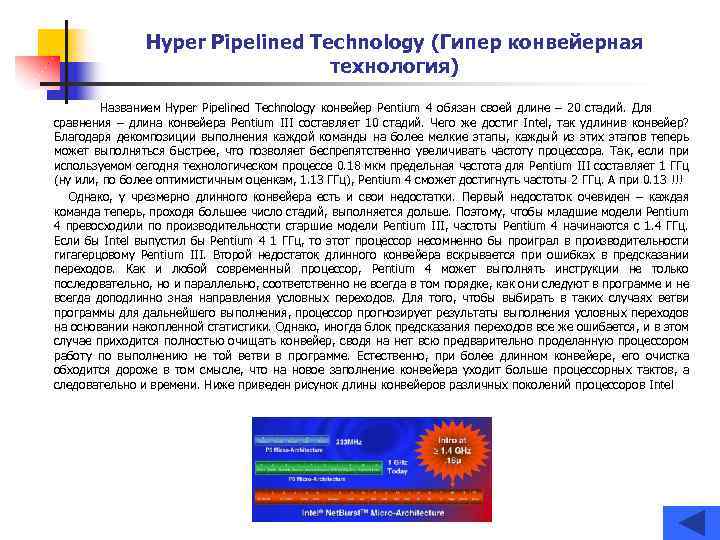

Hyper Pipelined Technology (Гипер конвейерная технология) Названием Hyper Pipelined Technology конвейер Pentium 4 обязан своей длине – 20 стадий. Для сравнения – длина конвейера Pentium III составляет 10 стадий. Чего же достиг Intel, так удлинив конвейер? Благодаря декомпозиции выполнения каждой команды на более мелкие этапы, каждый из этих этапов теперь может выполняться быстрее, что позволяет беспрепятственно увеличивать частоту процессора. Так, если при используемом сегодня технологическом процессе 0. 18 мкм предельная частота для Pentium III составляет 1 ГГц (ну или, по более оптимистичным оценкам, 1. 13 ГГц), Pentium 4 сможет достигнуть частоты 2 ГГц. А при 0. 13 !!! Однако, у чрезмерно длинного конвейера есть и свои недостатки. Первый недостаток очевиден – каждая команда теперь, проходя большее число стадий, выполняется дольше. Поэтому, чтобы младшие модели Pentium 4 превосходили по производительности старшие модели Pentium III, частоты Pentium 4 начинаются с 1. 4 ГГц. Если бы Intel выпустил бы Pentium 4 1 ГГц, то этот процессор несомненно бы проиграл в производительности гигагерцовому Pentium III. Второй недостаток длинного конвейера вскрывается при ошибках в предсказании переходов. Как и любой современный процессор, Pentium 4 может выполнять инструкции не только последовательно, но и параллельно, соответственно не всегда в том порядке, как они следуют в программе и не всегда доподлинно зная направления условных переходов. Для того, чтобы выбирать в таких случаях ветви программы для дальнейшего выполнения, процессор прогнозирует результаты выполнения условных переходов на основании накопленной статистики. Однако, иногда блок предсказания переходов все же ошибается, и в этом случае приходится полностью очищать конвейер, сводя на нет всю предварительно проделанную процессором работу по выполнению не той ветви в программе. Естественно, при более длинном конвейере, его очистка обходится дороже в том смысле, что на новое заполнение конвейера уходит больше процессорных тактов, а следовательно и времени. Ниже приведен рисунок длины конвейеров различных поколений процессоров Intel

Hyper Pipelined Technology (Гипер конвейерная технология) Названием Hyper Pipelined Technology конвейер Pentium 4 обязан своей длине – 20 стадий. Для сравнения – длина конвейера Pentium III составляет 10 стадий. Чего же достиг Intel, так удлинив конвейер? Благодаря декомпозиции выполнения каждой команды на более мелкие этапы, каждый из этих этапов теперь может выполняться быстрее, что позволяет беспрепятственно увеличивать частоту процессора. Так, если при используемом сегодня технологическом процессе 0. 18 мкм предельная частота для Pentium III составляет 1 ГГц (ну или, по более оптимистичным оценкам, 1. 13 ГГц), Pentium 4 сможет достигнуть частоты 2 ГГц. А при 0. 13 !!! Однако, у чрезмерно длинного конвейера есть и свои недостатки. Первый недостаток очевиден – каждая команда теперь, проходя большее число стадий, выполняется дольше. Поэтому, чтобы младшие модели Pentium 4 превосходили по производительности старшие модели Pentium III, частоты Pentium 4 начинаются с 1. 4 ГГц. Если бы Intel выпустил бы Pentium 4 1 ГГц, то этот процессор несомненно бы проиграл в производительности гигагерцовому Pentium III. Второй недостаток длинного конвейера вскрывается при ошибках в предсказании переходов. Как и любой современный процессор, Pentium 4 может выполнять инструкции не только последовательно, но и параллельно, соответственно не всегда в том порядке, как они следуют в программе и не всегда доподлинно зная направления условных переходов. Для того, чтобы выбирать в таких случаях ветви программы для дальнейшего выполнения, процессор прогнозирует результаты выполнения условных переходов на основании накопленной статистики. Однако, иногда блок предсказания переходов все же ошибается, и в этом случае приходится полностью очищать конвейер, сводя на нет всю предварительно проделанную процессором работу по выполнению не той ветви в программе. Естественно, при более длинном конвейере, его очистка обходится дороже в том смысле, что на новое заполнение конвейера уходит больше процессорных тактов, а следовательно и времени. Ниже приведен рисунок длины конвейеров различных поколений процессоров Intel

Принцип работы конвейера В в этом разделе мы внимательно рассмотрим принцип работы нового конвейера Pentium 4 реализован другой подход нежели в процессорах других фирм. На ступени выполнения там используется меньшее количество функциональных устройств. Но каждое из них обладает более длинным и более быстрым конвейером. Это означает, что каждое функциональное устройство имеет большее количество доступных для выполнения тактов (execution slots) и таким образом способно одновременно выполнять довольно много инструкций. Так, скажем, вместо трёх устройств для выполнения операций с плавающей точкой, работающих медленно, но параллельно, Pentium 4 имеет только одно такое устройство, которое может быстрее одновременно выполнять большее количество инструкций на различных ступенях. Важно отметить, что для того, чтобы полностью загружать быстрые конвейерные функциональные устройства в Pentium 4, препроцессор должен обладать большим буфером, способным вмещать в себя и планировать огромное количество инструкций. Процессор Pentium 4 может одновременно выполнять на различных ступенях до 126 инструкций. Отсюда следует, что для внеочередного выполнения процессор должен анализировать значительно большее количество инструкций на взаимозависимость, а затем преобразовывать их для быстрой передачи функциональным устройствам. Так работает конвейер Pentium 4

Принцип работы конвейера В в этом разделе мы внимательно рассмотрим принцип работы нового конвейера Pentium 4 реализован другой подход нежели в процессорах других фирм. На ступени выполнения там используется меньшее количество функциональных устройств. Но каждое из них обладает более длинным и более быстрым конвейером. Это означает, что каждое функциональное устройство имеет большее количество доступных для выполнения тактов (execution slots) и таким образом способно одновременно выполнять довольно много инструкций. Так, скажем, вместо трёх устройств для выполнения операций с плавающей точкой, работающих медленно, но параллельно, Pentium 4 имеет только одно такое устройство, которое может быстрее одновременно выполнять большее количество инструкций на различных ступенях. Важно отметить, что для того, чтобы полностью загружать быстрые конвейерные функциональные устройства в Pentium 4, препроцессор должен обладать большим буфером, способным вмещать в себя и планировать огромное количество инструкций. Процессор Pentium 4 может одновременно выполнять на различных ступенях до 126 инструкций. Отсюда следует, что для внеочередного выполнения процессор должен анализировать значительно большее количество инструкций на взаимозависимость, а затем преобразовывать их для быстрой передачи функциональным устройствам. Так работает конвейер Pentium 4

Принцип работы конвейера Для лучшего понимания сути вопроса можно обратиться к аналогии в индустрии фастфуд. В Мак. Дональдс вы можете либо прийти пешком, либо приехать. В первом случае, вы увидите шесть коротеньких очередей. Вы можете встать в любую, и подождать своей очереди, чтобы вас обслуживал один человек. Во втором случае, вы попадёте в одну большую очередь. Но очередь будет обслуживаться быстрее, так как там работает несколько человек. Первому вы сделаете заказ, а у второго вы этот заказ заберёте. Так как процесс обслуживания разбивается на несколько этапов, то большее количество посетителей смогут получить еду в одной большой очереди. Так вот, Pentium 4 использует второй вариант.

Принцип работы конвейера Для лучшего понимания сути вопроса можно обратиться к аналогии в индустрии фастфуд. В Мак. Дональдс вы можете либо прийти пешком, либо приехать. В первом случае, вы увидите шесть коротеньких очередей. Вы можете встать в любую, и подождать своей очереди, чтобы вас обслуживал один человек. Во втором случае, вы попадёте в одну большую очередь. Но очередь будет обслуживаться быстрее, так как там работает несколько человек. Первому вы сделаете заказ, а у второго вы этот заказ заберёте. Так как процесс обслуживания разбивается на несколько этапов, то большее количество посетителей смогут получить еду в одной большой очереди. Так вот, Pentium 4 использует второй вариант.

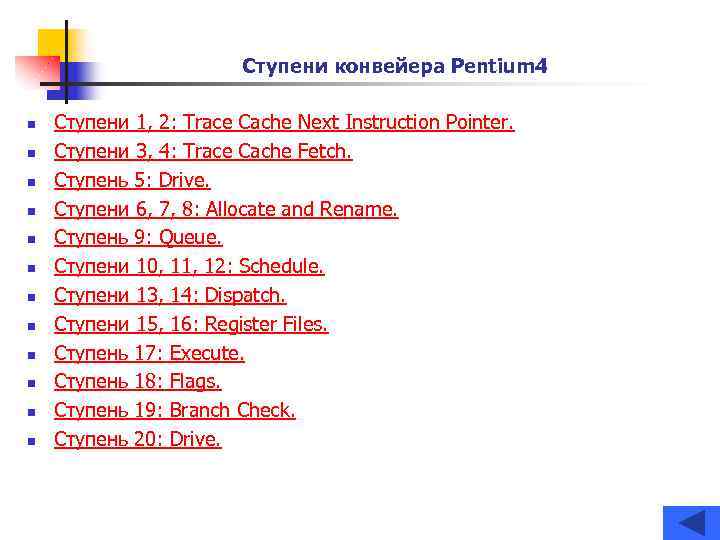

Ступени конвейера Pentium 4 n n n Ступени 1, 2: Trace Cache Next Instruction Pointer. Ступени 3, 4: Trace Cache Fetch. Ступень 5: Drive. Ступени 6, 7, 8: Allocate and Rename. Ступень 9: Queue. Ступени 10, 11, 12: Schedule. Ступени 13, 14: Dispatch. Ступени 15, 16: Register Files. Ступень 17: Execute. Ступень 18: Flags. Ступень 19: Branch Check. Ступень 20: Drive.

Ступени конвейера Pentium 4 n n n Ступени 1, 2: Trace Cache Next Instruction Pointer. Ступени 3, 4: Trace Cache Fetch. Ступень 5: Drive. Ступени 6, 7, 8: Allocate and Rename. Ступень 9: Queue. Ступени 10, 11, 12: Schedule. Ступени 13, 14: Dispatch. Ступени 15, 16: Register Files. Ступень 17: Execute. Ступень 18: Flags. Ступень 19: Branch Check. Ступень 20: Drive.

Ступени 1, 2 Отслеживающий кэш получает указатель на следующие инструкции. На этих ступенях в логику кэшпамяти передаётся указатель на следующую инструкцию в отслеживающем кэше.

Ступени 1, 2 Отслеживающий кэш получает указатель на следующие инструкции. На этих ступенях в логику кэшпамяти передаётся указатель на следующую инструкцию в отслеживающем кэше.

Ступени 3, 4 На этих двух ступенях происходит выборка инструкций из кэш-памяти. Затем эти инструкции будут отосланы на внеочередное выполнение.

Ступени 3, 4 На этих двух ступенях происходит выборка инструкций из кэш-памяти. Затем эти инструкции будут отосланы на внеочередное выполнение.

Ступень 5 Это первая из двух передаточных ступеней конвейера. Каждая из них предназначена для передачи сигналов из одной части процессора в следующую. Процессор работает настолько быстро, что иногда сигналы не могут пройти весь путь за один тактовый импульс, поэтому в Pentium® 4 выделено две ступени конвейера для передачи сигнала по чипу. Раньше эта ступень в конвейерах не встречалось. Intel® впервые внедрила эту ступень в конвейерную технологию. Без такого рода ступеней невозможно достичь высоких частот.

Ступень 5 Это первая из двух передаточных ступеней конвейера. Каждая из них предназначена для передачи сигналов из одной части процессора в следующую. Процессор работает настолько быстро, что иногда сигналы не могут пройти весь путь за один тактовый импульс, поэтому в Pentium® 4 выделено две ступени конвейера для передачи сигнала по чипу. Раньше эта ступень в конвейерах не встречалось. Intel® впервые внедрила эту ступень в конвейерную технологию. Без такого рода ступеней невозможно достичь высоких частот.

Ступени 6, 7, 8 n n На этих ступенях происходит распределение микроархитектурных ресурсов регистров. С помощью переименования регистров можно добиться бесконфликтного существования большего количества регистров в микроархитектуре, чем это определено архитектурой набора команд (ISA -Instruction Set Achitecture). Эти дополнительные регистры как раз распределяются и используются на этой стадии. В Pentium® 4 таких дополнительных регистров 128. Ступени распределения / переименования могут выпустить три микрокоманды за такт на следующую ступень конвейера.

Ступени 6, 7, 8 n n На этих ступенях происходит распределение микроархитектурных ресурсов регистров. С помощью переименования регистров можно добиться бесконфликтного существования большего количества регистров в микроархитектуре, чем это определено архитектурой набора команд (ISA -Instruction Set Achitecture). Эти дополнительные регистры как раз распределяются и используются на этой стадии. В Pentium® 4 таких дополнительных регистров 128. Ступени распределения / переименования могут выпустить три микрокоманды за такт на следующую ступень конвейера.

Ступени 10, 11, 12 На этих ступенях инструкции поступают из устройства распределения (Allocator) в одну из четырех n n очередей распределения. Далее цитата Intel®, которая подытожит функции этой ступени: "Распределитель микрокоманд (Scheduler) следит за входными регистровыми операндами (Register Operands) микрокоманд и определяет, какую из микрокоманд уже можно выполнять. Это суть внеочередного выполнения команд. Распределитель микрокоманд позволяет посылать на ступень выполнения микрокоманды как только они будут готовы (изменяя нормальных порядок) и при этом поддерживает нормальный ход программы. Микроархитектура Net. Burst™ использует два устройства, с помощью которых происходит распределение микрокоманд: сам распределитель, и очередь микрокоманд". Ниже представлены четыре распределителя: Memory Scheduler - распределитель памяти, распределяет операции по работе с памятью для устройств Load / Store Unit (LSU); Fast ALU Scheduler - быстрый распределитель арифметико-логического устройства, распределяет арифметикологические операции (простые целочисленные и логические операции), чтобы послать их потом на два ALU, работающие на двойной скорости; Slow ALU / General FPU Scheduler - медленный распределитель ALU / распределитель операций с плавающей точкой, распределяет остальные операции ALU и операции с плавающей точкой; Simple FP Scheduler, распределитель простых операций с плавающей точкой - распределяет простые операции с плавающей точкой и операции по доступу к памяти с плавающей точкой.

Ступени 10, 11, 12 На этих ступенях инструкции поступают из устройства распределения (Allocator) в одну из четырех n n очередей распределения. Далее цитата Intel®, которая подытожит функции этой ступени: "Распределитель микрокоманд (Scheduler) следит за входными регистровыми операндами (Register Operands) микрокоманд и определяет, какую из микрокоманд уже можно выполнять. Это суть внеочередного выполнения команд. Распределитель микрокоманд позволяет посылать на ступень выполнения микрокоманды как только они будут готовы (изменяя нормальных порядок) и при этом поддерживает нормальный ход программы. Микроархитектура Net. Burst™ использует два устройства, с помощью которых происходит распределение микрокоманд: сам распределитель, и очередь микрокоманд". Ниже представлены четыре распределителя: Memory Scheduler - распределитель памяти, распределяет операции по работе с памятью для устройств Load / Store Unit (LSU); Fast ALU Scheduler - быстрый распределитель арифметико-логического устройства, распределяет арифметикологические операции (простые целочисленные и логические операции), чтобы послать их потом на два ALU, работающие на двойной скорости; Slow ALU / General FPU Scheduler - медленный распределитель ALU / распределитель операций с плавающей точкой, распределяет остальные операции ALU и операции с плавающей точкой; Simple FP Scheduler, распределитель простых операций с плавающей точкой - распределяет простые операции с плавающей точкой и операции по доступу к памяти с плавающей точкой.

Ступень 9 Между ступенями распределения / переименования и распределяющей логикой существуют две очереди. Это очередь микрокоманд памяти и очередь арифметических микрокоманд. Именно в эти очереди и распределяются микрокоманды перед тем, как попасть на один из четырёх портов диспетчера, работающего в качестве шлюза к функциональным устройствам стадии выполнения.

Ступень 9 Между ступенями распределения / переименования и распределяющей логикой существуют две очереди. Это очередь микрокоманд памяти и очередь арифметических микрокоманд. Именно в эти очереди и распределяются микрокоманды перед тем, как попасть на один из четырёх портов диспетчера, работающего в качестве шлюза к функциональным устройствам стадии выполнения.

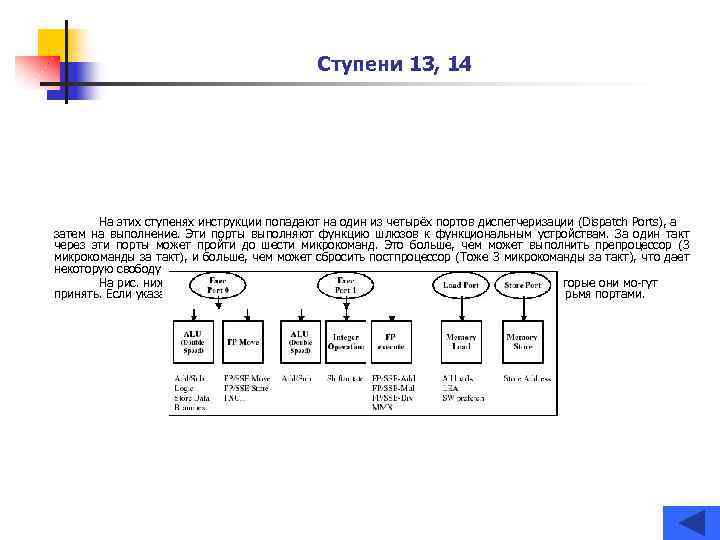

Ступени 13, 14 На этих ступенях инструкции попадают на один из четырёх портов диспетчеризации (Dispatch Ports), а затем на выполнение. Эти порты выполняют функцию шлюзов к функциональным устройствам. За один такт через эти порты может пройти до шести микрокоманд. Это больше, чем может выполнить препроцессор (3 микрокоманды за такт), и больше, чем может сбросить постпроцессор (Тоже 3 микрокоманды за такт), что дает некоторую свободу в случае вспышки активности. На рис. ниже представлены четыре порта диспетчеризации и типы инструкций, которые они мо-гут принять. Если указать на диаграмме распределители, то они были бы размещены над четырьмя портами.

Ступени 13, 14 На этих ступенях инструкции попадают на один из четырёх портов диспетчеризации (Dispatch Ports), а затем на выполнение. Эти порты выполняют функцию шлюзов к функциональным устройствам. За один такт через эти порты может пройти до шести микрокоманд. Это больше, чем может выполнить препроцессор (3 микрокоманды за такт), и больше, чем может сбросить постпроцессор (Тоже 3 микрокоманды за такт), что дает некоторую свободу в случае вспышки активности. На рис. ниже представлены четыре порта диспетчеризации и типы инструкций, которые они мо-гут принять. Если указать на диаграмме распределители, то они были бы размещены над четырьмя портами.

Ступени 15, 16 После того, как инструкции пройдут порты диспетчеризации, они попадают на две эти ступени. Здесь инструкции загружаются в блок регистров для дальнейшего выполнения.

Ступени 15, 16 После того, как инструкции пройдут порты диспетчеризации, они попадают на две эти ступени. Здесь инструкции загружаются в блок регистров для дальнейшего выполнения.

Ступень 17 На этой ступени инструкции выполняются в функциональных устройствах. Вообще говоря, это и есть самая главная стадия, ради которой и приходится проделывать весь этот длинный путь. Если это инструкция ADD, то цифры складываются, если это LOAD, то в память загружаются какие-то данные, если это MUL, то цифры перемножаются, и т. д.

Ступень 17 На этой ступени инструкции выполняются в функциональных устройствах. Вообще говоря, это и есть самая главная стадия, ради которой и приходится проделывать весь этот длинный путь. Если это инструкция ADD, то цифры складываются, если это LOAD, то в память загружаются какие-то данные, если это MUL, то цифры перемножаются, и т. д.

Ступень 18 Если результат выполнения инструкции требует изменения состоянии флагов, именно на этой ступени и выполняется эта операция.

Ступень 18 Если результат выполнения инструкции требует изменения состоянии флагов, именно на этой ступени и выполняется эта операция.

Ступень 19 На этой ступени Pentium 4 проверяет выполнение условия ветвления и определяет, напрасно были затрачены 19 тактов, или все-таки нет. Т. е. препроцессор узнает, сбылось ли предсказание ветвления.

Ступень 19 На этой ступени Pentium 4 проверяет выполнение условия ветвления и определяет, напрасно были затрачены 19 тактов, или все-таки нет. Т. е. препроцессор узнает, сбылось ли предсказание ветвления.

Ступень 20 Вторая передаточная ступень выполняет те же функции распространения сигнала по чипу, что и первая. 20 -ступенчатый конвейер Pentium® 4 выполняет ту же работу и в том же порядке, что и конвейеры других процессоров. Однако, разбиение конвейера на большее число ступеней позволяет Pentium® 4 достичь больших тактовых частот.

Ступень 20 Вторая передаточная ступень выполняет те же функции распространения сигнала по чипу, что и первая. 20 -ступенчатый конвейер Pentium® 4 выполняет ту же работу и в том же порядке, что и конвейеры других процессоров. Однако, разбиение конвейера на большее число ступеней позволяет Pentium® 4 достичь больших тактовых частот.

Advanced Dynamic Execution (Улучшенное предсказание переходов и исполнение команд с изменением порядка их следования) Целью ряда ухищрений в архитектуре Pentium 4, под общим названием Advanced Dynamic Execution, как раз и является минимизация простоя процессора при неправильном предсказании переходов и увеличение вероятности правильных предсказаний. Для этого Intel улучшил блок выборки инструкций для внеочередного выполнения и повысил правильность предсказания переходов. Правда, для этого алгоритмы предсказания переходов были доработаны минимально, основным же средством для достижения цели было выбрано увеличение размеров буферов, с которыми работают соответствующие блоки процессора. Так, для выборки следующей инструкции для исполнения используется теперь окно величиной в 126 команд против 42 команд у процессора Pentium III. Буфер же, в котором сохраняются адреса выполненных переходов и на основании которого процессор предсказывает будущие переходы, теперь увеличен до 4 Кбайт, в то время как у Pentium III его размер составлял всего 512 байт. Результатом этого, а также благодаря небольшой доработке алгоритма, вероятность правильного предсказания переходов была улучшена по сравнению с Pentium III на 33%. Это – очень хороший показатель, поскольку теперь Pentium 4 предсказывает переходы правильно в 90 -95% случаев.

Advanced Dynamic Execution (Улучшенное предсказание переходов и исполнение команд с изменением порядка их следования) Целью ряда ухищрений в архитектуре Pentium 4, под общим названием Advanced Dynamic Execution, как раз и является минимизация простоя процессора при неправильном предсказании переходов и увеличение вероятности правильных предсказаний. Для этого Intel улучшил блок выборки инструкций для внеочередного выполнения и повысил правильность предсказания переходов. Правда, для этого алгоритмы предсказания переходов были доработаны минимально, основным же средством для достижения цели было выбрано увеличение размеров буферов, с которыми работают соответствующие блоки процессора. Так, для выборки следующей инструкции для исполнения используется теперь окно величиной в 126 команд против 42 команд у процессора Pentium III. Буфер же, в котором сохраняются адреса выполненных переходов и на основании которого процессор предсказывает будущие переходы, теперь увеличен до 4 Кбайт, в то время как у Pentium III его размер составлял всего 512 байт. Результатом этого, а также благодаря небольшой доработке алгоритма, вероятность правильного предсказания переходов была улучшена по сравнению с Pentium III на 33%. Это – очень хороший показатель, поскольку теперь Pentium 4 предсказывает переходы правильно в 90 -95% случаев.

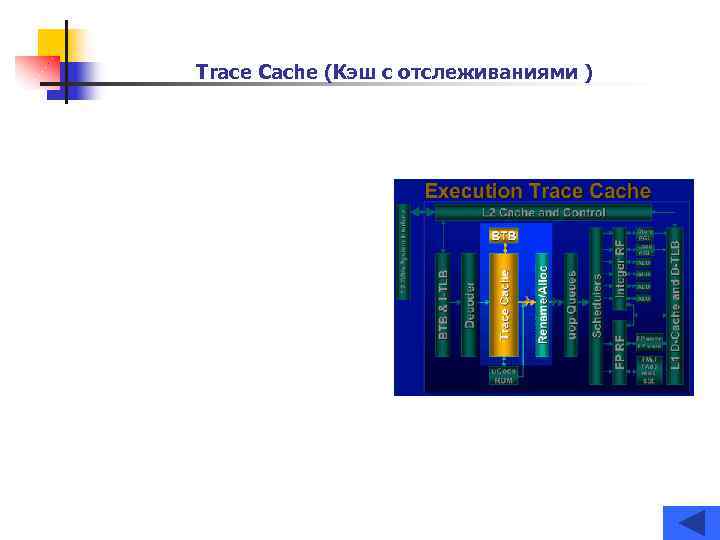

Trace Cache (Кэш с отслеживаниями )

Trace Cache (Кэш с отслеживаниями )

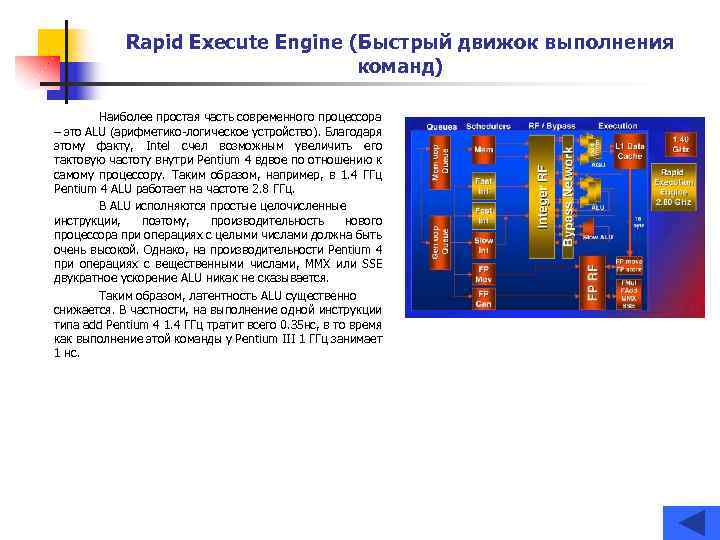

Rapid Execute Engine (Быстрый движок выполнения команд) Наиболее простая часть современного процессора – это ALU (арифметико-логическое устройство). Благодаря этому факту, Intel счел возможным увеличить его тактовую частоту внутри Pentium 4 вдвое по отношению к самому процессору. Таким образом, например, в 1. 4 ГГц Pentium 4 ALU работает на частоте 2. 8 ГГц. В ALU исполняются простые целочисленные инструкции, поэтому, производительность нового процессора при операциях с целыми числами должна быть очень высокой. Однако, на производительности Pentium 4 при операциях с вещественными числами, MMX или SSE двукратное ускорение ALU никак не сказывается. Таким образом, латентность ALU существенно снижается. В частности, на выполнение одной инструкции типа add Pentium 4 1. 4 ГГц тратит всего 0. 35 нс, в то время как выполнение этой команды у Pentium III 1 ГГц занимает 1 нс.

Rapid Execute Engine (Быстрый движок выполнения команд) Наиболее простая часть современного процессора – это ALU (арифметико-логическое устройство). Благодаря этому факту, Intel счел возможным увеличить его тактовую частоту внутри Pentium 4 вдвое по отношению к самому процессору. Таким образом, например, в 1. 4 ГГц Pentium 4 ALU работает на частоте 2. 8 ГГц. В ALU исполняются простые целочисленные инструкции, поэтому, производительность нового процессора при операциях с целыми числами должна быть очень высокой. Однако, на производительности Pentium 4 при операциях с вещественными числами, MMX или SSE двукратное ускорение ALU никак не сказывается. Таким образом, латентность ALU существенно снижается. В частности, на выполнение одной инструкции типа add Pentium 4 1. 4 ГГц тратит всего 0. 35 нс, в то время как выполнение этой команды у Pentium III 1 ГГц занимает 1 нс.

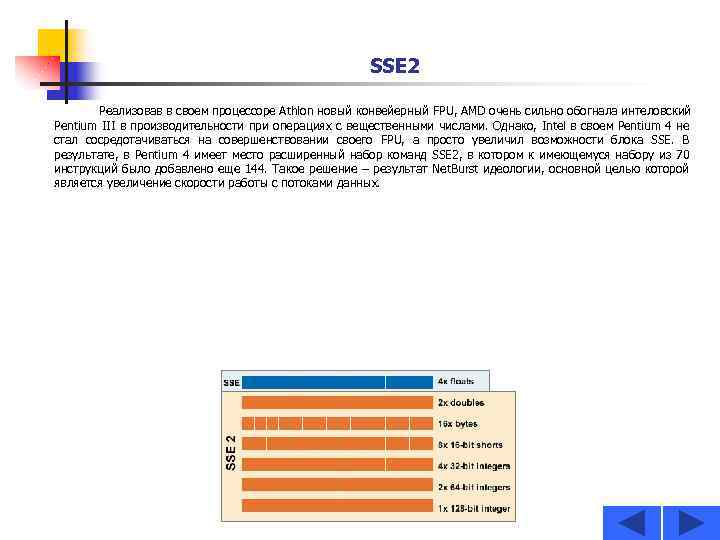

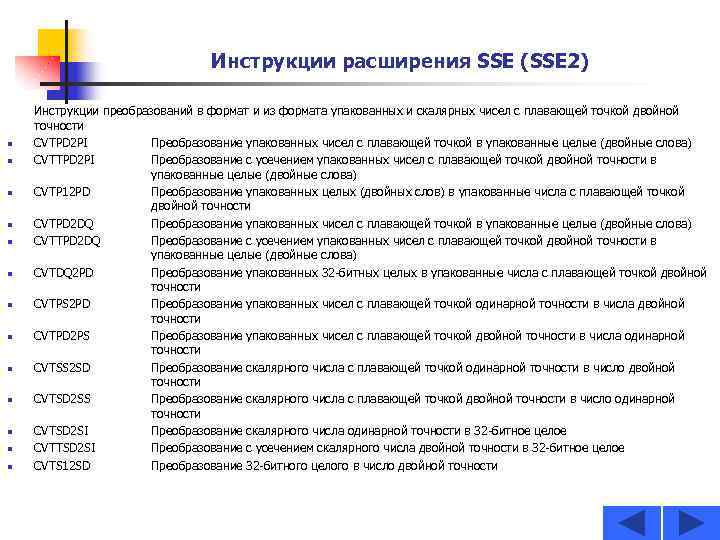

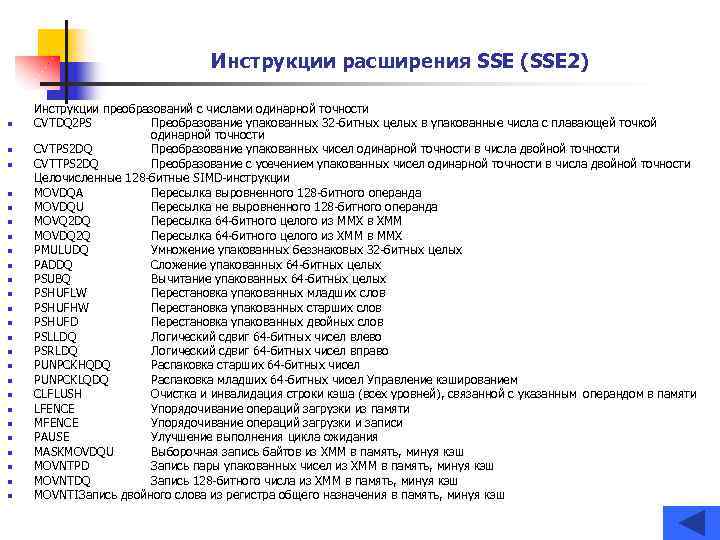

SSE 2 Реализовав в своем процессоре Athlon новый конвейерный FPU, AMD очень сильно обогнала интеловский Pentium III в производительности при операциях с вещественными числами. Однако, Intel в своем Pentium 4 не стал сосредотачиваться на совершенствовании своего FPU, а просто увеличил возможности блока SSE. В результате, в Pentium 4 имеет место расширенный набор команд SSE 2, в котором к имеющемуся набору из 70 инструкций было добавлено еще 144. Такое решение – результат Net. Burst идеологии, основной целью которой является увеличение скорости работы с потоками данных.

SSE 2 Реализовав в своем процессоре Athlon новый конвейерный FPU, AMD очень сильно обогнала интеловский Pentium III в производительности при операциях с вещественными числами. Однако, Intel в своем Pentium 4 не стал сосредотачиваться на совершенствовании своего FPU, а просто увеличил возможности блока SSE. В результате, в Pentium 4 имеет место расширенный набор команд SSE 2, в котором к имеющемуся набору из 70 инструкций было добавлено еще 144. Такое решение – результат Net. Burst идеологии, основной целью которой является увеличение скорости работы с потоками данных.

SSE 2 Таким образом, SSE 2 гораздо более гибок, позволяя добиваться впечатляющего прироста в производительности. Однако, использование нового набора команд требует специальной оптимизации программ, поэтому ждать его внедрения сразу после выхода нового процессора не стоит. Со временем же, SSE 2 имеет достаточно большие перспективы. Поэтому, даже AMD собирается реализовать SSE 2 в своем новом семействе процессоров Hammer. Старые же программы, не использующие SSE 2, а полагающиеся на обычный арифметический сопроцессор, никакого прироста в производительности при использовании Pentium 4 не получат. Более того, несмотря на то, что Intel говорит о том, что блок FPU в Pentium 4 был слегка усовершенствован, время, необходимое на выполнение обычных операций с вещественными числами возросло по сравнению с Pentium III в среднем на 2 такта.

SSE 2 Таким образом, SSE 2 гораздо более гибок, позволяя добиваться впечатляющего прироста в производительности. Однако, использование нового набора команд требует специальной оптимизации программ, поэтому ждать его внедрения сразу после выхода нового процессора не стоит. Со временем же, SSE 2 имеет достаточно большие перспективы. Поэтому, даже AMD собирается реализовать SSE 2 в своем новом семействе процессоров Hammer. Старые же программы, не использующие SSE 2, а полагающиеся на обычный арифметический сопроцессор, никакого прироста в производительности при использовании Pentium 4 не получат. Более того, несмотря на то, что Intel говорит о том, что блок FPU в Pentium 4 был слегка усовершенствован, время, необходимое на выполнение обычных операций с вещественными числами возросло по сравнению с Pentium III в среднем на 2 такта.

L 1 кэш Что касается кеша первого уровня в Pentium 4, то поскольку теперь команды хранятся в Trace Cache, он предназначен только для хранения данных. Однако, его размер в Pentium 4, основанном на ядре Willamette составляет всего 8 Кбайт. Это выглядит достаточно небольшой цифрой даже на фоне 16 -килобайтной области данных в L 1 кэше Pentium III. Однако, Intel был вынужден сократить объем кеша первого уровня в Pentium 4, так как ядро этого процессора и без того получалось слишком большим. Тем не менее, архитектура этого процессора может поддерживать L 1 -кеш и большего размера, поэтому, скорее всего, при переходе на технологический процесс 0. 13 мкм и новое ядро Northwood, этот кэш будет увеличен. Однако, для увеличения производительности, Intel применил для доступа к L 1 -кешу новый алгоритм, чем уменьшил в Pentium 4 латентность этого кеша до двух процессорных тактов вместо трех тактов в Pentium III. Таким образом, учитывая большую тактовую частоту Pentium 4, время реакции его L 1 кеша составляет всего 1. 4 нс для 1. 4 ГГц модели против 3 нс у L 1 кеша Pentium III 1 ГГц. Также как и в Pentium III, L 1 кэш Pentium 4 является write through и ассоциативным с 4 областями ассоциативности. При этом длина одной строки L 1 кеша равна 64 байтам.

L 1 кэш Что касается кеша первого уровня в Pentium 4, то поскольку теперь команды хранятся в Trace Cache, он предназначен только для хранения данных. Однако, его размер в Pentium 4, основанном на ядре Willamette составляет всего 8 Кбайт. Это выглядит достаточно небольшой цифрой даже на фоне 16 -килобайтной области данных в L 1 кэше Pentium III. Однако, Intel был вынужден сократить объем кеша первого уровня в Pentium 4, так как ядро этого процессора и без того получалось слишком большим. Тем не менее, архитектура этого процессора может поддерживать L 1 -кеш и большего размера, поэтому, скорее всего, при переходе на технологический процесс 0. 13 мкм и новое ядро Northwood, этот кэш будет увеличен. Однако, для увеличения производительности, Intel применил для доступа к L 1 -кешу новый алгоритм, чем уменьшил в Pentium 4 латентность этого кеша до двух процессорных тактов вместо трех тактов в Pentium III. Таким образом, учитывая большую тактовую частоту Pentium 4, время реакции его L 1 кеша составляет всего 1. 4 нс для 1. 4 ГГц модели против 3 нс у L 1 кеша Pentium III 1 ГГц. Также как и в Pentium III, L 1 кэш Pentium 4 является write through и ассоциативным с 4 областями ассоциативности. При этом длина одной строки L 1 кеша равна 64 байтам.

L 2 Advanced Transfer Cache Процессор Pentium 4 обладает Advanced Transfer Cache второго уровня объемом 256 -512 Кбайт. Также, как и в Pentium III, L 2 -кеш имеет широкую 256 -битную шину, благодаря которой процессоры от Intel имеют более высокую пропускную способность кеша, чем их конкуренты от AMD, использующие 64 -битную шину кеша. Однако, в отличие от Athlon, в Pentium 4 (впрочем, также как и в Pentium III) L 2 кэш не является эксклюзивным, то есть он дублирует данные, находящиеся в L 1 кэше. Так как Pentium 4 рассчитан на обработку потоковых данных, скорость работы L 2 -кеша для него является одним из ключевых моментов. Поэтому, Intel увеличил пропускную способность кеша второго уровня в Pentium 4 в два раза. Это усовершенствование было сделано благодаря передаче данных из L 2 -кеша на каждый процессорный такт, в то время, как данные из L 2 -кеша Pentium III передаются только на каждый второй такт. Таким образом, пропускная способность L 2 -кеша Pentium 4, работающего, например, с частотой 1. 4 ГГц имеет теперь внушительную величину 44. 8 Гбайт/с. Для сравнения – пропускная способность Advanced Transfer Cache у Pentium III 1 ГГц составляет 16 Гбайт/с. Также как и в Pentium III, L 2 кэш имеет восемь областей ассоциативности и строки длиной 128 байт. Однако, в отличие от Pentium III, каждая строка может быть изъята не целиком, а по 64 -байтовым половинкам. Говоря о системе кэширования в Pentium 4, нельзя обойти стороной и тот факт, что архитектура Net. Burst поддерживает и кэш третьего уровня размером до 4 Мбайт. Однако, в Pentium 4 пока эта возможность использоваться не будет. Она зарезервирована для будущего применения в серверных процессорах.

L 2 Advanced Transfer Cache Процессор Pentium 4 обладает Advanced Transfer Cache второго уровня объемом 256 -512 Кбайт. Также, как и в Pentium III, L 2 -кеш имеет широкую 256 -битную шину, благодаря которой процессоры от Intel имеют более высокую пропускную способность кеша, чем их конкуренты от AMD, использующие 64 -битную шину кеша. Однако, в отличие от Athlon, в Pentium 4 (впрочем, также как и в Pentium III) L 2 кэш не является эксклюзивным, то есть он дублирует данные, находящиеся в L 1 кэше. Так как Pentium 4 рассчитан на обработку потоковых данных, скорость работы L 2 -кеша для него является одним из ключевых моментов. Поэтому, Intel увеличил пропускную способность кеша второго уровня в Pentium 4 в два раза. Это усовершенствование было сделано благодаря передаче данных из L 2 -кеша на каждый процессорный такт, в то время, как данные из L 2 -кеша Pentium III передаются только на каждый второй такт. Таким образом, пропускная способность L 2 -кеша Pentium 4, работающего, например, с частотой 1. 4 ГГц имеет теперь внушительную величину 44. 8 Гбайт/с. Для сравнения – пропускная способность Advanced Transfer Cache у Pentium III 1 ГГц составляет 16 Гбайт/с. Также как и в Pentium III, L 2 кэш имеет восемь областей ассоциативности и строки длиной 128 байт. Однако, в отличие от Pentium III, каждая строка может быть изъята не целиком, а по 64 -байтовым половинкам. Говоря о системе кэширования в Pentium 4, нельзя обойти стороной и тот факт, что архитектура Net. Burst поддерживает и кэш третьего уровня размером до 4 Мбайт. Однако, в Pentium 4 пока эта возможность использоваться не будет. Она зарезервирована для будущего применения в серверных процессорах.

Процессор n n n n Итак, после краткого знакомства с основными деталями Net. Burst архитектуры, основного оружия Pentium 4 взглянем на его формальную спецификацию: Чип, производимый технологии по 0. 18 -0. 13 с мкм использованием алюминиевых соединений. Переход на медные соединения Intel планирует произвести одновременно с внедрением технологии 0. 13 мкм. архитектуре Net. Burst. Содержит 42 млн. транзисторов и имеет площадь 217 кв. мм. Это более чем в два раза больше, чем площадь ядра Athlon или Pentium III. Работает в специальных материнских платах с 478 контактным процессорным разъемом Socket 478. Использует высокопроизводительную 400/533/667 МГц Quad Pumped системную шину Кеш данных первого Кбайт. Cache уровня Trace 8 для декодированных инструкций рассчитан на 12000 микроопераций второго уровня размером 256 -512 Кбайт. Работает на полной частоте ядра и имеет 256 -битную шину Напряжение питания - 1. 7 В Набор SIMD-инструкций SSE 2

Процессор n n n n Итак, после краткого знакомства с основными деталями Net. Burst архитектуры, основного оружия Pentium 4 взглянем на его формальную спецификацию: Чип, производимый технологии по 0. 18 -0. 13 с мкм использованием алюминиевых соединений. Переход на медные соединения Intel планирует произвести одновременно с внедрением технологии 0. 13 мкм. архитектуре Net. Burst. Содержит 42 млн. транзисторов и имеет площадь 217 кв. мм. Это более чем в два раза больше, чем площадь ядра Athlon или Pentium III. Работает в специальных материнских платах с 478 контактным процессорным разъемом Socket 478. Использует высокопроизводительную 400/533/667 МГц Quad Pumped системную шину Кеш данных первого Кбайт. Cache уровня Trace 8 для декодированных инструкций рассчитан на 12000 микроопераций второго уровня размером 256 -512 Кбайт. Работает на полной частоте ядра и имеет 256 -битную шину Напряжение питания - 1. 7 В Набор SIMD-инструкций SSE 2

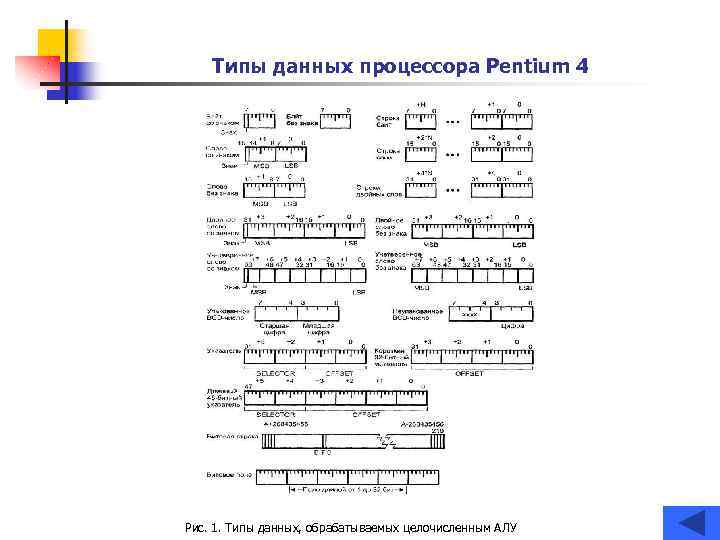

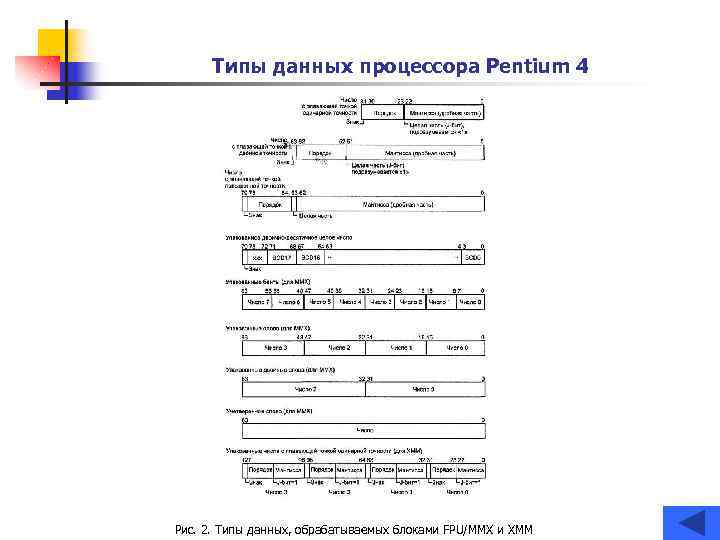

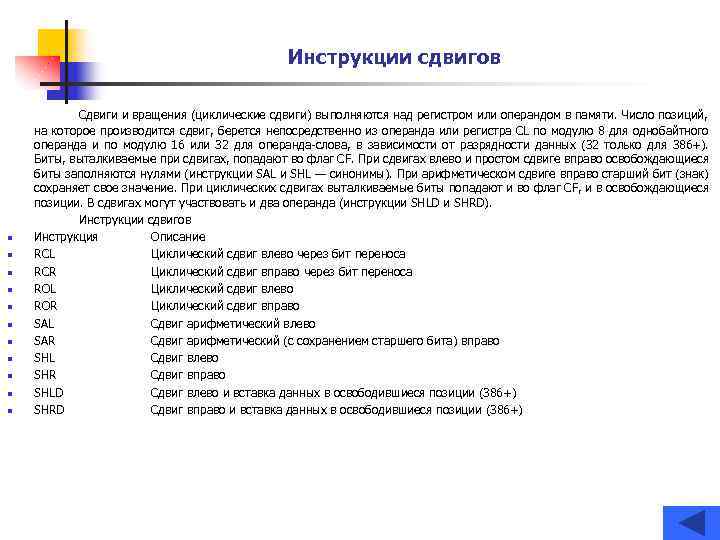

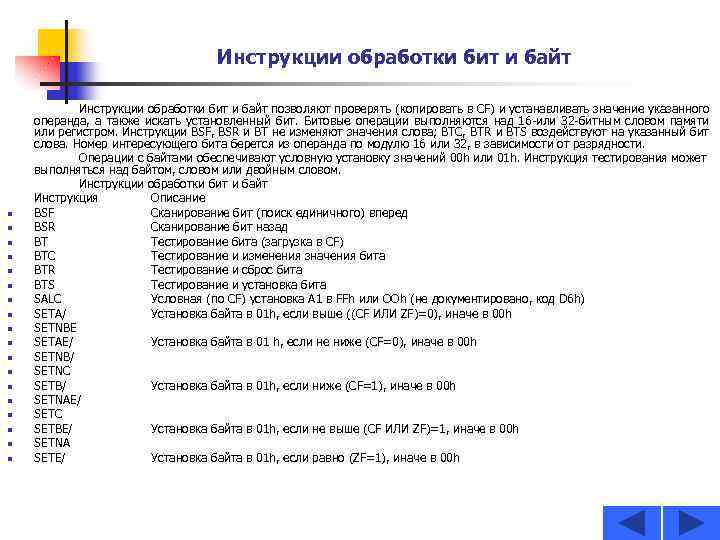

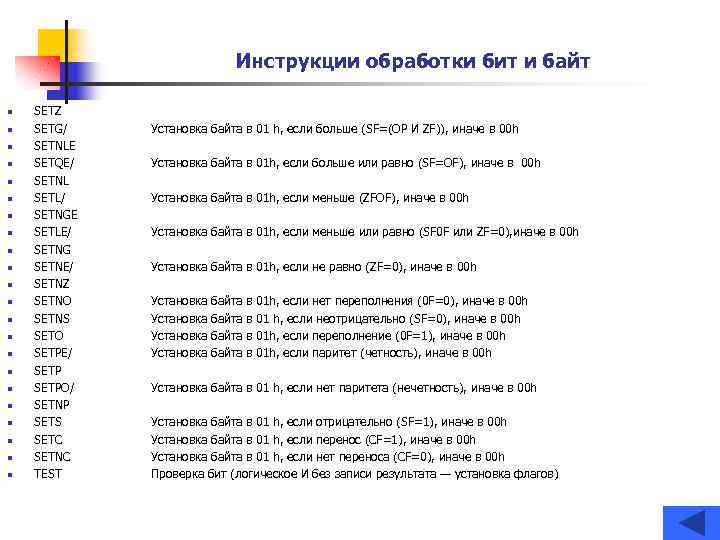

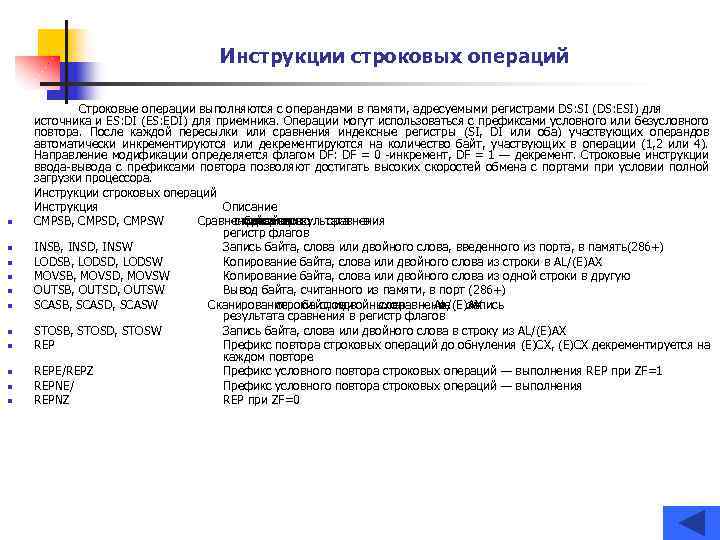

Форматы данных и команды их обработки процессора Intel Pentium 4 n n n Типы данных процессора Pentium 4 Рис. 1. Типы данных Рис. 2. Типы данных, обрабатываемых блоками FPU/MMX и ХММ Математический сопроцессор x 87 Технология MMX Расширение SSE и SSE 2 — блок XMM Команды обработки данных n Инструкции пересылки данных n Инструкции двоичной арифметики n Инструкции десятичной арифметики n Инструкции логических операций n Инструкции сдвигов n Инструкции обработки бит и байт n Инструкции строковых операций n Инструкции FPU n Инструкции ММХ n Инструкции расширения SSE 2

Форматы данных и команды их обработки процессора Intel Pentium 4 n n n Типы данных процессора Pentium 4 Рис. 1. Типы данных Рис. 2. Типы данных, обрабатываемых блоками FPU/MMX и ХММ Математический сопроцессор x 87 Технология MMX Расширение SSE и SSE 2 — блок XMM Команды обработки данных n Инструкции пересылки данных n Инструкции двоичной арифметики n Инструкции десятичной арифметики n Инструкции логических операций n Инструкции сдвигов n Инструкции обработки бит и байт n Инструкции строковых операций n Инструкции FPU n Инструкции ММХ n Инструкции расширения SSE 2

Типы данных процессора Pentium 4 История 32 -разрядных процессоров Intel началась с процессора Intel 386. Он вобрал в себя все черты своих 16 - n n n разрядных предшественников 8086/88 и 80286 для обеспечения совместимости с громадным объемом программного обеспечения, существовавшего на момент его появления. Процессоры могут оперировать с 8 -, 16 - и 32 -битными операндами, строками байт, слов и двойных слов, а также с битами, битовыми полями и строками бит. Рассматриваемые процессоры непосредственно поддерживают (используют в качестве операндов) знаковые и беззнаковые целые числа, строки байт, цифр и символов, битовые строки, указатели и числа с плавающей точкой. В семействе х86 принято, что слова записываются в двух смежных байтах памяти, начиная с младшего. Адресом слова является адрес его младшего байта. Двойные слова записываются в четырех смежных байтах, опять-таки начиная с младшего байта, адрес которого и является адресом двойного слова. Этот порядок называется Little-Endian Memory Format. В других семействах процессоров применяют и обратный порядок — Big-Endian Memory Format, в котором адресом слова (двойного слова) является адрес его старшего байта, а младшие байты располагаются в последующих адресах. Для взаимного преобразования форматов слова имеется инструкция XCHG, двойного слова — BSWAP (процессор 486 и выше). Типы данных: Бит (Bit) — единица информации. Бит в памяти задается базой (адресом слова) и смещением (номером бита в слове). Битовое поле (Bit Field) — группа до 32 смежных бит, располагающихся не более чем в 4 байтах. Битовая строка (Bit String) — набор смежных бит длиной до 4 Гбит. Байт (Byte) — 8 бит. Числа без знака: байт/слово/двойное/учетверенное слово (Unsigned Byte/ Word/Double Word/Quade Word), 8/16/32/64 бит. Целые числа со знаком: байт/слово/двойное/учетверенное слово (Integer Byte/ Word/Double Word/Quade Word). Единичное значение самого старшего бита (знак) является признаком отрицательного числа, которое хранится в дополнительном коде.

Типы данных процессора Pentium 4 История 32 -разрядных процессоров Intel началась с процессора Intel 386. Он вобрал в себя все черты своих 16 - n n n разрядных предшественников 8086/88 и 80286 для обеспечения совместимости с громадным объемом программного обеспечения, существовавшего на момент его появления. Процессоры могут оперировать с 8 -, 16 - и 32 -битными операндами, строками байт, слов и двойных слов, а также с битами, битовыми полями и строками бит. Рассматриваемые процессоры непосредственно поддерживают (используют в качестве операндов) знаковые и беззнаковые целые числа, строки байт, цифр и символов, битовые строки, указатели и числа с плавающей точкой. В семействе х86 принято, что слова записываются в двух смежных байтах памяти, начиная с младшего. Адресом слова является адрес его младшего байта. Двойные слова записываются в четырех смежных байтах, опять-таки начиная с младшего байта, адрес которого и является адресом двойного слова. Этот порядок называется Little-Endian Memory Format. В других семействах процессоров применяют и обратный порядок — Big-Endian Memory Format, в котором адресом слова (двойного слова) является адрес его старшего байта, а младшие байты располагаются в последующих адресах. Для взаимного преобразования форматов слова имеется инструкция XCHG, двойного слова — BSWAP (процессор 486 и выше). Типы данных: Бит (Bit) — единица информации. Бит в памяти задается базой (адресом слова) и смещением (номером бита в слове). Битовое поле (Bit Field) — группа до 32 смежных бит, располагающихся не более чем в 4 байтах. Битовая строка (Bit String) — набор смежных бит длиной до 4 Гбит. Байт (Byte) — 8 бит. Числа без знака: байт/слово/двойное/учетверенное слово (Unsigned Byte/ Word/Double Word/Quade Word), 8/16/32/64 бит. Целые числа со знаком: байт/слово/двойное/учетверенное слово (Integer Byte/ Word/Double Word/Quade Word). Единичное значение самого старшего бита (знак) является признаком отрицательного числа, которое хранится в дополнительном коде.

Типы данных процессора Pentium 4 n n n n n Двоично-десятичные числа (BCD — Binary Coded Decimal): 8 -разрядные упакованные (Packed BCD), содержащие два десятичных разряда в одном байте; 8 -разрядные неупакованные (Unpacked BCD), содержащие один десятичный разряд в байте (значение бит 7: 4 при сложении и вычитании несущественно, при умножении и делении они должны быть нулевыми). Строки байт, слов и двойных слов (Bit String, Byte String, Word String, Double Word String) длиной до 4 Гбайт. Указатели: длинный указатель (48 бит) — 16 -битный селектор (или сегмент) и 32 -битное смещение; короткий указатель — 32 -битное смещение; просто указатель (32 бит, единственный тип указателя для 8086 и 80286) • 16 -битный селектор (или сегмент) и 16 битное смещение. 16 -разрядные процессоры из приведенных типов данных не поддерживают учетверенные слова всех типов, битовые поля и строки, строки двойных слов, короткие и длинные указатели. Числа в формате с плавающей точкой и упакованные 80 -битные BCD-числа обрабатываются блоками FPU процессоров класса 486 и выше, а также сопроцессорами 8087/287/387. Упакованные 64 -битные и 128 -битные данные обрабатываются процессорами с ММХ и SSE. Форматы данных, обрабатываемых блоками FPU/MMX и ХММ Действительные числа в формате с плавающей точкой: n n n одинарной точности (Single Precision), 32 бит — 23 бит мантисса, 8 бит порядок; двойной точности (Double Precision), 64 бит — 52 бит мантисса, 11 бит порядок; повышенной точности (Extended Precision), 80 бит — 64 бит мантисса, 15 бит порядок. Двоично-десятичные 80 -битные упакованные числа (18 десятичных разрядов и знак). Упакованные действительные числа одинарной точности в формате с плавающей точкой, обрабатываются блоком ХММ. Упакованные целые числа, знаковые и беззнаковые, обрабатываются блоком ММХ:

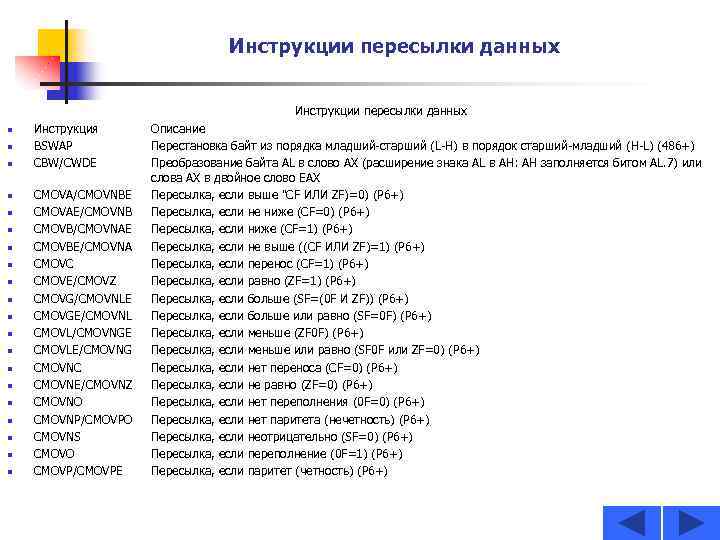

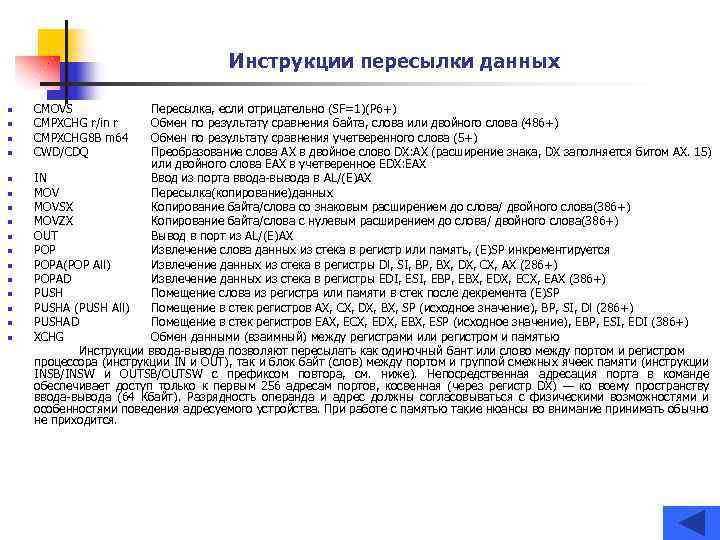

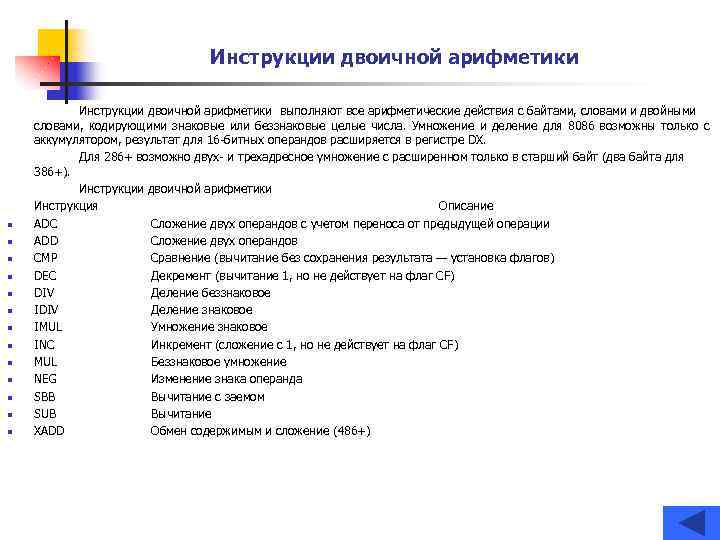

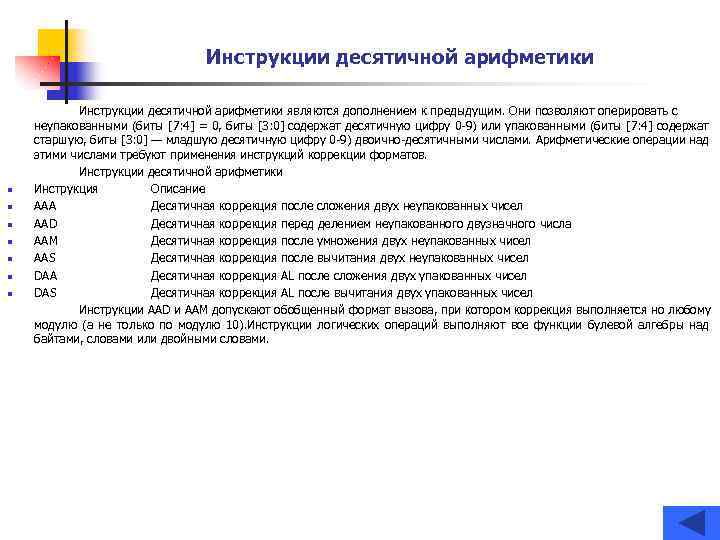

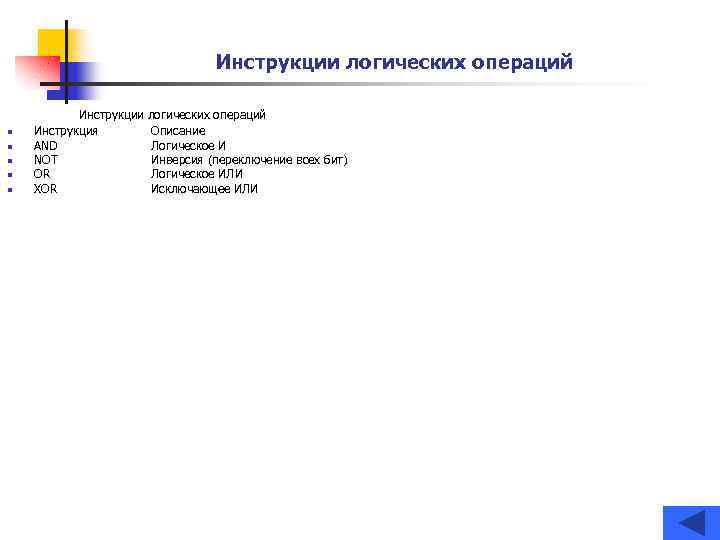

Типы данных процессора Pentium 4 n n n n n Двоично-десятичные числа (BCD — Binary Coded Decimal): 8 -разрядные упакованные (Packed BCD), содержащие два десятичных разряда в одном байте; 8 -разрядные неупакованные (Unpacked BCD), содержащие один десятичный разряд в байте (значение бит 7: 4 при сложении и вычитании несущественно, при умножении и делении они должны быть нулевыми). Строки байт, слов и двойных слов (Bit String, Byte String, Word String, Double Word String) длиной до 4 Гбайт. Указатели: длинный указатель (48 бит) — 16 -битный селектор (или сегмент) и 32 -битное смещение; короткий указатель — 32 -битное смещение; просто указатель (32 бит, единственный тип указателя для 8086 и 80286) • 16 -битный селектор (или сегмент) и 16 битное смещение. 16 -разрядные процессоры из приведенных типов данных не поддерживают учетверенные слова всех типов, битовые поля и строки, строки двойных слов, короткие и длинные указатели. Числа в формате с плавающей точкой и упакованные 80 -битные BCD-числа обрабатываются блоками FPU процессоров класса 486 и выше, а также сопроцессорами 8087/287/387. Упакованные 64 -битные и 128 -битные данные обрабатываются процессорами с ММХ и SSE. Форматы данных, обрабатываемых блоками FPU/MMX и ХММ Действительные числа в формате с плавающей точкой: n n n одинарной точности (Single Precision), 32 бит — 23 бит мантисса, 8 бит порядок; двойной точности (Double Precision), 64 бит — 52 бит мантисса, 11 бит порядок; повышенной точности (Extended Precision), 80 бит — 64 бит мантисса, 15 бит порядок. Двоично-десятичные 80 -битные упакованные числа (18 десятичных разрядов и знак). Упакованные действительные числа одинарной точности в формате с плавающей точкой, обрабатываются блоком ХММ. Упакованные целые числа, знаковые и беззнаковые, обрабатываются блоком ММХ: