14. 1 АРХИТЕКТУРА 32 -х РАЗРЯДНЫХ МИКРОПРОЦЕССОРОВ Базовая

4.1_arhitektura_32-razryadnyh_mikroprocessorov.pptx

- Размер: 952.4 Кб

- Автор:

- Количество слайдов: 20

Описание презентации 14. 1 АРХИТЕКТУРА 32 -х РАЗРЯДНЫХ МИКРОПРОЦЕССОРОВ Базовая по слайдам

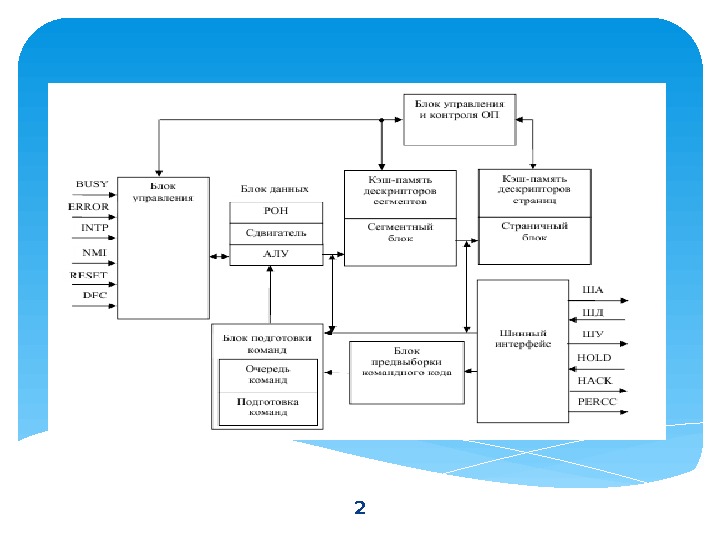

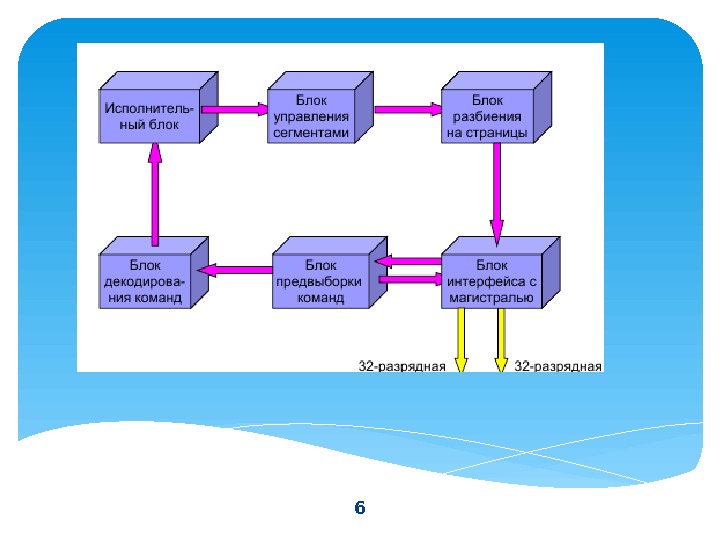

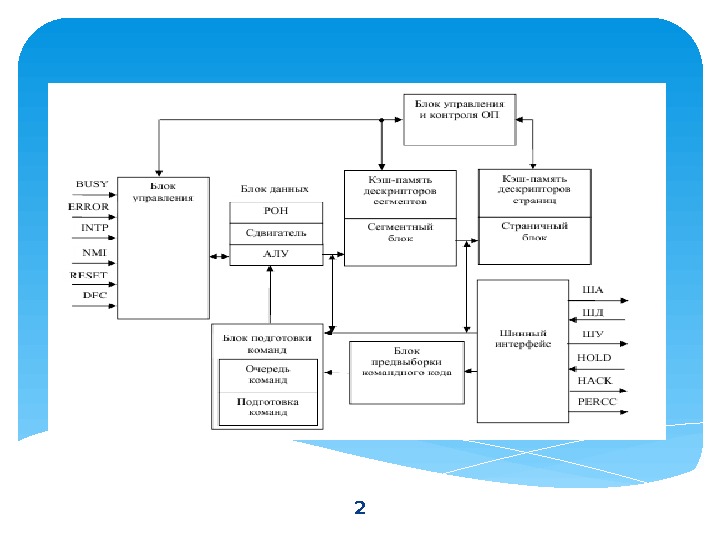

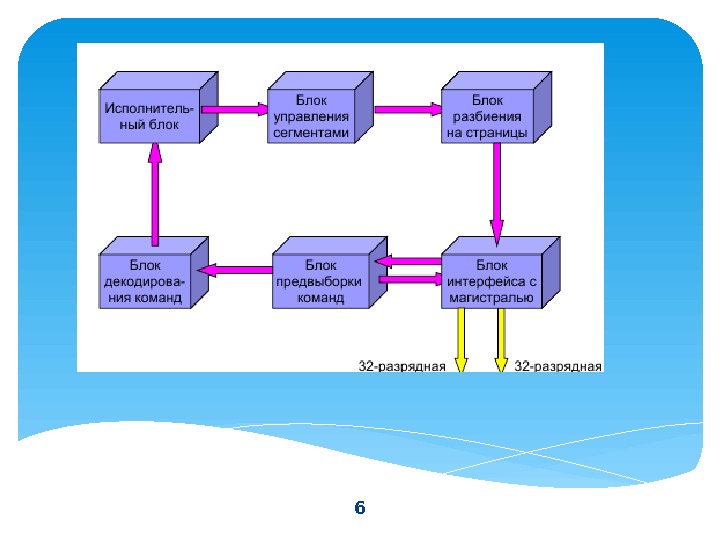

14. 1 АРХИТЕКТУРА 32 -х РАЗРЯДНЫХ МИКРОПРОЦЕССОРОВ Базовая архитектура 32 -х разрядных процессоров (обозначаемых: 386+) является общей для существующих на данный момент процессоров фирмы INTEL – 386, 486, PENTIUM и его модификаций. МП состоит из 3 основных частей: устройства обработки; устройства управления ЗУ; интерфейсного блока.

14. 1 АРХИТЕКТУРА 32 -х РАЗРЯДНЫХ МИКРОПРОЦЕССОРОВ Базовая архитектура 32 -х разрядных процессоров (обозначаемых: 386+) является общей для существующих на данный момент процессоров фирмы INTEL – 386, 486, PENTIUM и его модификаций. МП состоит из 3 основных частей: устройства обработки; устройства управления ЗУ; интерфейсного блока.

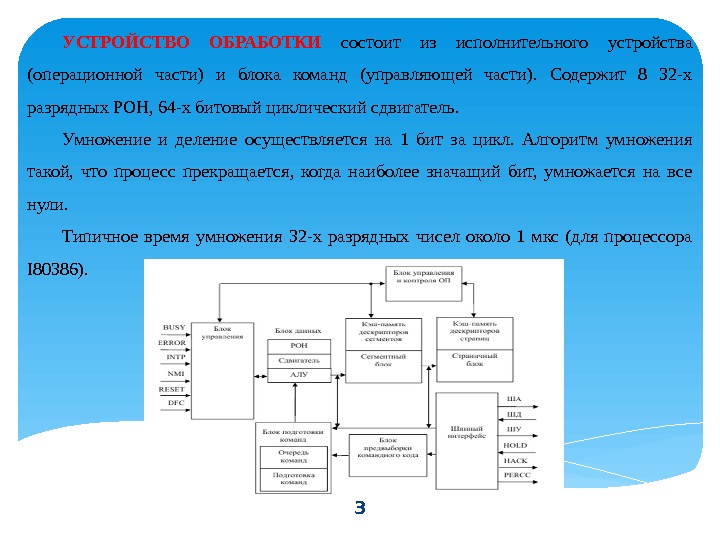

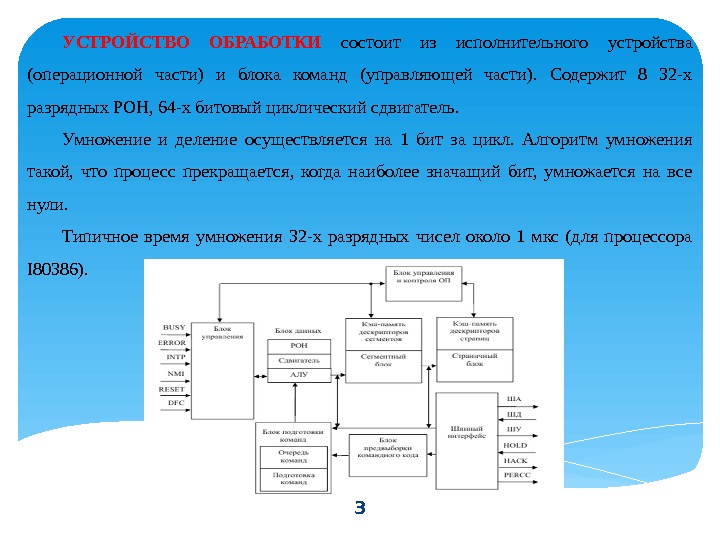

3 УСТРОЙСТВО ОБРАБОТКИ состоит из исполнительного устройства (операционной части) и блока команд (управляющей части). Содержит 8 32 -х разрядных РОН, 64 -х битовый циклический сдвигатель. Умножение и деление осуществляется на 1 бит за цикл. Алгоритм умножения такой, что процесс прекращается, когда наиболее значащий бит, умножается на все нули. Типичное время умножения 32 -х разрядных чисел около 1 мкс (для процессора I 80386).

3 УСТРОЙСТВО ОБРАБОТКИ состоит из исполнительного устройства (операционной части) и блока команд (управляющей части). Содержит 8 32 -х разрядных РОН, 64 -х битовый циклический сдвигатель. Умножение и деление осуществляется на 1 бит за цикл. Алгоритм умножения такой, что процесс прекращается, когда наиболее значащий бит, умножается на все нули. Типичное время умножения 32 -х разрядных чисел около 1 мкс (для процессора I 80386).

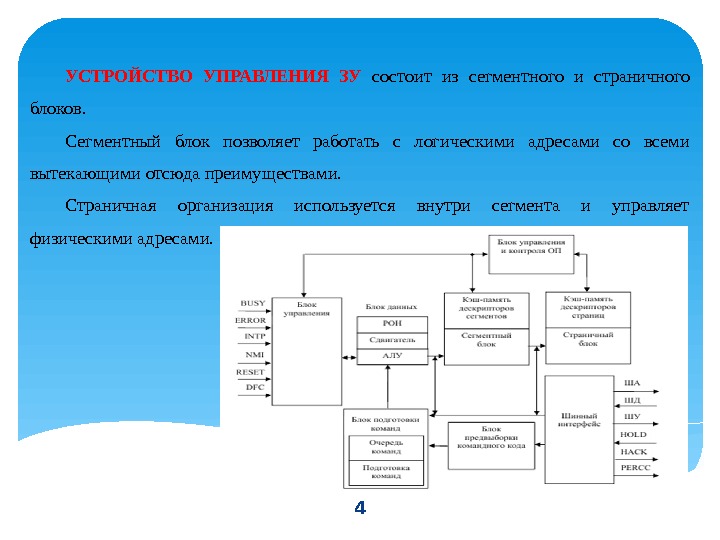

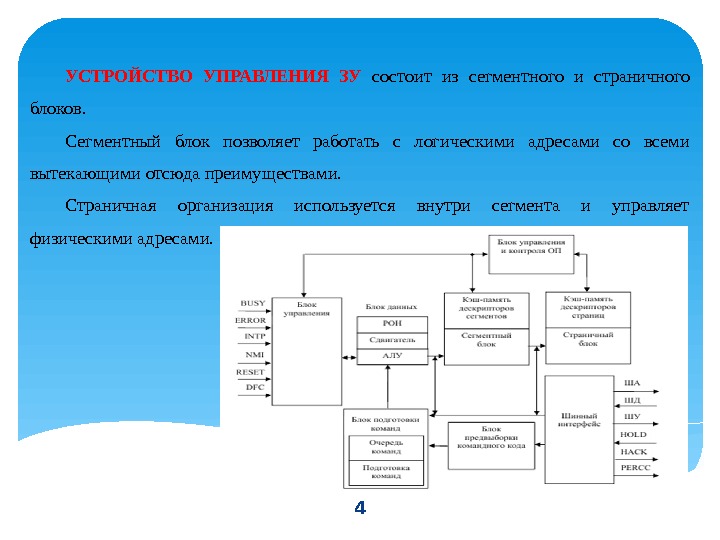

4 УСТРОЙСТВО УПРАВЛЕНИЯ ЗУ состоит из сегментного и страничного блоков. Сегментный блок позволяет работать с логическими адресами со всеми вытекающими отсюда преимуществами. Страничная организация используется внутри сегмента и управляет физическими адресами.

4 УСТРОЙСТВО УПРАВЛЕНИЯ ЗУ состоит из сегментного и страничного блоков. Сегментный блок позволяет работать с логическими адресами со всеми вытекающими отсюда преимуществами. Страничная организация используется внутри сегмента и управляет физическими адресами.

5 ИНТЕРФЕЙСНЫЙ БЛОК обеспечивает взаимодействие с внешними устройствами, включая автоматическое управление разрядностью шины, и формирование сигналов активности байтов.

5 ИНТЕРФЕЙСНЫЙ БЛОК обеспечивает взаимодействие с внешними устройствами, включая автоматическое управление разрядностью шины, и формирование сигналов активности байтов.

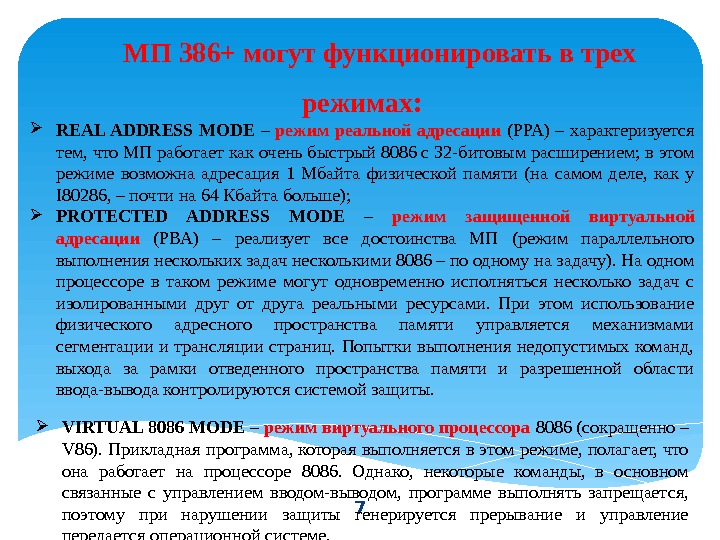

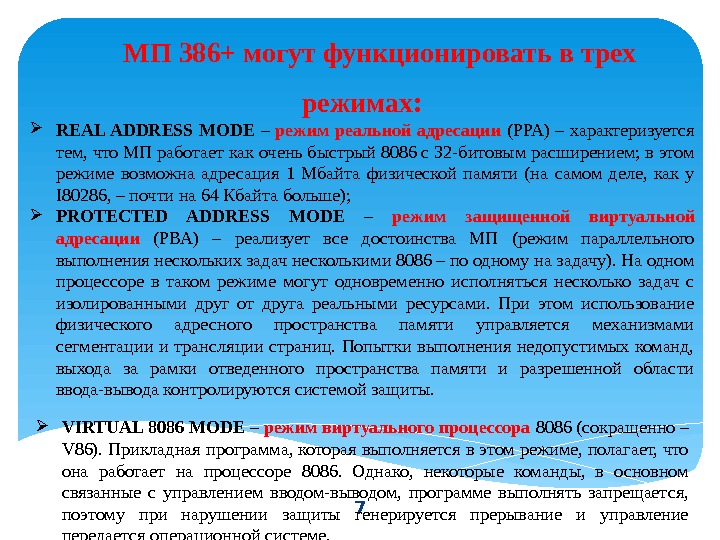

7 МП 386+ могут функционировать в трех режимах: REAL ADDRESS MODE – режим реальной адресации (РРА) – характеризуется тем, что МП работает как очень быстрый 8086 с 32 -битовым расширением; в этом режиме возможна адресация 1 Мбайта физической памяти (на самом деле, как у I 80286, – почти на 64 Кбайта больше); PROTECTED ADDRESS MODE – режим защищенной виртуальной адресации (РВА) – реализует все достоинства МП (режим параллельного выполнения нескольких задач несколькими 8086 – по одному на задачу). На одном процессоре в таком режиме могут одновременно исполняться несколько задач с изолированными друг от друга реальными ресурсами. При этом использование физического адресного пространства памяти управляется механизмами сегментации и трансляции страниц. Попытки выполнения недопустимых команд, выхода за рамки отведенного пространства памяти и разрешенной области ввода-вывода контролируются системой защиты. VIRTUAL 8086 MODE – режим виртуального процессора 8086 (сокращенно – V 86). Прикладная программа, которая выполняется в этом режиме, полагает, что она работает на процессоре 8086. Однако, некоторые команды, в основном связанные с управлением вводом-выводом, программе выполнять запрещается, поэтому при нарушении защиты генерируется прерывание и управление передается операционной системе.

7 МП 386+ могут функционировать в трех режимах: REAL ADDRESS MODE – режим реальной адресации (РРА) – характеризуется тем, что МП работает как очень быстрый 8086 с 32 -битовым расширением; в этом режиме возможна адресация 1 Мбайта физической памяти (на самом деле, как у I 80286, – почти на 64 Кбайта больше); PROTECTED ADDRESS MODE – режим защищенной виртуальной адресации (РВА) – реализует все достоинства МП (режим параллельного выполнения нескольких задач несколькими 8086 – по одному на задачу). На одном процессоре в таком режиме могут одновременно исполняться несколько задач с изолированными друг от друга реальными ресурсами. При этом использование физического адресного пространства памяти управляется механизмами сегментации и трансляции страниц. Попытки выполнения недопустимых команд, выхода за рамки отведенного пространства памяти и разрешенной области ввода-вывода контролируются системой защиты. VIRTUAL 8086 MODE – режим виртуального процессора 8086 (сокращенно – V 86). Прикладная программа, которая выполняется в этом режиме, полагает, что она работает на процессоре 8086. Однако, некоторые команды, в основном связанные с управлением вводом-выводом, программе выполнять запрещается, поэтому при нарушении защиты генерируется прерывание и управление передается операционной системе.

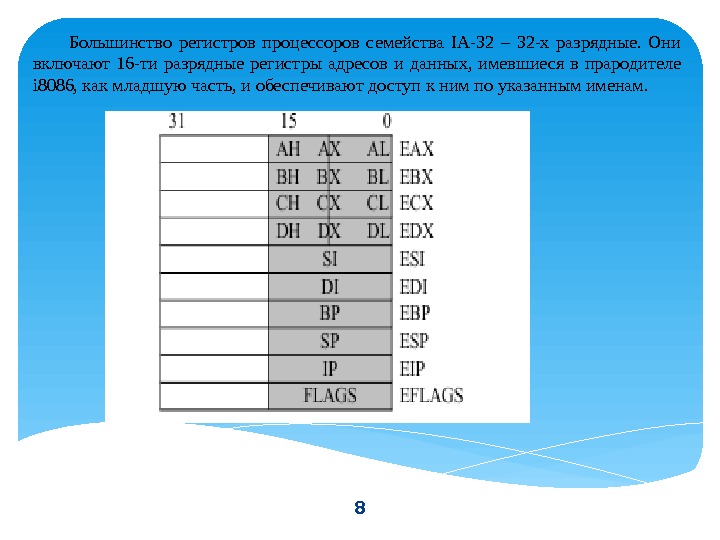

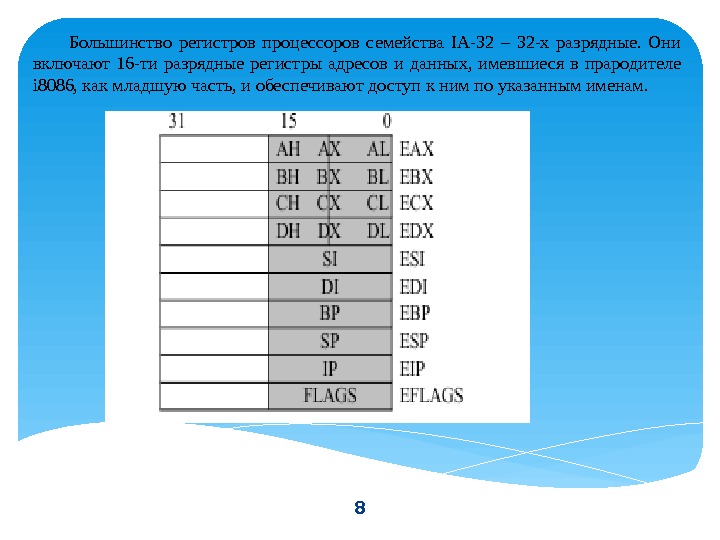

8 Большинство регистров процессоров семейства IA-32 – 32 -х разрядные. Они включают 16 -ти разрядные регистры адресов и данных, имевшиеся в прародителе i 8086, как младшую часть, и обеспечивают доступ к ним по указанным именам.

8 Большинство регистров процессоров семейства IA-32 – 32 -х разрядные. Они включают 16 -ти разрядные регистры адресов и данных, имевшиеся в прародителе i 8086, как младшую часть, и обеспечивают доступ к ним по указанным именам.

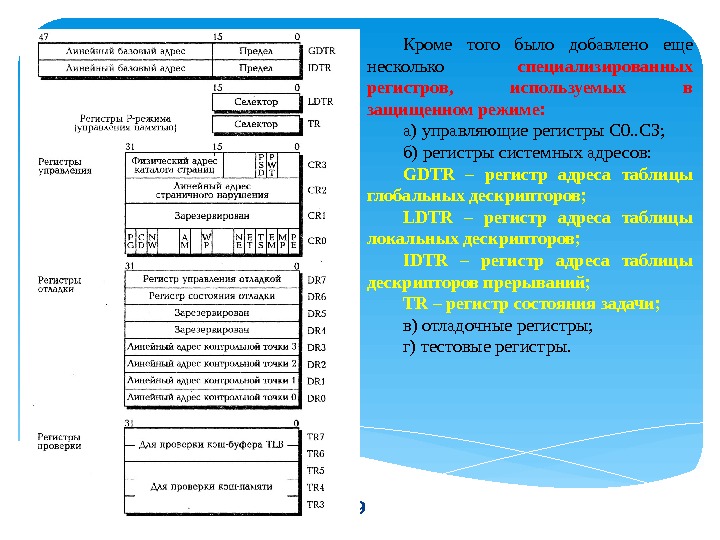

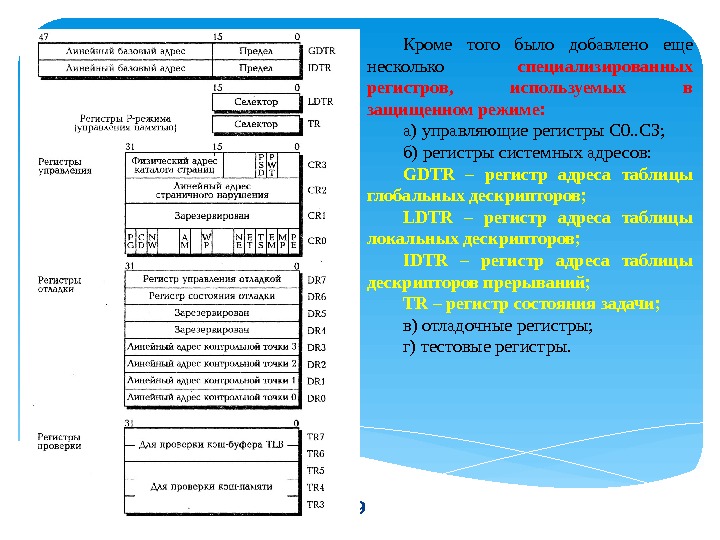

9 Кроме того было добавлено еще несколько специализированных регистров, используемых в защищенном режиме: а) управляющие регистры С 0. . С 3; б) регистры системных адресов: GDTR – регистр адреса таблицы глобальных дескрипторов; LDTR – регистр адреса таблицы локальных дескрипторов; IDTR – регистр адреса таблицы дескрипторов прерываний; TR – регистр состояния задачи; в) отладочные регистры; г) тестовые регистры.

9 Кроме того было добавлено еще несколько специализированных регистров, используемых в защищенном режиме: а) управляющие регистры С 0. . С 3; б) регистры системных адресов: GDTR – регистр адреса таблицы глобальных дескрипторов; LDTR – регистр адреса таблицы локальных дескрипторов; IDTR – регистр адреса таблицы дескрипторов прерываний; TR – регистр состояния задачи; в) отладочные регистры; г) тестовые регистры.

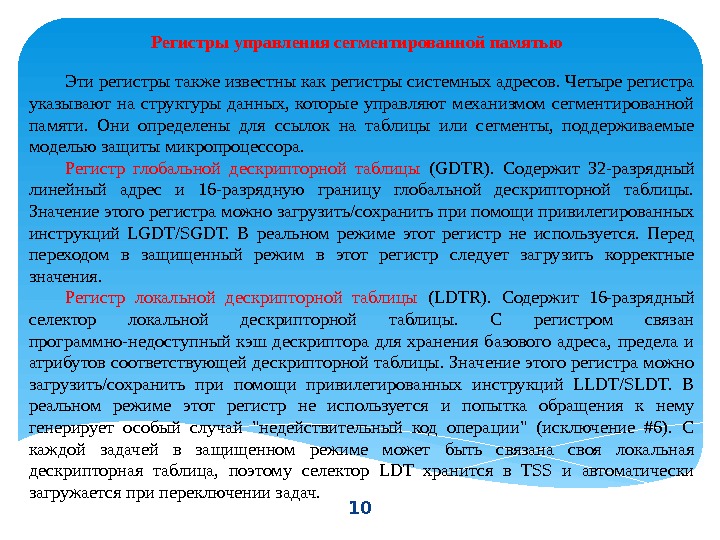

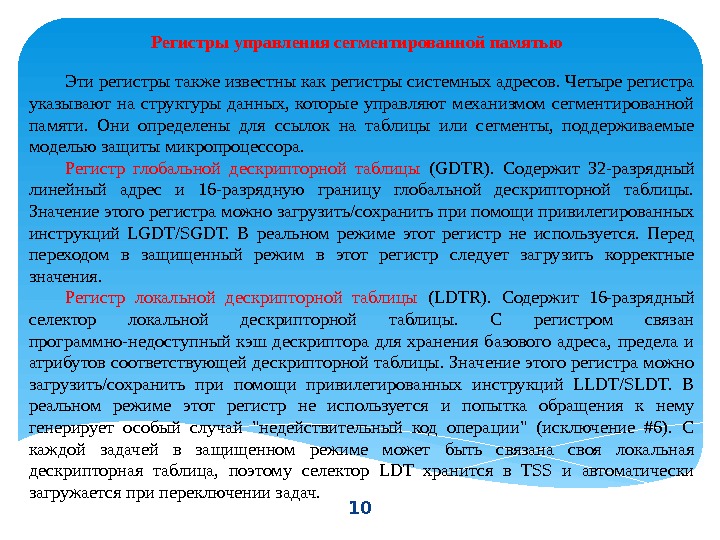

10 Регистры управления сегментированной памятью Эти регистры также известны как регистры системных адресов. Четыре регистра указывают на структуры данных, которые управляют механизмом сегментированной памяти. Они определены для ссылок на таблицы или сегменты, поддерживаемые моделью защиты микропроцессора. Регистр глобальной дескрипторной таблицы (GDTR). Содержит 32 -разрядный линейный адрес и 16 -разрядную границу глобальной дескрипторной таблицы. Значение этого регистра можно загрузить/сохранить при помощи привилегированных инструкций LGDT/SGDT. В реальном режиме этот регистр не используется. Перед переходом в защищенный режим в этот регистр следует загрузить корректные значения. Регистр локальной дескрипторной таблицы (LDTR). Содержит 16 -разрядный селектор локальной дескрипторной таблицы. С регистром связан программно-недоступный кэш дескриптора для хранения базового адреса, предела и атрибутов соответствующей дескрипторной таблицы. Значение этого регистра можно загрузить/сохранить при помощи привилегированных инструкций LLDT/SLDT. В реальном режиме этот регистр не используется и попытка обращения к нему генерирует особый случай «недействительный код операции» (исключение #6). С каждой задачей в защищенном режиме может быть связана своя локальная дескрипторная таблица, поэтому селектор LDT хранится в TSS и автоматически загружается при переключении задач.

10 Регистры управления сегментированной памятью Эти регистры также известны как регистры системных адресов. Четыре регистра указывают на структуры данных, которые управляют механизмом сегментированной памяти. Они определены для ссылок на таблицы или сегменты, поддерживаемые моделью защиты микропроцессора. Регистр глобальной дескрипторной таблицы (GDTR). Содержит 32 -разрядный линейный адрес и 16 -разрядную границу глобальной дескрипторной таблицы. Значение этого регистра можно загрузить/сохранить при помощи привилегированных инструкций LGDT/SGDT. В реальном режиме этот регистр не используется. Перед переходом в защищенный режим в этот регистр следует загрузить корректные значения. Регистр локальной дескрипторной таблицы (LDTR). Содержит 16 -разрядный селектор локальной дескрипторной таблицы. С регистром связан программно-недоступный кэш дескриптора для хранения базового адреса, предела и атрибутов соответствующей дескрипторной таблицы. Значение этого регистра можно загрузить/сохранить при помощи привилегированных инструкций LLDT/SLDT. В реальном режиме этот регистр не используется и попытка обращения к нему генерирует особый случай «недействительный код операции» (исключение #6). С каждой задачей в защищенном режиме может быть связана своя локальная дескрипторная таблица, поэтому селектор LDT хранится в TSS и автоматически загружается при переключении задач.

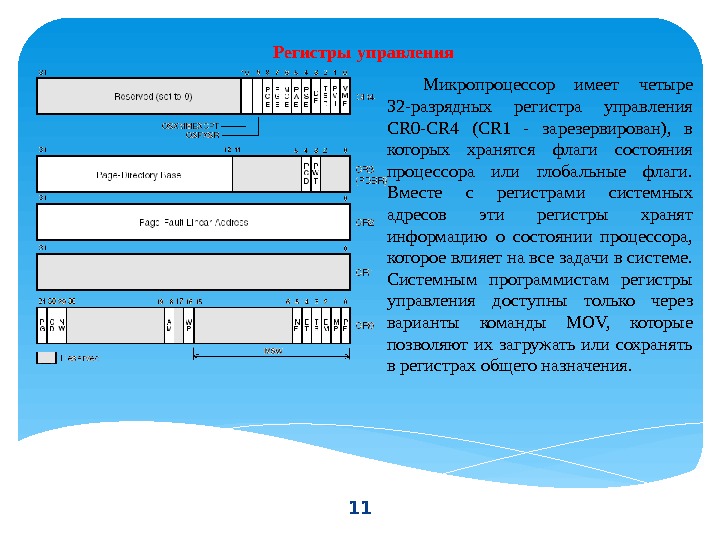

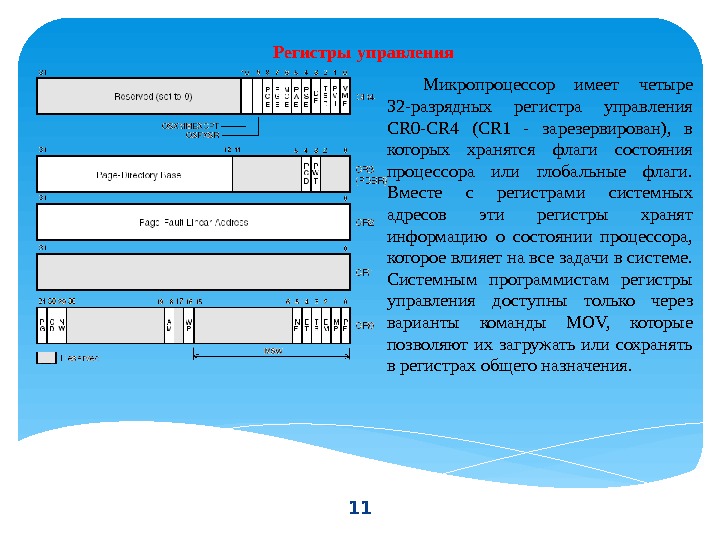

11 Регистры управления Микропроцессор имеет четыре 32 -разрядных регистра управления CR 0 -CR 4 (CR 1 — зарезервирован), в которых хранятся флаги состояния процессора или глобальные флаги. Вместе с регистрами системных адресов эти регистры хранят информацию о состоянии процессора, которое влияет на все задачи в системе. Системным программистам регистры управления доступны только через варианты команды MOV, которые позволяют их загружать или сохранять в регистрах общего назначения.

11 Регистры управления Микропроцессор имеет четыре 32 -разрядных регистра управления CR 0 -CR 4 (CR 1 — зарезервирован), в которых хранятся флаги состояния процессора или глобальные флаги. Вместе с регистрами системных адресов эти регистры хранят информацию о состоянии процессора, которое влияет на все задачи в системе. Системным программистам регистры управления доступны только через варианты команды MOV, которые позволяют их загружать или сохранять в регистрах общего назначения.

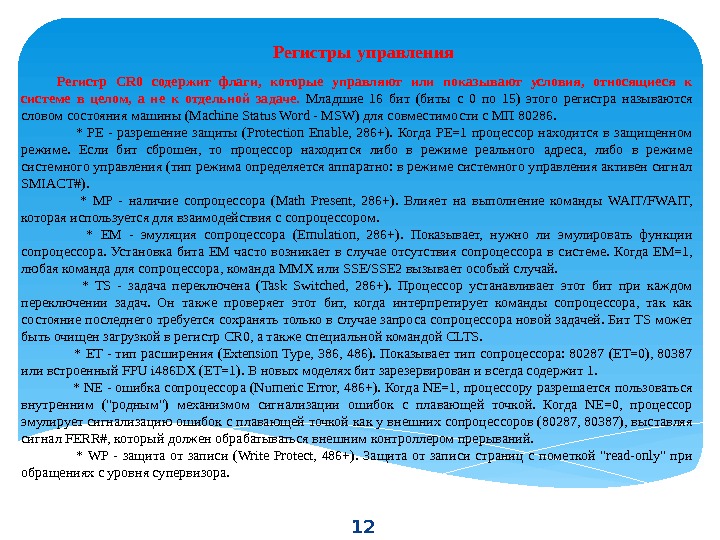

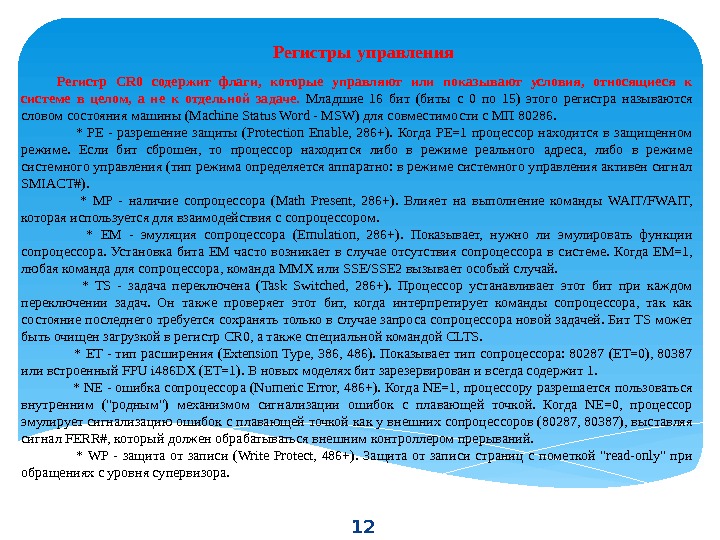

12 Регистры управления Регистр CR 0 содержит флаги, которые управляют или показывают условия, относящиеся к системе в целом, а не к отдельной задаче. Младшие 16 бит (биты с 0 по 15) этого регистра называются словом состояния машины (Machine Status Word — MSW) для совместимости с МП 80286. * PE — разрешение защиты (Protection Enable, 286+). Когда PE=1 процессор находится в защищенном режиме. Если бит сброшен, то процессор находится либо в режиме реального адреса, либо в режиме системного управления (тип режима определяется аппаратно: в режиме системного управления активен сигнал SMIACT#). * MP — наличие сопроцессора (Math Present, 286+). Влияет на выполнение команды WAIT/FWAIT, которая используется для взаимодействия с сопроцессором. * EM — эмуляция сопроцессора (Emulation, 286+). Показывает, нужно ли эмулировать функции сопроцессора. Установка бита EM часто возникает в случае отсутствия сопроцессора в системе. Когда EM=1, любая команда для сопроцессора, команда MMX или SSE/SSE 2 вызывает особый случай. * TS — задача переключена (Task Switched, 286+). Процессор устанавливает этот бит при каждом переключении задач. Он также проверяет этот бит, когда интерпретирует команды сопроцессора, так как состояние последнего требуется сохранять только в случае запроса сопроцессора новой задачей. Бит TS может быть очищен загрузкой в регистр CR 0, а также специальной командой CLTS. * ET — тип расширения (Extension Type, 386, 486). Показывает тип сопроцессора: 80287 (ET=0), 80387 или встроенный FPU i 486 DX (ET=1). В новых моделях бит зарезервирован и всегда содержит 1. * NE — ошибка сопроцессора (Numeric Error, 486+). Когда NE=1, процессору разрешается пользоваться внутренним («родным») механизмом сигнализации ошибок с плавающей точкой. Когда NE=0, процессор эмулирует сигнализацию ошибок с плавающей точкой как у внешних сопроцессоров (80287, 80387), выставляя сигнал FERR#, который должен обрабатываться внешним контроллером прерываний. * WP — защита от записи (Write Protect, 486+). Защита от записи страниц с пометкой «read-only» при обращениях с уровня супервизора.

12 Регистры управления Регистр CR 0 содержит флаги, которые управляют или показывают условия, относящиеся к системе в целом, а не к отдельной задаче. Младшие 16 бит (биты с 0 по 15) этого регистра называются словом состояния машины (Machine Status Word — MSW) для совместимости с МП 80286. * PE — разрешение защиты (Protection Enable, 286+). Когда PE=1 процессор находится в защищенном режиме. Если бит сброшен, то процессор находится либо в режиме реального адреса, либо в режиме системного управления (тип режима определяется аппаратно: в режиме системного управления активен сигнал SMIACT#). * MP — наличие сопроцессора (Math Present, 286+). Влияет на выполнение команды WAIT/FWAIT, которая используется для взаимодействия с сопроцессором. * EM — эмуляция сопроцессора (Emulation, 286+). Показывает, нужно ли эмулировать функции сопроцессора. Установка бита EM часто возникает в случае отсутствия сопроцессора в системе. Когда EM=1, любая команда для сопроцессора, команда MMX или SSE/SSE 2 вызывает особый случай. * TS — задача переключена (Task Switched, 286+). Процессор устанавливает этот бит при каждом переключении задач. Он также проверяет этот бит, когда интерпретирует команды сопроцессора, так как состояние последнего требуется сохранять только в случае запроса сопроцессора новой задачей. Бит TS может быть очищен загрузкой в регистр CR 0, а также специальной командой CLTS. * ET — тип расширения (Extension Type, 386, 486). Показывает тип сопроцессора: 80287 (ET=0), 80387 или встроенный FPU i 486 DX (ET=1). В новых моделях бит зарезервирован и всегда содержит 1. * NE — ошибка сопроцессора (Numeric Error, 486+). Когда NE=1, процессору разрешается пользоваться внутренним («родным») механизмом сигнализации ошибок с плавающей точкой. Когда NE=0, процессор эмулирует сигнализацию ошибок с плавающей точкой как у внешних сопроцессоров (80287, 80387), выставляя сигнал FERR#, который должен обрабатываться внешним контроллером прерываний. * WP — защита от записи (Write Protect, 486+). Защита от записи страниц с пометкой «read-only» при обращениях с уровня супервизора.

13 Регистры управления * AM — маска выравнивания (Alignment Mask, 486+). Если CR 0. AM=1 и EFLAGS. AC=1 и CR 0. PE=1 и CPL=3, то производится контроль выравнивания. Т. е. при обращениях к памяти двойное слово обязательно должно начинаться с адреса, кратного 4, а 16 -битное слово — с адреса, кратного 2, иначе генерируется нарушение контроля выравнивания (исключение #17). * NW — несквозная запись (Not Write-through, 486+). Используется для управления кэшированием. * CD — запрещение кэш-памяти (Cache Disable, 486+). Используется для управления кэшированием. * PG — страничная трансляция (Paging, 386+). Определяет, использует ли микропроцессор таблицы страниц для трансляции линейных адресов в физические. Страничная трансляция используется только в защищенном режиме, и попытка выставить этот бит в реальном режиме приводит к нарушению общей защиты (исключение #13) Регистр CR 2 используется для обработки страничного нарушения, если установлен бит PG в регистре CR 0. В регистре CR 2 процессор сохраняет тот линейный адрес, который вызвал исключение. Код ошибки, запоминаемый при возникновении отказа в стеке обработчика страничного нарушения, обеспечивает дополнительную информацию о состоянии при этом исключении.

13 Регистры управления * AM — маска выравнивания (Alignment Mask, 486+). Если CR 0. AM=1 и EFLAGS. AC=1 и CR 0. PE=1 и CPL=3, то производится контроль выравнивания. Т. е. при обращениях к памяти двойное слово обязательно должно начинаться с адреса, кратного 4, а 16 -битное слово — с адреса, кратного 2, иначе генерируется нарушение контроля выравнивания (исключение #17). * NW — несквозная запись (Not Write-through, 486+). Используется для управления кэшированием. * CD — запрещение кэш-памяти (Cache Disable, 486+). Используется для управления кэшированием. * PG — страничная трансляция (Paging, 386+). Определяет, использует ли микропроцессор таблицы страниц для трансляции линейных адресов в физические. Страничная трансляция используется только в защищенном режиме, и попытка выставить этот бит в реальном режиме приводит к нарушению общей защиты (исключение #13) Регистр CR 2 используется для обработки страничного нарушения, если установлен бит PG в регистре CR 0. В регистре CR 2 процессор сохраняет тот линейный адрес, который вызвал исключение. Код ошибки, запоминаемый при возникновении отказа в стеке обработчика страничного нарушения, обеспечивает дополнительную информацию о состоянии при этом исключении.

14 Регистры управления Регистр CR 3 используется, когда установлен бит PG в регистре CR 0. Этот регистр известен также как регистр каталога таблиц страниц (Page Directory Base Register — PDBR) Он позволяет процессору определить место расположения каталога таблиц страниц для текущей задачи. В старших 10 битах он содержит физический базовый адрес каталога таблиц страниц. Каталог таблиц страниц микропроцессора всегда выравнивается на размер страницы в 4 Кбайт. Специальное назначение имеют биты 3 и 4, управляющие кэшированием страницы, на которой находится каталог таблиц: * PWT — сквозная запись страницы (Page Write-Through, 486+); * PCD — запрещение кэширования страницы (Page-Cache Disable, 486+). Регистр CR 4 управляет использованием тех или иных архитектурных расширений процессоров Pentium и более новых. Какими возможностями обладает процессор, можно узнать по результатам выполнения команды CPUID(1). * VME — расширение виртуального режима (Virtual-8086 Mode Extensions, Pentium+). Разрешает расширения обработки прерываний и особых случаев в состоянии VM 86. VME позволяют задаче в состоянии VM 86 самостоятельно обрабатывать прерывания и особые случаи, не переключаясь в защищенный режим. VME обеспечивают аппаратную поддержку виртуального флага прерываний (VIF). * PVI — поддержка виртуального флага прерываний (Protected-mode Virtual Interrupts, Pentium+). Разрешает аппаратную поддержку VIF. * TSD — запрещение счетчика времени (Time Stamp Disable, Pentium+). Когда TSD=1, выполнение инструкции RDTSC (чтение внутреннего счетчика времени) ограничивается нулевым уровнем привилегий, иначе инструкция разрешена на всех уровнях.

14 Регистры управления Регистр CR 3 используется, когда установлен бит PG в регистре CR 0. Этот регистр известен также как регистр каталога таблиц страниц (Page Directory Base Register — PDBR) Он позволяет процессору определить место расположения каталога таблиц страниц для текущей задачи. В старших 10 битах он содержит физический базовый адрес каталога таблиц страниц. Каталог таблиц страниц микропроцессора всегда выравнивается на размер страницы в 4 Кбайт. Специальное назначение имеют биты 3 и 4, управляющие кэшированием страницы, на которой находится каталог таблиц: * PWT — сквозная запись страницы (Page Write-Through, 486+); * PCD — запрещение кэширования страницы (Page-Cache Disable, 486+). Регистр CR 4 управляет использованием тех или иных архитектурных расширений процессоров Pentium и более новых. Какими возможностями обладает процессор, можно узнать по результатам выполнения команды CPUID(1). * VME — расширение виртуального режима (Virtual-8086 Mode Extensions, Pentium+). Разрешает расширения обработки прерываний и особых случаев в состоянии VM 86. VME позволяют задаче в состоянии VM 86 самостоятельно обрабатывать прерывания и особые случаи, не переключаясь в защищенный режим. VME обеспечивают аппаратную поддержку виртуального флага прерываний (VIF). * PVI — поддержка виртуального флага прерываний (Protected-mode Virtual Interrupts, Pentium+). Разрешает аппаратную поддержку VIF. * TSD — запрещение счетчика времени (Time Stamp Disable, Pentium+). Когда TSD=1, выполнение инструкции RDTSC (чтение внутреннего счетчика времени) ограничивается нулевым уровнем привилегий, иначе инструкция разрешена на всех уровнях.

15 Регистры управления * DE — расширение отладки (Debugging Extensions, Pentium+). Расширение отладки позволяет использовать регистры DR 4 и DR 5 для установки контрольных точек по портам ввода-вывода. * PSE — расширение размера страниц (Page Size Extension, Pentium+). Расширение размера страницы позволяет в страничном преобразовании использовать страницы размером 4 Мбайт (или 2 Мбайт, если PAE=1). * PAE — расширение физического адреса (Physical Addres Extension, P 6+). Расширение физического адреса позволяет в результате страничной трансляции генерировать 36 -битные физические адреса. * MCE — разрешение машинного контроля (Machine Check Enable, Pentium+). Разрешает особый случай машинного контроля (исключение #18), возникающий, когда блок внутреннего контроля операций внутри чипа или на шине обнаруживает ошибку. * PGE — разрешение атрибута глобальности (Page Global Enable, P 6+). Разрешает использование бита глобальности в элементах PDE/PTE. Это расширение позволяет часто используемые или разделяемые (shared) страницы пометить как «глобальные». Глобальные страницы не выгружаются из TLB при переключении задачи.

15 Регистры управления * DE — расширение отладки (Debugging Extensions, Pentium+). Расширение отладки позволяет использовать регистры DR 4 и DR 5 для установки контрольных точек по портам ввода-вывода. * PSE — расширение размера страниц (Page Size Extension, Pentium+). Расширение размера страницы позволяет в страничном преобразовании использовать страницы размером 4 Мбайт (или 2 Мбайт, если PAE=1). * PAE — расширение физического адреса (Physical Addres Extension, P 6+). Расширение физического адреса позволяет в результате страничной трансляции генерировать 36 -битные физические адреса. * MCE — разрешение машинного контроля (Machine Check Enable, Pentium+). Разрешает особый случай машинного контроля (исключение #18), возникающий, когда блок внутреннего контроля операций внутри чипа или на шине обнаруживает ошибку. * PGE — разрешение атрибута глобальности (Page Global Enable, P 6+). Разрешает использование бита глобальности в элементах PDE/PTE. Это расширение позволяет часто используемые или разделяемые (shared) страницы пометить как «глобальные». Глобальные страницы не выгружаются из TLB при переключении задачи.

16 Регистры управления * PCE — разрешение счетчика производительности (Performance-monitoring Counter Enable, P 6+). Когда PCE=1, выполнение инструкции RDPMC (чтение внутреннего счетчика производительности) разрешено на всех уровнях привилегий, иначе инструкция будет выполняться только на нулевом уровне привилегий. * OSFXSR — поддержка операционной системой FXSAVE/FXRESTOR (OS support for FXSAVE/FXRESTOR instructions, Pentium II+). Разрешает командам FXSAVE/FXRESTOR, сохраняющим/восстанавливающим контекст сопроцессора, сохранять/восстанавливать контекст XMM. * OSXMMEXCPT — поддержка операционной системой особых случаев XMM (OS support for XMM Exception, Pentium III+). Разрешает генерацию исключения #19 (ошибка SIMD), в противном случае немаскированные ошибки SIMD будут генерировать особый случай «недействительный код операции» (исключение #6).

16 Регистры управления * PCE — разрешение счетчика производительности (Performance-monitoring Counter Enable, P 6+). Когда PCE=1, выполнение инструкции RDPMC (чтение внутреннего счетчика производительности) разрешено на всех уровнях привилегий, иначе инструкция будет выполняться только на нулевом уровне привилегий. * OSFXSR — поддержка операционной системой FXSAVE/FXRESTOR (OS support for FXSAVE/FXRESTOR instructions, Pentium II+). Разрешает командам FXSAVE/FXRESTOR, сохраняющим/восстанавливающим контекст сопроцессора, сохранять/восстанавливать контекст XMM. * OSXMMEXCPT — поддержка операционной системой особых случаев XMM (OS support for XMM Exception, Pentium III+). Разрешает генерацию исключения #19 (ошибка SIMD), в противном случае немаскированные ошибки SIMD будут генерировать особый случай «недействительный код операции» (исключение #6).

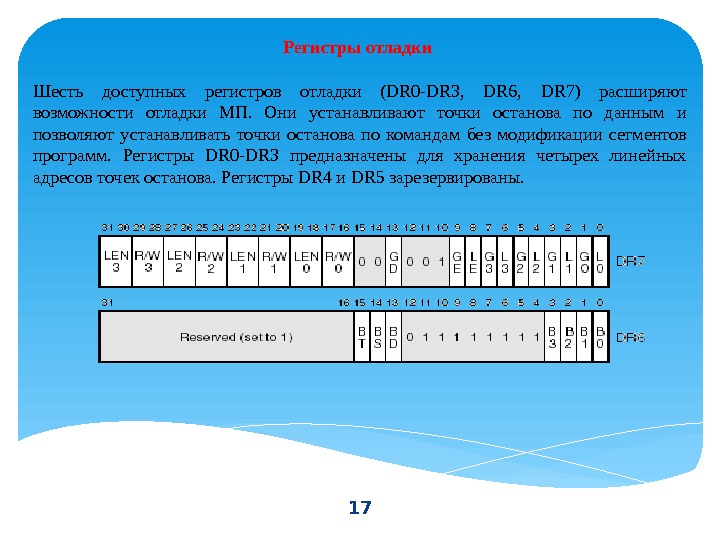

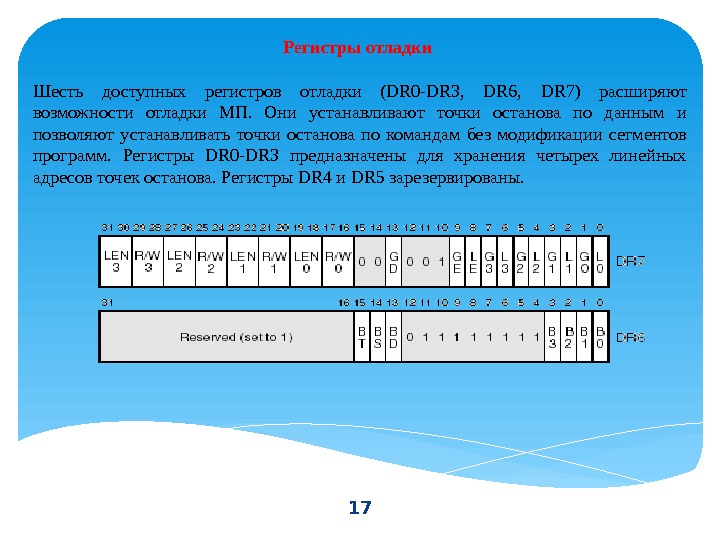

17 Регистры отладки Шесть доступных регистров отладки (DR 0 -DR 3, DR 6, DR 7) расширяют возможности отладки МП. Они устанавливают точки останова по данным и позволяют устанавливать точки останова по командам без модификации сегментов программ. Регистры DR 0 -DR 3 предназначены для хранения четырех линейных адресов точек останова. Регистры DR 4 и DR 5 зарезервированы.

17 Регистры отладки Шесть доступных регистров отладки (DR 0 -DR 3, DR 6, DR 7) расширяют возможности отладки МП. Они устанавливают точки останова по данным и позволяют устанавливать точки останова по командам без модификации сегментов программ. Регистры DR 0 -DR 3 предназначены для хранения четырех линейных адресов точек останова. Регистры DR 4 и DR 5 зарезервированы.

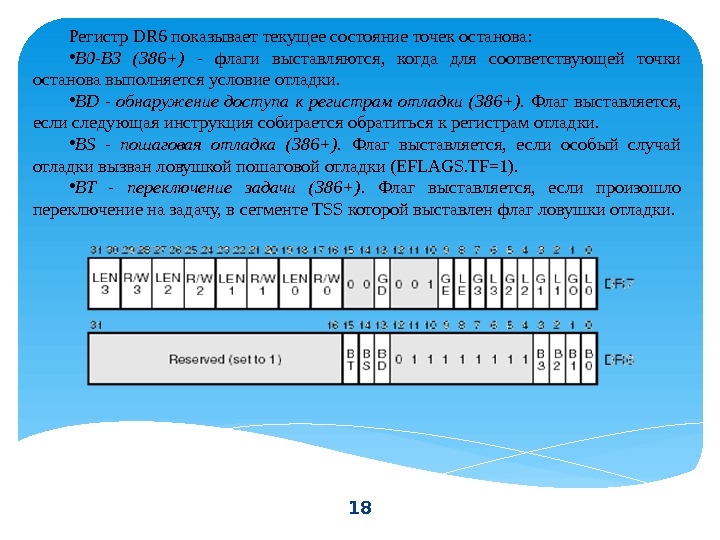

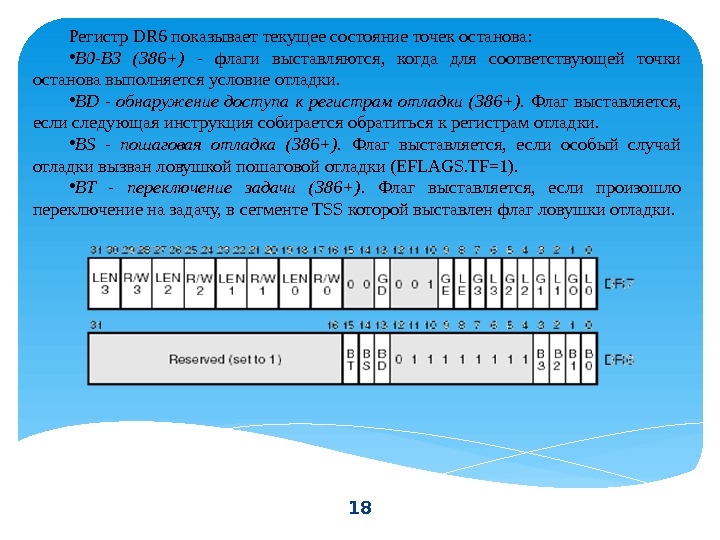

18 Регистр DR 6 показывает текущее состояние точек останова: • B 0 -B 3 (386+) — флаги выставляются, когда для соответствующей точки останова выполняется условие отладки. • BD — обнаружение доступа к регистрам отладки (386+). Флаг выставляется, если следующая инструкция собирается обратиться к регистрам отладки. • BS — пошаговая отладка (386+). Флаг выставляется, если особый случай отладки вызван ловушкой пошаговой отладки (EFLAGS. TF=1). • BT — переключение задачи (386+). Флаг выставляется, если произошло переключение на задачу, в сегменте TSS которой выставлен флаг ловушки отладки.

18 Регистр DR 6 показывает текущее состояние точек останова: • B 0 -B 3 (386+) — флаги выставляются, когда для соответствующей точки останова выполняется условие отладки. • BD — обнаружение доступа к регистрам отладки (386+). Флаг выставляется, если следующая инструкция собирается обратиться к регистрам отладки. • BS — пошаговая отладка (386+). Флаг выставляется, если особый случай отладки вызван ловушкой пошаговой отладки (EFLAGS. TF=1). • BT — переключение задачи (386+). Флаг выставляется, если произошло переключение на задачу, в сегменте TSS которой выставлен флаг ловушки отладки.

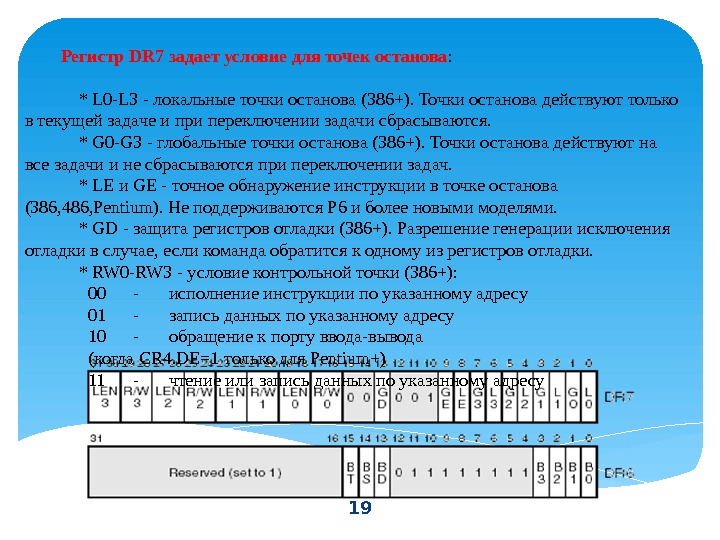

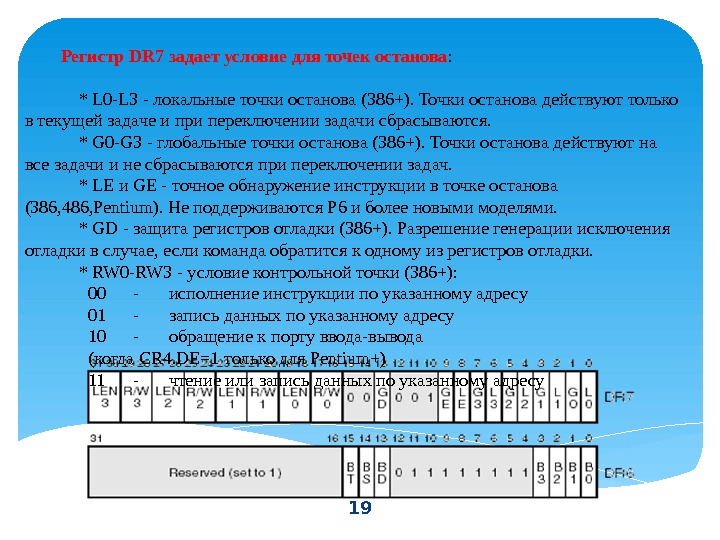

19 Регистр DR 7 задает условие для точек останова : * L 0 -L 3 — локальные точки останова (386+). Точки останова действуют только в текущей задаче и при переключении задачи сбрасываются. * G 0 -G 3 — глобальные точки останова (386+). Точки останова действуют на все задачи и не сбрасываются при переключении задач. * LE и GE — точное обнаружение инструкции в точке останова (386, 486, Pentium). Не поддерживаются P 6 и более новыми моделями. * GD — защита регистров отладки (386+). Разрешение генерации исключения отладки в случае, если команда обратится к одному из регистров отладки. * RW 0 -RW 3 — условие контрольной точки (386+): 00 — исполнение инструкции по указанному адресу 01 — запись данных по указанному адресу 10 — обращение к порту ввода-вывода (когда CR 4. DE=1 только для Pentium+) 11 — чтение или запись данных по указанному адресу

19 Регистр DR 7 задает условие для точек останова : * L 0 -L 3 — локальные точки останова (386+). Точки останова действуют только в текущей задаче и при переключении задачи сбрасываются. * G 0 -G 3 — глобальные точки останова (386+). Точки останова действуют на все задачи и не сбрасываются при переключении задач. * LE и GE — точное обнаружение инструкции в точке останова (386, 486, Pentium). Не поддерживаются P 6 и более новыми моделями. * GD — защита регистров отладки (386+). Разрешение генерации исключения отладки в случае, если команда обратится к одному из регистров отладки. * RW 0 -RW 3 — условие контрольной точки (386+): 00 — исполнение инструкции по указанному адресу 01 — запись данных по указанному адресу 10 — обращение к порту ввода-вывода (когда CR 4. DE=1 только для Pentium+) 11 — чтение или запись данных по указанному адресу

20 LEN 0 -LEN 3 (386+) — длина контрольной точки для обращения к данным (если RWx=00, то LENx тоже должно быть 00): 00 — 1 байт 01 — 2 байта 10 — резерв. 11 — 4 байта

20 LEN 0 -LEN 3 (386+) — длина контрольной точки для обращения к данным (если RWx=00, то LENx тоже должно быть 00): 00 — 1 байт 01 — 2 байта 10 — резерв. 11 — 4 байта